面向CMOS图像传感器芯片的3D 芯粒(Chiplet) 非接触互联技术

2023-10-17徐志航徐永烨马同川

徐志航 徐永烨 马同川 杜 力 杜 源

(南京大学电子科学与工程学院 南京 210023)

1 引言

CMOS图像传感器(CMOS Image Sensor, CIS)因具有高集成度、低功耗以及低成本的优点而被广泛应用于智能驾驶、医疗影像、安防等领域[1]。目前,为了满足高分辨率和高帧率的性能需求,CIS芯片和数字芯片之间的数据吞吐量需要不断提升。然而,由于阻抗不连续,金属的趋肤效应以及介质损耗等问题,芯片间2维互联中的高速信号传输速度受到限制且能效较低[2,3]。在应对这些挑战的先进芯片集成技术中,3D Chiplet技术是一种有效且可行的解决方案[4,5]。该技术通过将多个不同工艺节点的芯粒在垂直方向上封装成一个异构集成芯片,具有可扩展性和低成本的优势,并且提高芯粒间的通信速度和整体芯片能效,在集成电路领域得到了广泛的关注和应用[6–11]。

传统的3D Chiplet 技术使用硅通孔(Through Silicon Via, TSV)进行异构芯片的集成[12],具有集成密度高和泛用性高的优点。但是由于其工艺步骤复杂、对生产设备要求高,导致封装良品率低、成本高[13–15]。而非接触式3D Chiplet可以解决这些问题,文献[16]首先提出了电感耦合的芯片间通信(Inductive Inter-chip Signaling, IIS)技术,使所有垂直堆叠的芯片无需硅通孔工艺即可实现互联。因为该技术对封装工艺要求较低,所以封装的成本较低。此外,相较于常见的电容耦合互联方式,电感耦合互联的信道衰减仅受限于电流大小,不会直接受限于电源电压[17]。但由于耦合电感的耦合系数随通信距离的提升衰减较大,通常应用于芯片间的短距通信[18]。

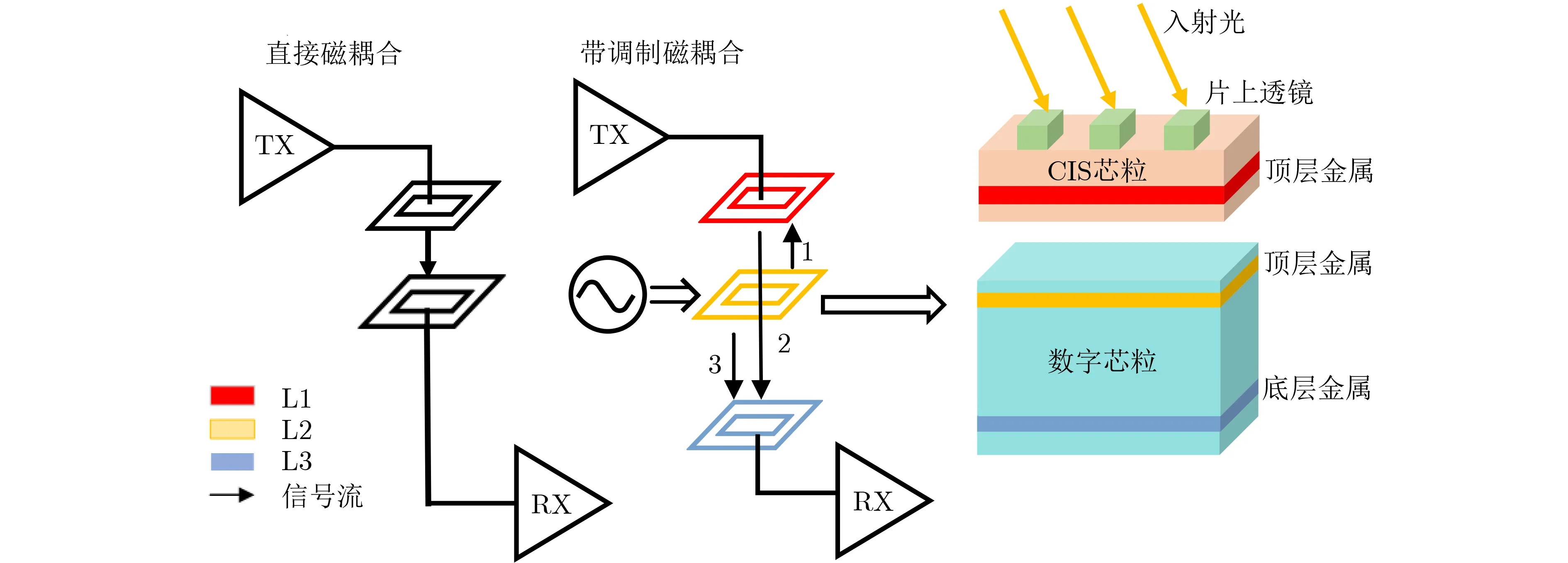

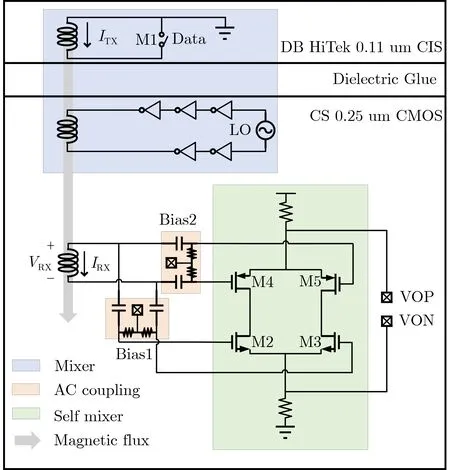

如图1所示,为了解决传统的前照式CIS工艺中芯片金属层阻挡入射光线的问题,业界广泛采用背照式CIS工艺翻转晶圆来消除金属干扰[19,20]。当背照式工艺的CIS芯粒和数字芯粒进行3D异构集成时,CIS芯粒的顶层金属邻近数字芯粒的顶层金属,非常适合电感耦合互联来实现短距通信。

图1 面向CIS芯粒与数字芯粒间互联的3D Chiplet 非接触高速互联

本文受到文献[21]所提出的技术的启发,提出了一种新型面向CIS的3D Chiplet非接触互联技术,基于电感耦合构建了数据源、载波源和接收机3层分布式收发机结构。首先,与目前3D Chiplet主流的硅通孔互联方式相比具有低工艺复杂度和低成本的优点。其次,载波调制的互联方式对比数据直传可以更有效地利用带宽实现多通道通信。最后,所提出的互联技术中载波源脱离CIS芯粒而被放置在数据源下层,降低了载波源对低频信号的干扰。本文以电感耦合调制结构与带自混频解调的高速收发电路为实验模型,通过仿真和实际芯片测试来验证该互联系统可行性和有效性,并统计系统接收端的误码率和能效。

2 3D Chiplet 非接触互联系统设计

2.1 分布式收发机结构调制原理

该设计是一种针对CIS芯粒和数字芯粒的3D Chiplet非接触互联系统。如图1所示,该系统由3层电感组成,顶层红色电感(下称L1)位于CIS芯粒中,用于信号调制。中层黄色电感(下称L2)和底层蓝色电感(下称L3)位于数字芯粒中,分别用于发送本振信号和接收已调信号。

图1中的信号流1表示L2对L1的辐射,信号流2表示L1对L3的直接辐射,信号流3表示L2对L3的辐射。假设不考虑电荷注入效应和时钟馈通效应,因为L1所在回路中不存在有源器件,所以开关在切换开闭状态时,回路中不存在瞬态电流,但回路的阻抗会随开关状态变化。信号流1会在L1回路中产生感应电流,回路的阻抗会影响该电流的幅度。由于感应电流的磁场总会阻碍引起感应电流的磁通量的变化,所以无论L1回路的开关状态如何,L1的感应电流的磁场都会阻碍L2在L3处产生的磁通量变化,但在回路闭合时阻碍更强。因此,L1开关的状态就映射到了L3回路的磁通量变化率上,实现了通断键控(On-Off Keying, OOK)。另外,会存在L1先耦合至L2再耦合到L3的情况,需要说明的是:(1)L3回路的感应电动势和L1, L2在L3回路处产生的磁通量变化的速率成正比。(2)L1到L2的耦合使得L2的感应电流的磁场在L3回路处阻碍L1磁通量的变化,这使得L1到L3的耦合变弱。综上,由于L1到L2的耦合属于次级耦合,其在调制机制中是一种非理想因素,在涉及这种情况的电磁仿真中,OOK的调制功能仍然成立,为了调制机制描述的简洁性,该分析忽略了信号的次级耦合是合理的。

2.2 耦合电感建模与分析

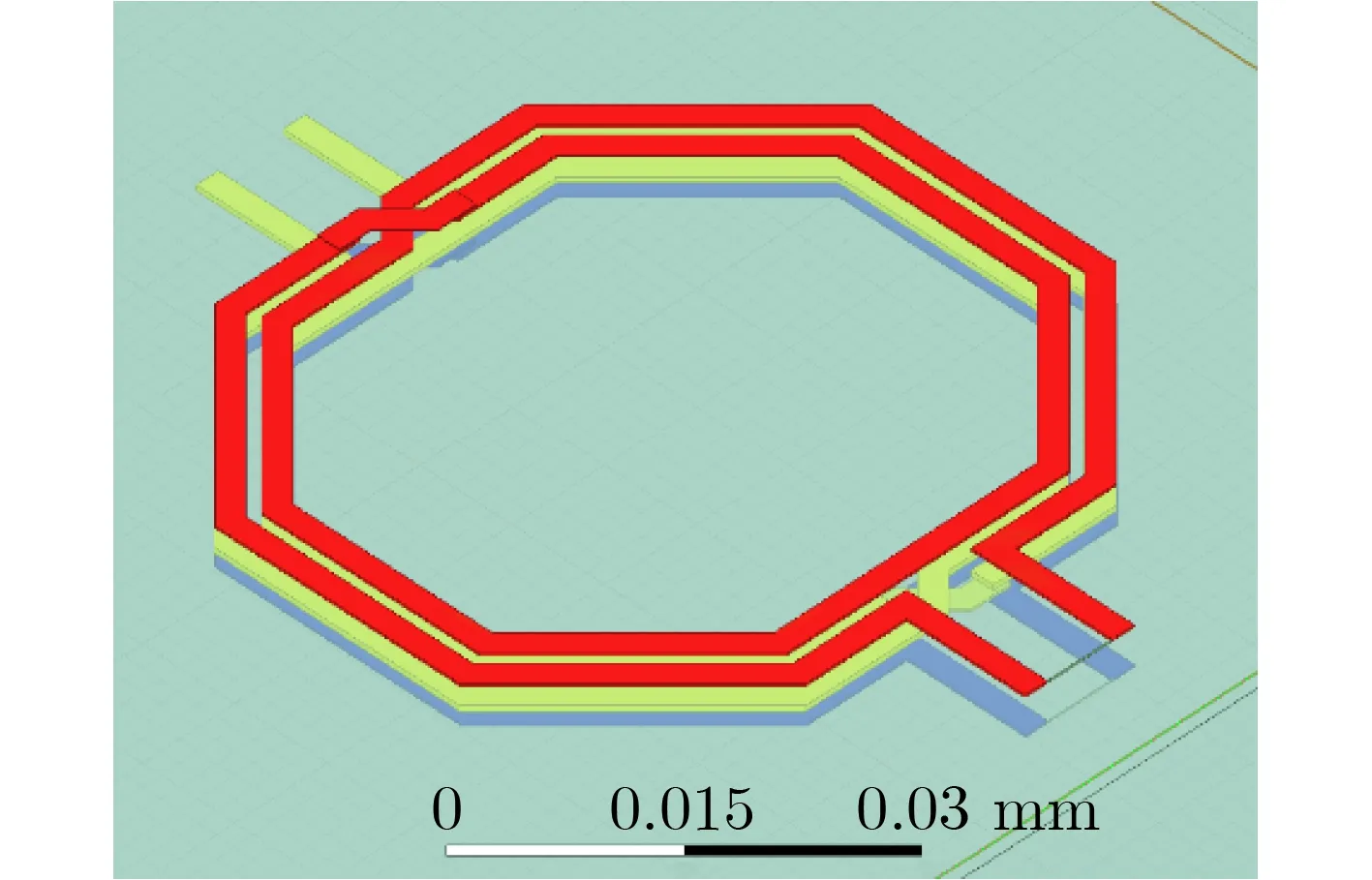

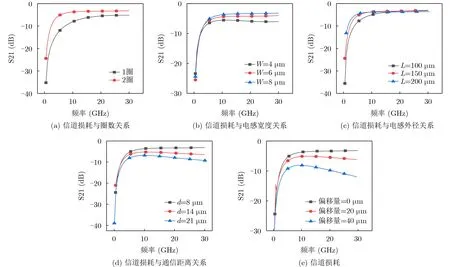

通过对所提出的3D Chiplet 非接触链路系统发射端的分析,得出了发射端实现OOK调制的结论。为尽可能减小发射端的信号衰减,得到增益较高的耦合电感设计,在HFSS中进行了建模。如图2所示,从上到下堆叠了0.11 μm CIS工艺和0.25 μm CMOS工艺的介质层,介质中的红色线圈为L1,黄色线圈为L2,蓝色线圈为L3。在优化信道损耗时,需要考虑圈数、宽度、外径以及两颗芯片之间的垂直、水平距离,分别以它们为单变量在0~30 GHz范围内仿真了L1到L3的信道损耗(本文使用S21表征信道损耗),图3为仿真结果。

图2 HFSS耦合电感的电磁仿真建模

图3 信道损耗的影响因素

图3(a)为不同电感圈数对信道损耗的影响,互感系数随着圈数的增加而提升,信道损耗也相应降低。2圈的耦合电感在10~30 GHz范围内展现出4 dB左右的损耗。图3(b)展示了电感宽度对信道损耗的影响,宽度的增加会降低信道的高频损耗。图3(c)展示了外径对信道损耗的影响,降低外径可以提升信道密度,但会显著提升信道的低频损耗。根据图3(d),随着通信距离的增加,互感系数降低,因而信道损耗提升。这时,需要提升发射端的输入功率,以维持接收端的信号质量[22]。根据图3(e),当水平偏移量为20 μm时,信道损耗提升了3 dB;当水平偏移量为40 μm时,信道损耗提升超过5 dB。这表明3D封装的对准误差会使信道产生一定的信号衰减。

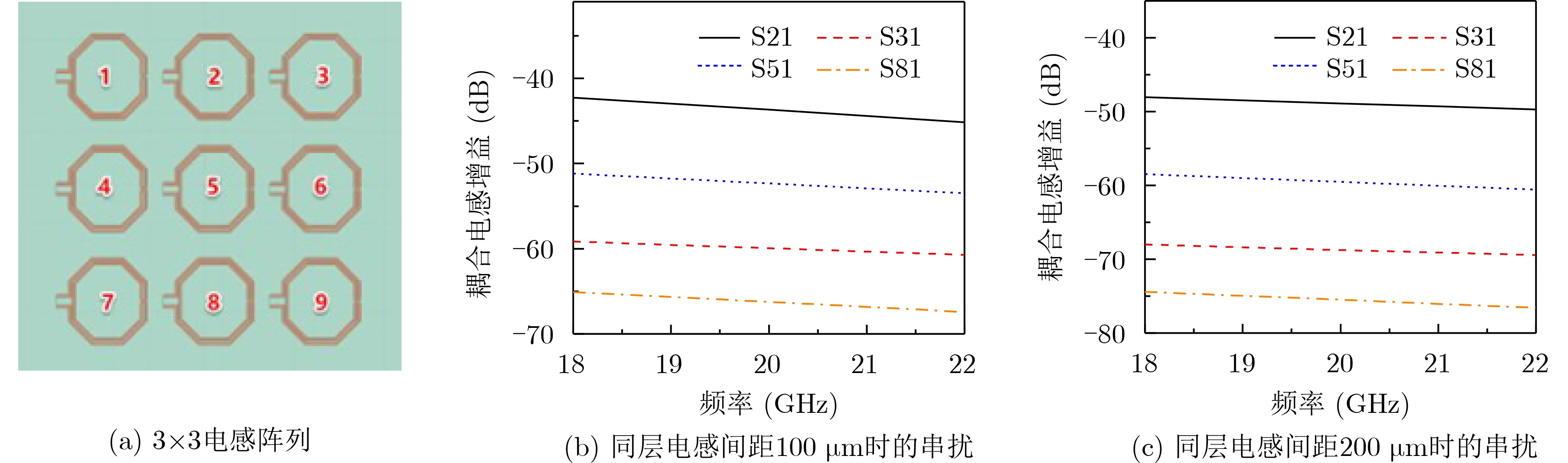

考虑电感阵列中因同层电感的耦合产生的串扰,在 HFSS中建模了一个如图4(a)所示的3×3的电感阵列,其中9个电感位于同一层,每一个电感外径为200 μm。根据图3(d),在通信距离为21 μm时,两垂直电感在20 GHz处信道损耗为7.98 dB。图4(b)、图4(c)展示了阵列中不同间距的同层电感之间的耦合电感增益,在同一层内,相邻两电感的间距为100 μm时,最近两电感的耦合电感增益在20 GHz处为–42.3 dB;相邻两电感的间距为200 μm时,最近两电感的耦合电感增益在20 GHz处为–48.9 dB。因此,同层电感之间的串扰处于可以接受的范围。为了提升带宽的利用率,若使用4电平脉冲幅度调制(4 level Pulse Amplitude Modulation, PAM4),为了得到同样的误码率,相比于OOK需要更高的信噪比,这对串扰的抑制提出了更高的要求。

图4 同层电感阵列串扰分析

为此可以采用降低整体数据速率来换取更好的通信质量的策略,将1, 3, 5, 7, 9和2, 4, 6, 8处的信道分为两组进行时分复用,对比S51和S21可知串扰会下降8.92 dB。另外,如果电感周围增加屏蔽层设计,可以进一步降低串扰,但需要更多的芯片面积。

2.3 高速收发电路设计

图5是所设计的高速收发电路结构,发射端电路由CIS芯粒中的开关电路和数字芯粒中的本振信号驱动电路两个模块组成。通过切换开关开闭状态,可以改变回路阻抗进而调节L1感应电流的幅值。在频率较低时,如果不考虑寄生电容带来的影响,M1宽长比越大,则电流开关比越大。在频率较高时,若M1开关断开,交流电流通过M1的寄生电容CDB和L1;若M1开关闭合,交流电流通过M1的导通电阻RON和L1。无论哪种情况,提升M1的宽长比,回路的阻抗幅值都会降低,这说明在频率较高时,需要选择合适的开关尺寸来最大化感应电流的开关比。本振信号的电流驱动电路位于数字芯粒中,在芯片测试中,本振信号源由芯片外部供给。

图5 3D Chiplet 非接触链路系统结构

为了实现信号解调,接收端电路采用了自混频电路进行异步数据恢复。该自混频电路的M2~M5均需要偏置到亚阈值区。当电路接收已调信号时,假设M2栅压低于共模电平而M3栅压高于共模电平,则M2趋向于截止区而M3趋向于线性区。反之则M2趋向于线性区,M3趋向于截止区。M2和M3在载波频率对应的1个周期T内总有1个处于开启状态。同样地,M4和M5在周期T内也交替开启。因为M2和M5以及M3和M4的输入信号也都互为差分,自混频电路的电阻上在周期T内始终有电流通过,所以该电路可以将已调信号中的包络提取到电阻的电流上进行输出。通过设置合适的偏置电压,可以优化自混频输出的开关比。以NMOS差分对为例,若偏置电压过低,会使得晶体管不能动态导通;反之,则会使得晶体管不能动态关闭。因此,偏置电压过低或过高都会导致输出摆幅降低。此外,工艺制造误差可能导致晶体管阈值电压的浮动。综合以上考虑,自混频电路的偏置在芯片测试中是可调的。解调完成后,信号将被送入后续的电路中进行处理。

3 系统仿真和芯片测试

为了验证系统的可行性,本文基于Cadence Virtuoso软件进行了系统仿真和性能测试。将通过HFSS仿真得到的耦合电感信道的S参数模型导入到Virtuoso。同时,加入需要的两种工艺模型库进行联合仿真。

基带数据速率设为200 Mbit/s,载波频率设为20 GHz。为了尽量减小信道占用面积,且不影响信道在载波频率附近的损耗,电感尺寸选择为W=8 μm,L= 200 μm,圈数为2圈,通信距离设置为8 μm。

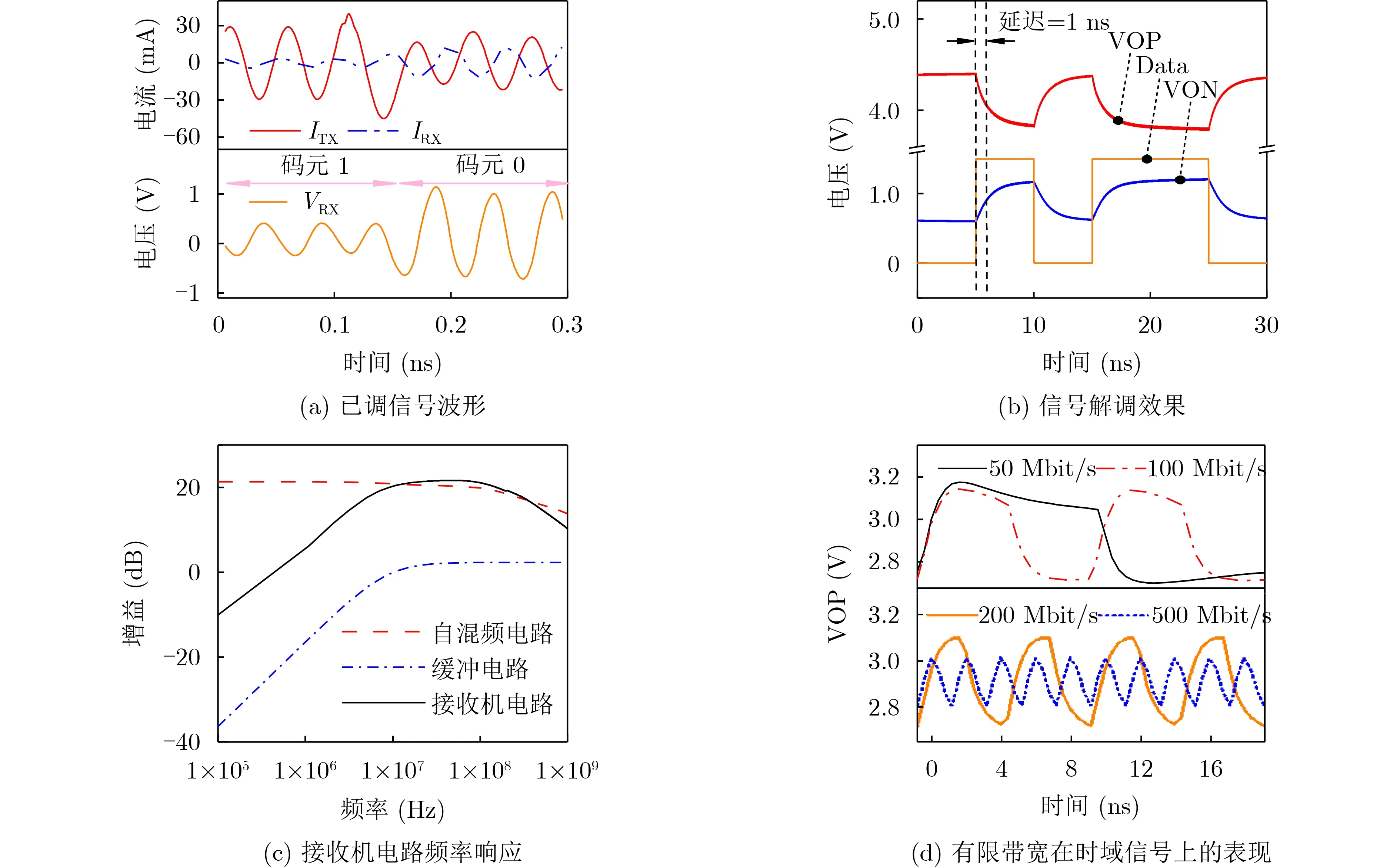

图6显示了电路不同节点的时域仿真结果。其中图6(a)展示了码元状态从1转换至0时, L1 的电流 ITX,L3的电流IRX和其两端电压VRX的时域波形。L1回路开关导通时ITX稳定幅值约为30 mA,回路开关断开时ITX稳定幅值约为20 mA,电流开关比约为3:2。在开关导通时,L1感应电流的磁场对L2在L3回路处产生的磁通量变化阻碍更强,流过L3的电流IRX和其两端电压VRX变小,反之则变大。L1回路开关导通时 IRX稳定幅值约为4 mA,回路开关断开时IRX稳定幅值约为12 mA,接收端电流开关比约为1:3,接收端电压开关比约为1:2。图6(b)显示,经过自混频解调的差分信号VOP与VON,单端幅值约为0.45 V,差分幅值约为0.9 V,发射到接收端的延迟为1 ns。

图6 联合仿真时域结果

如图6(d)所示,解调后的波形趋向于三角波,这是系统带宽不足导致的。现对系统带宽进行仿真与分析,由于自混频电路存在不同频率信号的转换,在Virtuoso环境中需要使用PSS和PAC仿真求解其频率响应。如图6(c)所示,自混频电路的频率响应为低通,后续缓冲电路由于使用AC耦合,频率响应为高通,进而接收机芯片的频率响应为带通,其–3 dB带宽对应的频率范围为6.3~251.2 MHz。

通过仿真还可以评估系统的噪声条件,信号衰减程度以及期望的输出信噪比。其中,接收机芯片的噪声基底(Noise Floor)的估计为

式(1)中噪声积分的带宽BW为20 GHz,噪声系数NF定义为式(2)。式(2)中:Si和Ni分别表示输入信号和输入噪声;So和No分别表示输出信号和输出噪声;G表示接收机增益;N表示接收机贡献的输出噪声。根据式(2),接收机噪声系数NF定义为等效输入噪声积分的功率与源阻抗贡献的噪声积分的功率之比加1,通过PSS和PNOISE仿真可以 得到为10.93 dB。因此噪声基底为–60.06 dBm,接收机芯片在200 MHz处信号衰减程度通过PSS和PAC仿真得到为–14.52 dB。而对于一个加性高斯白噪声(Additive White Gaussian Noise, AWGN)信道,为保证误码率低于10–8,最小信噪比为21 dB,由此计算出发射端最小输出功率为–24.54 dBm。

在搭建该接收机的CSMC 0.25 μm工艺平台上进行了实际芯片验证与性能测试。图7为芯片测试环境和芯片引线键合的显微照片,图8是测试平台与眼图。信号发生器生成20 GHz的载波,OOK调制的码元速率为200 Mbaud/s。测试结果表明,该以20 GHz为中心频率的收发机在通信距离为8 μm的情况下,数据速率达到200 Mbit/s,误码率小于10–8,接收端功耗为1.09 mW,能效为5.45 pJ/bit。

图7 测试环境和芯片引线键合的显微照片

4 结束语

本文介绍了一种面向CIS的3D Chiplet非接触互联技术,该技术使所有垂直堆叠的芯片无需通孔即可实现互联,解决了传统封装中TSV工艺步骤复杂、成本高和良品率低的问题。基于电感耦合,本文构建了数据源、载波源和接收机3层分布式收发机结构,非常适合背照式CIS的倒置封装结构。带载波的磁耦合与没有载波的基带直接磁耦合相比,将信号搬移至更高频段从而适应信道的高通特性,并且可以有效地利用带宽实现多通道通信。芯片的仿真和测试结果验证了该面向CIS的芯片间互联技术的有效性。在未来的研究中可以设计耦合电感阵列的3D Chiplet非接触互联,以进一步提升互联密度和频带利用率。