基于ADP1071-2的高效率超薄反激变换器

2023-10-05任永宏杨利军黄烨琳

任永宏,纪 飞,杨利军,黄烨琳

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

反激变换器由于电路拓扑结构简单、副边无滤波电感、体积小、成本低等优点,在小功率隔离电路中被广泛应用[1]。传统反激变换器多采用基于Si 材料的功率器件和绕线式变压器来实现,但是Si 材料在高频下较大的开关损耗限制了变换器工作频率的提高,限制电源高功率密度的实现;绕线式变压器由于体积大、漏感大,会增大主功率管的电压应力,降低反激变换器的转换效率,同时也会增加系统散热设计的难度。

GaN 晶体管作为第三代半导体器件的典型代表,具有禁带宽度大、电子迁移率高、临界击穿电场高、饱和电子速度高、介电常数小等优点[2-4]。这些优点使GaN 器件在相同电压应力下与Si 器件相比,具有更小的栅极寄生电容、更低的导通电阻,因此其开关速度更快、驱动和开关损耗更低,有助于提高变换器的转换效率及功率密度。

磁性元器件的体积和质量在开关电源中占据相当大的比例,因此减小其体积成为提高变换器功率密度的一种关键方法[5]。印制电路板平面变压器以PCB 绕组代替传统导线绕组而实现平面结构,省去了传统变压器的骨架,可以降低变压器的高度。此外,平面变压器减少了高频时由集肤效应和邻近效应产生的涡流损耗,可增大PCB 绕组的电流密度,提高变压器的功率密度[6-9]。

本文采用ADP1071-2 控制芯片,应用PCB 平面变压器和GaN 晶体管,设计了一台3.3 V/10 A 的高效率超薄反激变换器。以实验样机为例,详细分析了主电路参数的设计方法,给出选型依据和计算公式,可作为工程应用参考。

1 反激变换器设计方案

ADP1071-2 是由美国ADI 公司推出的一款集成了同步整流功能的电流模式反激控制器,其内部集成了两路ADI 公司的专有iCoupler 隔离器,一路隔离器用来将副边产生的电压环路补偿信号传输到原边,另一路用来将原边产生的同步整流驱动信号传输到副边。两路隔离器取代了传统隔离电源中常用的光耦器件和隔离驱动变压器,降低了系统设计的复杂性和成本,减少了元器件数量,并提高了系统的可靠性和功率密度。

该芯片工作电压范围4.7~60 V,可调频率范围50~600 kHz。内部集成了1 A 的原边和副边驱动器,且原、副边驱动信号留有固定的死区时间,能够满足一般反激变换器的设计需求。除此之外,还具有可调斜坡补偿、软启动、最大占空比限制、输入欠压保护、输出过压保护、逐周期限流保护、频率同步和过温保护等功能。

基于ADP1071-2 控制的反激变换器电路如图1 所示。输出电压经过采样电路后送到芯片副边FB 引脚,经过内部运算放大器比较产生误差放大信号,再通过芯片内部隔离器送到原边,作为内部PWM 比较器的反向输入端,与正向输入端的经过斜坡补偿的原边电流采样信号进行比较,获得PWM驱动信号,控制原边功率管和副边同步整流管的导通和关断,从而实现输出电压的调节。

图1 基于ADP1071-2控制的反激变换器电路图

2 高效率超薄反激变换器参数设计

2.1 变换器关键参数要求

变换器输入电压范围15~50 V(DC),额定输入电压28 V,额定输出电压Vo=3.3 V,满载输出电流Io=10 A,开关频率fs取500 kHz。

反激变换器根据变压器磁通是否连续分为断续工作模式(DCM)和连续工作模式(CCM)。当输出功率相同时,CCM模式下原边和副边的电感电流峰值和有效值更小,功率管的损耗也更小,因此本文设计的反激变换器工作于CCM 模式。

2.2 平面变压器设计

2.2.1 确定匝比和原边感量

最低输入电压Vin_min=15 V 时,对应最大占空比Dmax取0.57,由反激变换器CCM 模式下输入输出电压关系计算出变压器原边与副边的匝比n为:

变压器的初级电感Lm为:

式中:Pin_max为最大输入功率;KRF为电感电流纹波系数,此设计取KRF=0.32。

对应初级电感的电流纹波ΔI和电流峰值Ipk分别为:

2.2.2 计算匝数和气隙

根据AP 法选取TDK 公司的平面磁芯PC95ER14/4.5/9,磁芯材料为PC95,磁芯高度约4.5 mm,其有效磁芯截面积Ae为22.7 mm2,磁路长度le为15.4 mm,100 ℃时饱和磁密Bs为0.41 T。

选取磁芯最高工作磁密Bm=0.26 T,则变压器原边匝数Np为:

原边匝数取整为Np=6,根据变压器匝比n计算出副边匝数Ns=1。

反激变压器需要增加气隙以提高磁芯的能量储存能力,其所需气隙长度δ为:

2.2.3 PCB 绕组设计

变压器原边和副边绕组的电流有效值Ip_rms和Is_rms分别为:

取PCB 绕组的电流密度J=30 A/mm2,设计PCB 绕组的铜厚h0=0.07 mm(2 盎司)。

对于原边绕组,根据所选磁芯的窗口宽度,考虑每层PCB 绕3 匝,取线径dp=0.8 mm,则原边绕组所需层数为:

对于副边绕组,考虑每层PCB 绕1 匝,取线径ds=2.6 mm,则副边绕组所需层数为:

为了保证绕组结构的对称性,原边和副边绕组层数各取4 层,此外原边和副边的辅助绕组各取1 层,共10 层PCB。相同绕组不同层间使用过孔进行连接,且采用交错排布方式进行绕制以减小变压器的交流等效电阻和漏感[6-9],从而减少变压器的绕组损耗,减小由漏感造成功率管关断瞬间的电压尖峰,缓减吸收电路压力,提高变换器的效率。

由于设计的PCB 绕组宽度略小于磁芯窗口宽度(2.95 mm),因此只需保证PCB 绕组厚度小于窗口高度即可。已知磁芯窗口高度1.7 mm,选取PCB 绕组的板厚为1.5 mm,满足设计要求。

2.3 原副边功率管选型

2.3.1 原边功率管

反激变换器在原边功率管关断瞬间,由变压器漏感与功率管输出电容谐振造成的电压尖峰加在原边功率管的漏极,为此需增加钳位电路来吸收电压尖峰。通常设计钳位电压Vclamp为2~3 倍的副边反射电压[10],此处取2.5 倍,对应原边功率管所承受的电压应力为:

工作于CCM 模式的高频反激变换器,原边功率管存在硬开关,其关键损耗为开关损耗、导通损耗和驱动损耗。GaN晶体管由于栅极电荷小、开关速度快、导通电阻低,非常适用于此应用场合。根据以上分析,本文选取的GaN 晶体管型号为EPC 公司的EPC2034,其漏源击穿电压VDS_max为200 V,通态电流ID为48 A,导通电阻RDS(on)为10 mΩ,门极电荷QG为8.8 nC,密勒平台电荷QGD为1.8 nC。

EPC2034 采用球阵列封装(BGA 4.6×2.6),如图2 所示,其源极S 和漏极D 交错分布,器件尺寸非常小,可以最大限度地减小引线电阻和寄生电容,有利于提高工作频率,提高系统功率密度。在实际应用中,栅极驱动器的合理设计和布局对于GaN 晶体管的性能发挥和可靠工作起着至关重要的作用,驱动器与GaN 晶体管之间的布局应当尽可能地紧凑,尽量减小驱动回路的寄生电感,同时合理设置驱动电阻,以减小过高dv/dt和di/dt给器件带来的不利影响,确保GaN 晶体管可靠地开通和关断[11-12]。

图2 EPC2034封装图

2.3.2 副边同步整流管

为了提高反激变换器效率,ADP1071-2 芯片内部集成了副边同步整流功能,其驱动信号与原边功率管驱动互补,且留有固定的死区时间(原、副边驱动信号前沿死区时间约30 ns,后沿死区时间约52 ns)。

考虑到同步整流管的关键损耗为导通损耗,且由于死区时间固定不可调,因此在选型时除了关注较低的导通电阻外,还需重点考虑选择栅极驱动电荷较低的MOS 管,保证驱动速度足够快以防止原、副边功率管共通。

副边同步整流管所承受的电压应力为:

根据以上分析,本文选取的副边同步整流管型号为英飞凌公司的BSC015NE2LS5I。

2.4 输出滤波电容设计

输出滤波电容的容值大小由允许的输出电压纹波来决定,而输出电压纹波通常由开关过程中电容的充放电和其等效串联电阻(ESR)的压降两部分构成,其计算公式为:

此外,输出滤波电容通过的纹波电流有效值Ic_rms为:

若取输出电压纹波为输出电压的1%,即ΔVo=33 mV,根据公式(11)、(12),样机中输出滤波电容采用10 颗47 μF/16 V的陶瓷电容并联使用。

3 实验结果分析

根据上述理论分析和主电路参数设计方法,研制了一台33 W 的高效率超薄反激变换器,实验样机尺寸为45 mm ×30 mm×6 mm,质量约18 g,如图3 所示。

图3 反激变换器实验样机

图4 为最低输入电压15 V、满载10 A 输出时原边功率管和副边同步整流管的驱动电压波形vGS_p、vGS_s。从波形中可以看出原、副边驱动的前沿死区时间约10 ns,后沿死区时间约40 ns(由于功率管的开关延时,其死区时间会低于ADP1071-2芯片设定的死区时间)。波形中测量vGS_p的占空比为57%,与理论设计结果一致。

图4 原边功率管和副边同步整流管的驱动电压波形

图5 所示为最高输入电压50 V、满载10 A 输出时原边功率管和副边同步整流管的漏源极电压波形vDS_p、vDS_s。波形中测 量vDS_p、vDS_s的电压峰值VDS_p_max、VDS_s_max分别为108、19.5 V,满足钳位吸收电路设计结果和器件电压应力降额,验证了器件选型和设计方法的正确性。

图5 原边功率管和副边同步整流管的漏源极电压波形

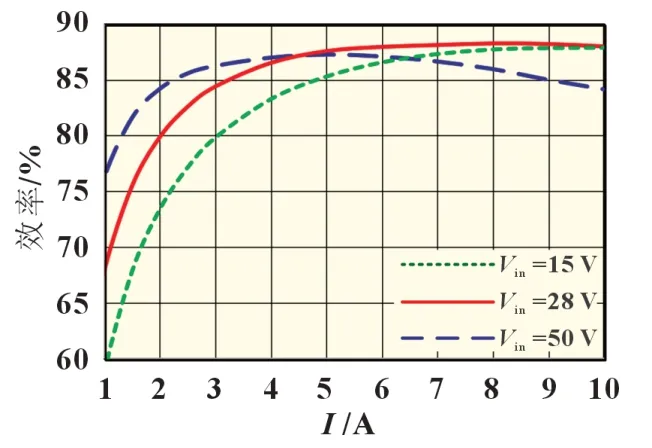

图6 给出了在最低、最高及额定输入电压下,不同负载电流时的效率曲线,从图6 中可以看出最高效率达到88%以上。在全输入电压和全负载范围内,输出电压在3.302~3.306 V,调整率小于0.5%,满足设计要求。

图6 效率曲线

4 结论

本文结合设计指标选用ADP1071-2 控制芯片,应用平面变压器和GaN 晶体管设计研制了一台3.3 V/10 A 的高效率超薄反激变换器。阐述了平面变压器磁芯选取、匝数计算和PCB 绕组的详细设计方法,给出了原边GaN 晶体管、副边同步整流管和输出滤波电容的参数选型分析。实验样机满载效率可达88%,厚度仅为6 mm,质量仅18 g,比功率高达4 kW/L,满足轻薄、高效率、高功率密度、开关电源绿色化的发展要求。