多路精确稳压输出的数字DC-DC变换器设计

2023-10-05鄢婉娟

侯 伟,鄢婉娟,彭 健

(航天东方红卫星有限公司,北京 100094)

目前航天器上使用的DC-DC 变换器均为传统模拟电路设计,且很大一部分依赖进口。与模拟技术实现闭环反馈控制的DC-DC 变换器相比,数字电路具有以下优点:1)可实现多路独立闭环控制、精确稳压输出,具有快速响应能力及调节能力;2)可实现硬件拓扑的通用化设计,通过参数设置实现针对不同对象的应用;3)抗干扰能力强,避免了模拟信号的畸变失真;4)控制参数设计精确,一致性好,性能稳定;5)具备高度的柔性、智能化和可操控性,可通过远程诊断实现故障管理。本文以常用的XX28512 (28 V 输入,+5 V、±12 V 三路输出)型DC-DC 为例,设计一款三路(+5 V/3.6 A、+12 V/0.5 A、-12 V/0.5 A)独立闭环控制、精确稳压输出且电压可通过软件设置的数字DC-DC 变换器。

1 方案设计

数字化DC-DC 变换器的设计分硬件电路设计和软件程序设计两个部分。

依据多路输出、每路精确稳压的要求,数字化DC-DC 变换器的设计必须建立三个独立的闭环进行稳压。为了提高输出电压的调节速度和避免原、副边通信带来的软、硬件设计的复杂性,数字化DC-DC 变换器的总体框架采用主控制器在变压器副边、辅助控制器在原边的设计方案,三路输出电压全部在副边构成闭环,由主控制器直接进行调节,而不用将电压信息隔离反馈到原边。DC-DC 变换器的主拓扑原理框图如图1 所示。

图1 主拓扑原理框图

数字化DC-DC 变换器的主拓扑采用推挽变换器结构,提高了输入电压和变压器的利用率,而且副边绕组的整流电路无需滤波电感,电路结构简单。副边三路共用一路母线,+5和+12 V 输出采用同步Buck 变换器实现稳压,-12 V 采用同步Buck/Boost 变换器实现稳压。采用同步整流的设计方式不仅可以减小续流二极管的导通损耗,提高转换效率,而且实现了负载和母线的能量双向流动,负载变化时每路后级调节的占空比变化较小,减小了对副边母线电压的影响和负载不平衡时各路之间的交叉调节[1]。

数字化DC-DC 变换器的原、副边各有一个控制器,两个控制器互相隔离。主控制器在副边,完成副边三路的稳压调节、输出电压过压保护、输出电流过流保护、各路输出软启动、电压时序控制、使能、同步和通信功能。辅助控制器在原边,完成原边互补推挽开关管的控制、输入电压欠压保护、输入电流过流保护和原边软启动功能。

2 硬件设计

2.1 主拓扑设计

数字化DC-DC 变换器的主拓扑采用推挽变换器结构,如图2 所示。输入电压的设计范围是23~33 V,经一级LC 滤波后输入到主变压器。原边控制器在软启动之后,使两个开关管分别以0.45 的固定占空比互补导通(死区时间为100 ns),将能量传递到副边绕组中,并经过全波整流、滤波后得到比较稳定的副边母线电压。为了避免与副边三路Buck 的开关频率(312 kHz)之间产生拍频干扰,原边的开关频率稍高于副边的开关频率,定为320 kHz。

图2 主拓扑原理图

为了减小开关动作时的导通损耗和关断损耗,主开关管和副边母线的整流二极管都加有相应的吸收电路,防止开关温升过高损耗器件。原、副边的“地”之间接有一高压吸收电容,减小地之间的高频干扰。根据工作频率以及输出功率,主变压器的磁芯选用TDK 公司PC40 材质的磁罐,尺寸选择P18/11,原、副边每个绕组的匝数分别为8 匝和6 匝。

2.2 同步Buck(Buck/Boost)变换器设计

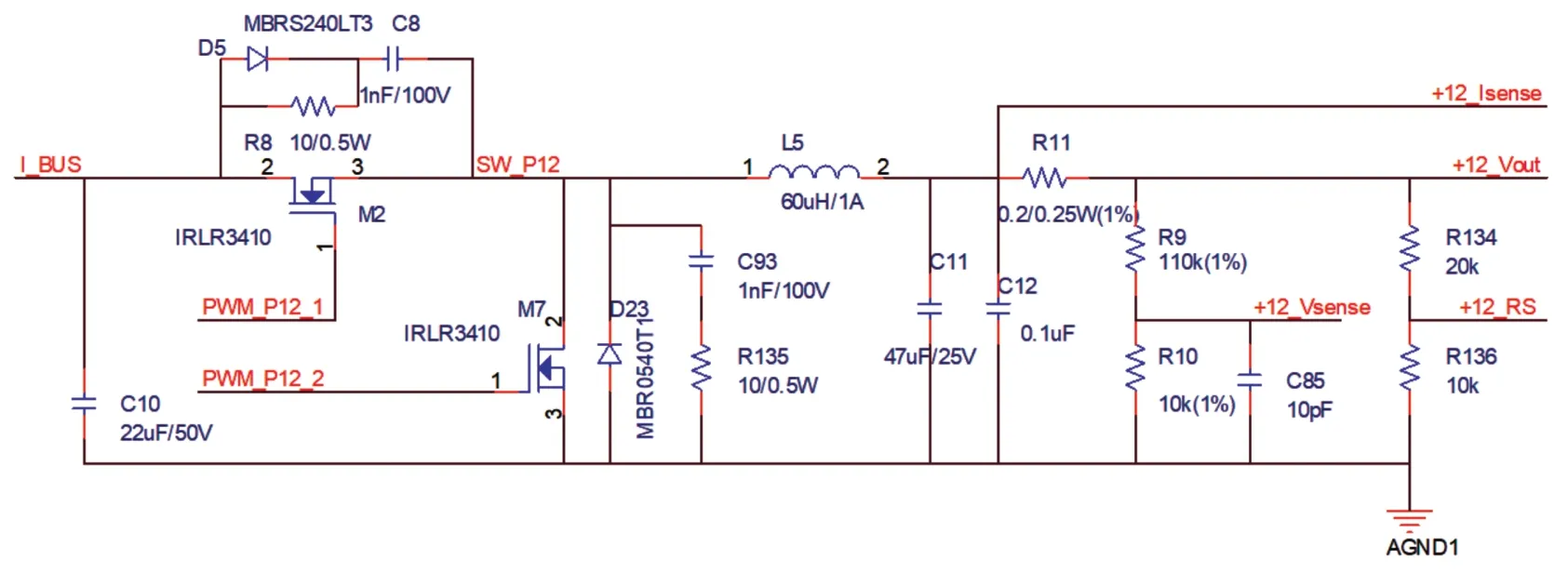

副边+5 和+12 V 输出采用同步Buck 的变换器结构,而-12 V 由于输入、输出电压极性相反,采用同步Buck/Boost变换器结构,每路独立稳压调节。+5、+12 和-12 V 的电路原理分别如图3、图4 和图5 所示。每路输出都采用电压闭环稳压调节,每路输出电流采用电阻取样,因为三路输出共地,所以取样电阻放在输出高端,防止地线中产生干扰,避免各路之间相互影响。正电压输出+5 和+12 V 的有遥测端子,遥测电压为+4 V,遥测分压电阻的值要尽量大,以减小对输出电压和效率的影响,但是必须满足遥测阻抗的要求。

图3 +5 V输出同步Buck原理图

图4 +12 V输出同步Buck原理图

图5 -12 V输出同步Buck/Boost原理图

同步Buck/Boost 变换器就是将传统Buck/Boost 变换器中的续流二极管换成MOSFET,因此,与其他两路不同的是,-12 V 的两个MOSFET 都需要高边驱动[2]。由于进行电压取样信号放大的运放为正电压单电源供电,-12 V 的电压检测与其他两路不同,不是分压后进行取样,而是采用倍数为1/12的反相放大器实现负电压取样。

3 软件设计

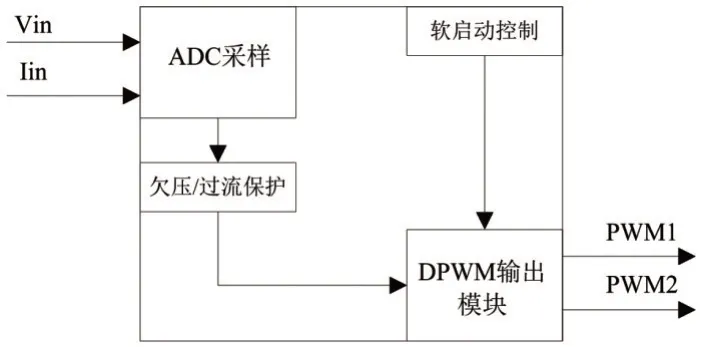

原边控制器和副边控制器的总体功能设计框图如图6 和图7 所示[3]。

图6 原边控制器功能设计框图

图7 副边控制器功能设计框图

数字DC-DC 变换器工作流程如图8 所示。在发生过压、过流等异常情况时,控制器首先关闭控制信号,并且在检测异常消失延时一段时间后重新软启动,且恢复时间可程序设定。数字化控制器的通信协议中采用16 位的CRC 校验,保证上位机的数据可靠写入数字化电源模块中。考虑到特定的应用环境,设计中采用了三模块冗余(TMR)技术,每个参数在E2PROM 存储器中有三个备份,以抵抗单粒子翻转对E2PROM 造成的影响[4-5]。

图8 数字DC-DC变换器工作流程

4 测试结果

数字DC-DC 变换器实现了三路独立精确稳压且输出电压在额定值±20%范围内可设置,同时上电时序、输出过压、过流保护值、PID 参数等可设置。频率同步可通过外接时钟实现。图9 给出了参数配置软件的界面,可以对+5、+12、-12 V 三路的输出电压基准、过压保护值、过流保护值、上电延迟时间、PID 参数等进行独立设置。

图9 数字DC-DC变换器参数配置软件

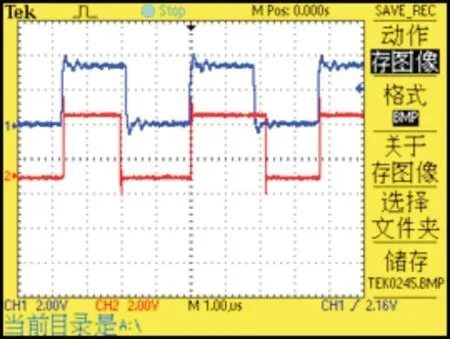

图10 和图11 给出了上电延迟时间设置后的启动时序,图10 中+5、+12、-12 V 启动时序分别为0、5、10 ms,图11 中+5、+12、-12 V 启动时序分别为0、5、15 ms,三路上电延迟时间在0~100 ms 范围内可设置,验证了数字DC-DC 变换器上电时序设置功能。外接时钟270 kHz 时,数字DC-DC 变换器的开关频率如图12 所示,外接时钟320 kHz 时,数字DC-DC变换器的开关频率如图13 所示,验证了外部时钟频率同步功能。

图12 初始的外部时钟与PWM波形(蓝线:外部时钟信号;红线:控制器的PWM信号,同步频率270 kHz)

图13 调整参数后的外部时钟与PWM波形(蓝线:外部时钟信号;红线:控制器的PWM信号,同步频率320 kHz)

5 结论

本文完成了一款三路输出,各路独立稳压、输出精确可调的数字化DC-DC 变换器的设计与验证,取得了以下主要成果:通过对多路稳压输出拓扑结构比较与分析,设计了以推挽变换器为主体、副边三路后级闭环稳压控制的拓扑结构,在FPGA 平台上采用状态机结构完成控制算法的运算时序与控制逻辑,实现高精度DPWM 模块,完成了多路信号高速采样,实现了数字化DC-DC 控制器的核心功能;通过状态机控制总线的时序逻辑,实现I2C 总线和UART 接口通信的设计,提供了数字化电源参数的存储方式,并且可远程修改电源的运行状态,数据存储中,采用三个备份的方式对每个数据进行读写操作,保证参数的准确性和电源的安全性,实现了数字化控制器的智能化与容错机制设计。