任意信号发生器系统设计

2023-08-10余梦新吴银川

余梦新,吴银川

(西安石油大学 陕西省油气井测控技术重点实验室,西安 710065)

0 引言

在实际应用中,除了需要一些规则的信号,如正弦波、三角波、方波等,还需要一种能够产生各种不规则波形的仪器,如生物电子工程中常见的各种生物电波、人体产生的各种信号波,如心脏跳动过程,电子设备产生的各种干扰杂波、模拟电路各种瞬变波形等。这类波形不仅不规则,且无法直接获取,普通信号发生器很难产生[1]。此时,设计任意信号发生器具有重要意义。

与传统的信号发生器相比,任意信号发生器的最大优势在于产生信号的方式灵活多变,它可以根据用户的测试需求进行仿真。目前,市面上任意信号发生器常见的波形信号合成技术有直接数字波形合成技术(Direct Digital Waveform Synthesis,DDWS)和直接数字频率合成技术(Direct Digital Frequency Synthesizer,DDFS)。该技术均是通过改变采样时钟和波形点数改变输出波形频率,再利用D/A 转换器进行数模转换,完成波形输出。但该方法面临着模拟通道内低通滤波器设计困难以及波形易受模拟通道内的元器件的影响,因此在输出波形时幅度不够平坦[2,3],影响波形质量。而且目前常见的任意信号发生器大多数是通过外接电路进行介入,没有独立的系统[4]。因此,本文在该背景下,设计任意信号发生器的自适应闭环控制系统,通过上位机结合下位机的方式,设计一个独立的任意信号发生器系统。

1 方案设计

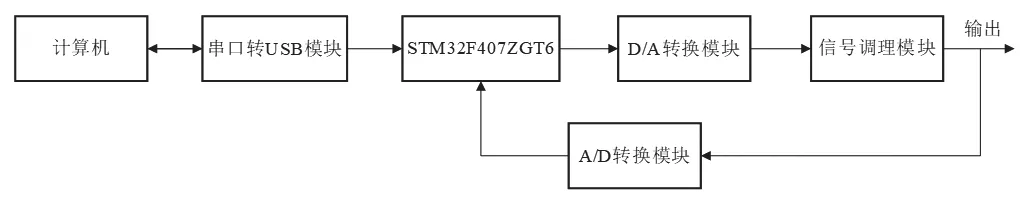

系统主要由上位机与下位机两部分组成,上位机软件主要是实现任意波形数据的产生、采集、显示功能。下位机由以STM32F407 为核心的控制模块、D/A 转换模块、A/D 转换模块以及信号调理模块组成。

任意信号发生器系统框图如图1 所示。用户利用上位机产生任意模拟信号波形数据,通过串口转USB 模块送至单片机。单片机完成信号接收与存储,并送至D/A 转换模块进行数模转换,经过信号调理等操作,输出用户所需要的波形信号。单片机再将输出波形进行采集,经过A/D 转换模块,完成模数转换。利用USB 或者串口上传至上位机软件显示,从而实现信号的自适应闭环控制。

图1 任意信号发生器系统框图Fig.1 Block diagram of any signal generator system

2 任意信号合成原理

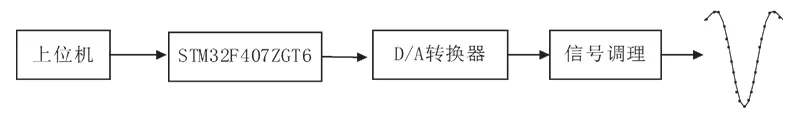

2.1 信号数据生成原理

任意波形合成框图如图2 所示,上位机软件通过函数计算得到波形数据点,其长度可以根据波形的复杂程度或者用户对波形的精度要求而改变。采样点数越多[5,6],波形的还原度越高,显示的波形就越完美。数据位数选用D/A转换器的位数,本文采用12 位宽的DAC。将已经采样好的波形数据通过串口下传至单片机进行处理,完成D/A 转换,将数字量转换为模拟量,经过滤波等信号调理获得需要的波形。

图2 任意信号波形数据合成原理框图Fig.2 Schematic block diagram of arbitrary signal waveform data synthesis

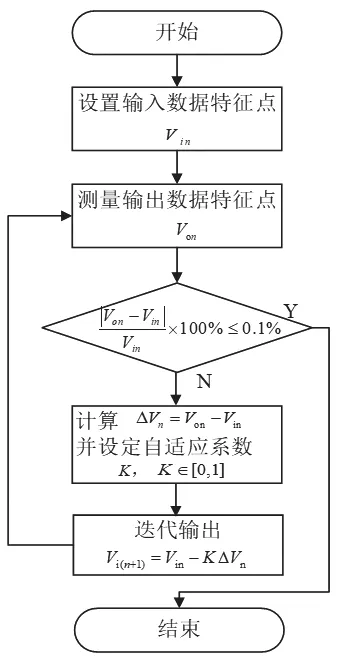

2.2 输出信号自适应原理

输出信号自适应流程图如图3 所示。其中,Vin是输入波形各点电压,Von是波形输出实际电压,Kn是自适应系数,取值范围为[0,1]。通过计算特征点的相对误差,判断是否完成自适应处理。具体步骤如图3。

图3 输出信号自适应流程Fig.3 Output signal adaptation process

Step1:设置输入数据特征值Vin。

Step2:测量实际输出数据特征值Von。

Step3:判断特征点相对误差|Von-Vin|/Vin×100%≤0.1%;若该点的相对误差小于等于0.1%,则迭代结束,转入Step6;若该点的相对误差大于0.1%,则转入Step4。

Step4:计算ΔVn=Von-Vin,并设定自适应系数Kn,Kn∈[0,1]。

Step5:迭代输出Vi(n+1)=Vin-KnΔVn,转入Step2。

Step6:自适应结束。

3 硬件设计

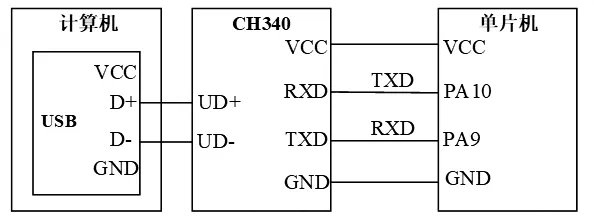

3.1 串口转USB接口设计

接口电路设计如图4 所示。单片机STM32F407 作为下位机的控制端,需要接收上位机(计算机)传来的指令,对指令进行解析,然后根据解析内容执行或协调其他模块的工作。它主要依靠TXD、RXD 两个管脚进行通讯。该系统计算机选择USB 接口与单片机进行数据传输。所以,要实现单片机与计算机的串行通信,需要在控制电路中设计一个通信接口电路来实现串口与USB 接口的数据传输[7]。因此,需要借助芯片CH340 完成串口与USB 两处接口的电平转换,芯片CH340 无需外挂晶振,且能自行产生时钟,数据传输波特率最高达12500Mbps。

图4 串口转USB接口设计Fig.4 Design of serial port to USB interface

图5 ADC时序图Fig.5 ADC Timing diagram

3.2 DAC参数配置

STM32F407 的DAC 模块(数字/模拟转换模块)是12位数字输入,电压输出型的DAC。它可以配置8 位或者12位模式,也可以与DMA 控制器配合使用,DAC 工作在12位模式时,数据可以设置成左对齐或者右对齐数据格式,DAC 模块有两个输出通道,每个通道都有单独的转换器。本系统就是使用单个DAC 通道1 进行数模转换的。采用12 位的右对齐方式,不采用硬件触发,存入寄存器DAC_DHRx 的数据会在一个APB1 时钟周期后自动传入寄存器DAC_DORx[8]。当DAC 的参考电压为VREF+的时候,即3.3V,它的输出电压也是线性的,电压范围为0 ~VREF+。

DAC 配置如下:

1)开启PA5 时钟和ADC1 时钟,设置PA5 为模拟输入。

2)设置DAC 的工作模式,该部分设置包括:DAC 通道1 使能,DAC 通道1 输出缓存关闭,不使用波形发生器,不使用硬件触发等。

3)设置DAC 输出值,配置好上述3 个步骤,DAC 就可以开始工作了,这里使用12 位的右对齐数据格式,在DAC 的输出引脚(PA5)可以得到不同的电压值。

3.3 ADC参数配置

ADC 时序图如5 所示。STM32F407 具有12 位逐次趋近型模数转换器(ADC)。它具有多达19 个复用通道,可测量来自16 个外部源、2 个内部源和V BAT 通道信号。这些通道的A/D 转换可在单次、连续、扫描或不连续采样模式下进行。ADC 的结果存储在一个左对齐或者右对齐的16位数字寄存器中[9]。该系统设计采用STM32F407 内部的ADC 进行波形数据采集,配置如下:

1)开启ADC1 时钟和PA5 时钟,设置PA5 为模拟输入。

2) 配置ADC 输入时钟分频,模式为独立模式,以及设置ADC 的通用控制寄存器CCR 等。

在系统设计中,由于ADC 的总线时钟为84M,但是当ADC 的采样时钟超过36M 时,采样数据失真程度较大。因此,需要对该总线时钟进行分频处理。为了满足最大时钟频率不超过36M 的要求,这里设置对ADC 总线时钟进行4分频,就能得到ADC 的采样时钟为24M。

3)对ADC 参数进行初始化处理并设置ADC1 的转换分辨率、转换方式、对齐方式,以及规则的序列等相关信息。

ADC 的转换分辨率就是采样数据的位数,可以进行多种位数的配置,但采样周期与之息息相关,转换分辨率较高时,采样周期较长;反之,转换分辨率较低时,采样周期较短。本系统采用中断触发模式,边沿触发设置为上升沿触发,这样当模数转换器检测到外部脉冲信号的上升沿时,就会启动ADC 进行一次采样。在转换结束后,便可以读取ADC 规则数字寄存器中的值了。

4 软件设计

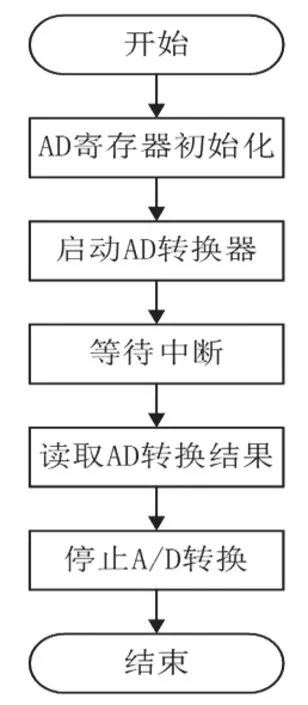

4.1 AD转换程序设计

A/D 转换流程图如图6 所示。首先对AD 寄存器进行初始化处理,然后启动A/D 转换器,等待中断服务,依次读出A/D 转换结果,最后停止A/D 转换。

图6 A/D转换流程图Fig.6 A/D Conversion flowchart

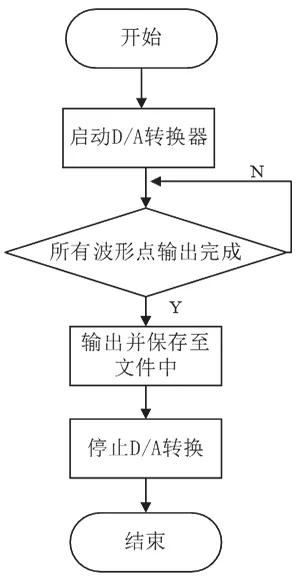

4.2 DA转换程序设计

D/A 转换流程如图7 所示,首先启动D/A 转换器并完成参数配置,将所有波形点数据经过数模转换后,并保存至文件中,最后停止D/A 转换器。

图7 D/A转换流程图Fig.7 D/A Conversion flowchart

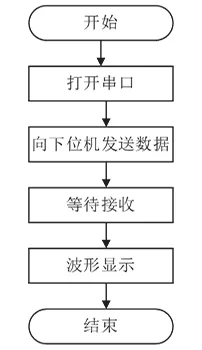

4.3 上位机程序设计

上位机程序流程图如图8 所示,首先上位机配置并打开串口,设置串口的工作方式为默认方式,然后向下位机发送模拟信号数据,等待下位机接收与处理,最后完成波形显示。

图8 上位机程序流程图Fig.8 Upper computer program flowchart

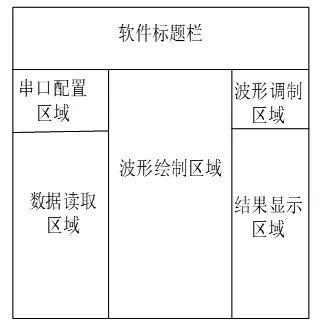

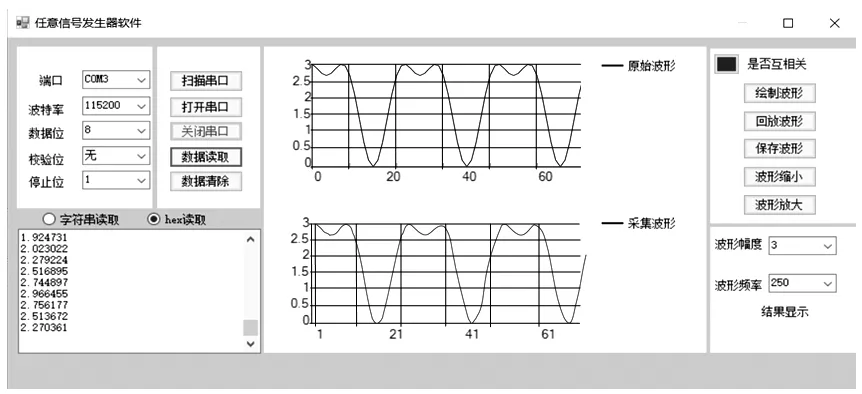

4.4 软件界面设计

上位机软件界面设计框图如图9 所示。本文基于Visual Studio 2022 开发环境,采用C#语言对任意信号发生器系统进行开发与设计[10-12],根据系统所需要的功能将上位机软件界面区域划分为以下部分:串口配置区域、波形绘制区域、波形调制区域、结果显示区域、数据读取区域。

图9 上位机软件界面设计框图Fig.9 Design block diagram of upper computer software interface

串口配置区域负责配置串口端口、波特率、数据位、停止位、校验位;波形绘制区域负责描绘输出波形以及采集波形;波形调制区域负责波形的缩小、波形的放大以及波形的回放。结果显示区域负责显示输出波形的频率与幅度,数据读取区域负责读取输出波形各点电压值。

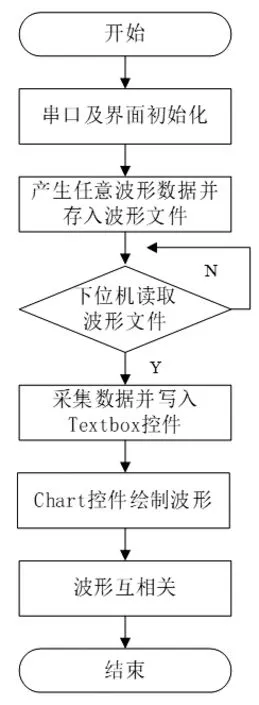

4.5 软件流程设计

上位机软件设计如图10 所示。首先进行串口及软件界面初始化,然后上位机产生任意波形数据并存入波形文件中,下位机接收到指令,对文件读取并进行信号处理,完成波形输出。再将输出波形采集,并进行自适应处理,最后使用Chart 图表绘制波形图。

图10 上位机软件设计图Fig.10 Upper computer software design diagram

5 系统测试结果

通过实验室内验证该系统原理,充分证明了该系统的可靠性,从中得到以下结论:

1)该系统设计输出任意信号稳定可靠,上位机软件编程及控制能力良好,下位机执行状况良好,满足系统的自适应闭环控制。

2)上位机软件测试图如图11 所示。该系统具有输出任意信号波形的能力,通过上位机可以产生正弦波、三角波、方波以及用户需要的任意波形数组,下位机完成信号接收与处理,输出波形在上位机上显示。

图11 上位机软件测试图Fig.11 Upper computer software testing diagram

3)输出信号电压范围是0V ~3.3V,电压最大相对误差不大于0.1%。

6 总结

本设计不仅可以输出任意信号,同时也具有输出频率稳定、输出波形连续等优点。波形合成过程中存在一定的误差,如幅度量化误差,通过提出输出波形自适应原理,对特征点电压进行自适应处理,控制其电压相对误差在0.1%以内,观察结果并发现波形质量明显改善,精确度也有提高。该设计利用上位机软件也可以对信号波形进行存储与再现,也为测量结果进一步分析提供了方便。系统总体设计结构简单,拓展性能好,易于操作,设计成本低,为模拟实际工程需要信号提供了一种辅助手段。