基于MicroBlaze软核的射频控制系统设计与实现

2023-07-17魏志瑾

魏志瑾,王 园

(1.中国电子科技集团公司第二十研究所,陕西 西安 710068;2.中电科星河北斗技术(西安)有限公司,陕西 西安 710068)

0 引 言

随着现场可编程门阵列(FPGA)技术的发展,FPGA的成本越来越低,资源容量越来越大。同时随着嵌入式系统的需求在不断变化,系统外围设备复杂性逐渐增加。由于FPGA自身稳定性强、可靠性高、成本低的特点,利用FPGA代替处理器系统进行越来越多的功能设计已渐成趋势。可编程片上系统(SOPC)将CPU核与外设核以及系统软件集成到单一芯片中,可以帮助用户快速“量身定制”所需要的产品,为用户提供省资源、高可靠的基于FPGA的嵌入式设计方案[1]。

Xilinx公司推出的MicroBlaze软核是一个功能齐全、指令集少、高度可配置的32位RISC微处理器[2],用户可以利用它将丰富的处理器外围设备、内存、接口等,在嵌入式开发套件(EDK)中组合成定制化、高性能的嵌入式系统,无缝集成到Xilinx Vivado设计中。MicroBlaze软核已应用到工业、医疗、汽车、军工等诸多行业中,它丰富的可配置性和高性能已经发展成为替代ARM Cortex-M CPU的主流趋势,尤其是当硬件资源紧张时,在1片FPGA中内嵌MicroBlaze软核代替FPGA+数字信号处理器(DSP)/CPU的架构,优势明显。

本文在1片Xilinx的FPGA上基于MicroBlaze软核设计一套射频控制系统,完成解析上位机通过控制器局域网(CAN)总线、通用异步收发联接器(UART)总线等下发的软件控制协议,并依据解析出的指令控制射频组件,完成射频模块的收发工作。

1 射频控制系统结构

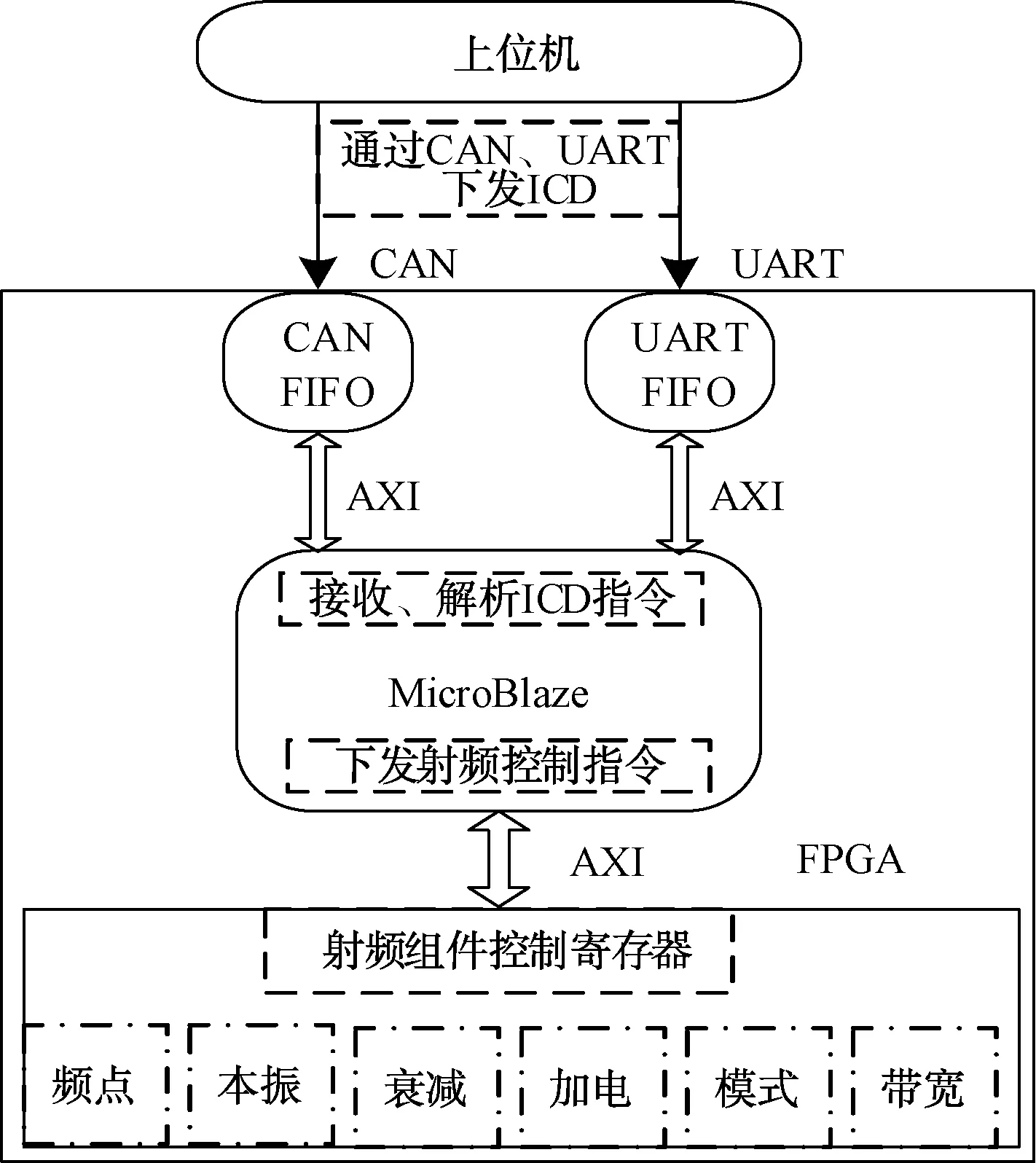

基于某课题的射频控制系统主要是在FPGA上通过CAN总线、UART总线接收上位机下发的接力控制文件(ICD)控制命令,在本地经过相应的先进先出(FIFO)缓存;在FPGA内搭建MicroBlaze软核,将FIFO缓存的数据通过高级可扩展接口(AXI)总线发送给MicroBlaze软核;在软核的软件开发工具包(SDK)中,解析ICD指令并通过AXI总线下发射频控制指令;在FPGA端完成射频控制寄存器的赋值与输出,实现对射频组件的频点、本振、衰减、加电、模式等的控制。其结构框图如图1所示。本文重点介绍基于MicroBlaze软核的数据通信,包括软核的架构、搭建、EDK开发、应用以及相应的AXI总线通信。

图1 射频控制系统结构框图

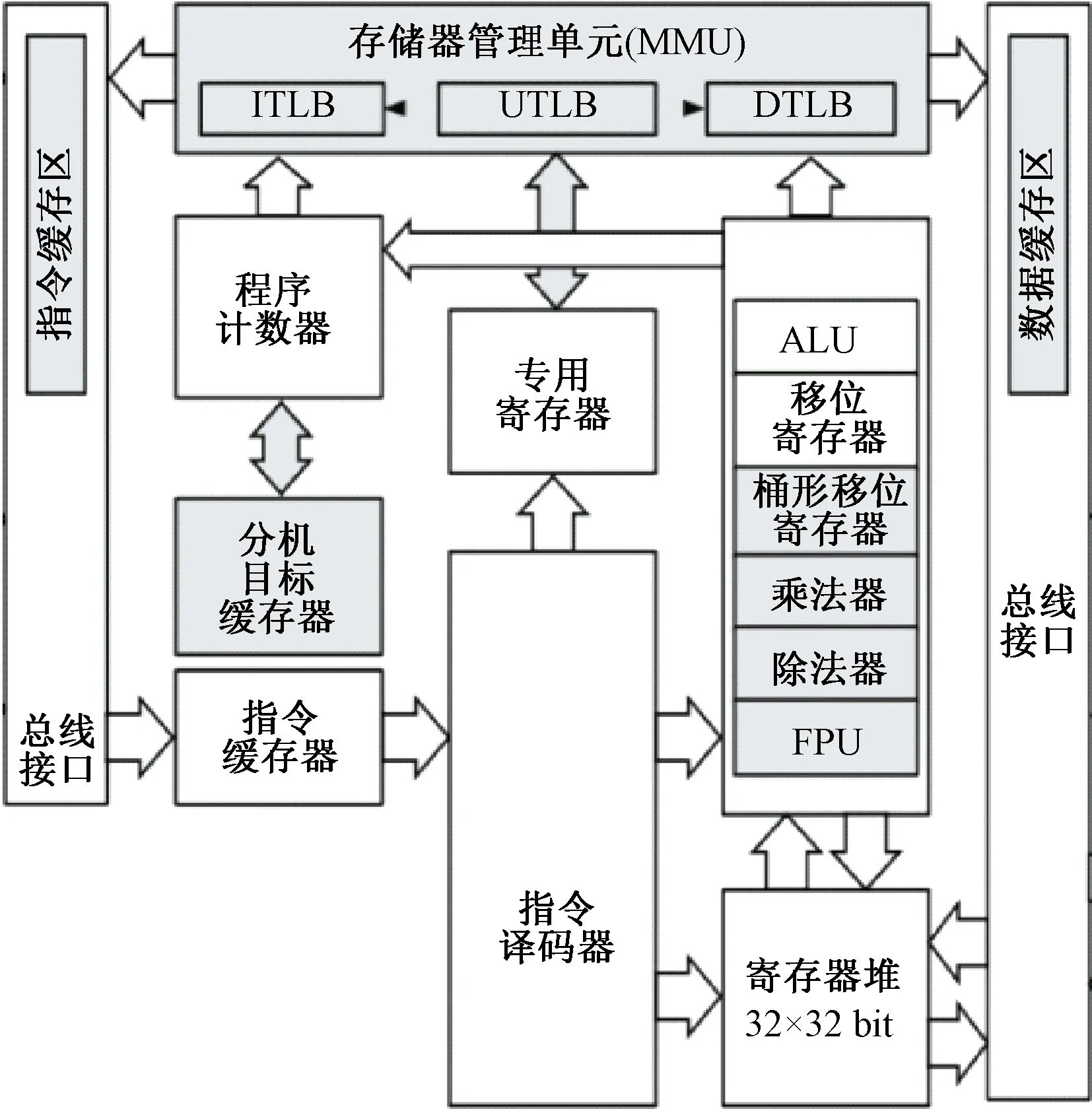

MicroBlaze软核采用精简指令集(RISC)架构和哈佛结构,具有32位独立的地址总线和数据总线;32位指令系统,支持3个操作数和2种寻址方式;具有高速的指令和数据缓存Cache.5级流水线结构;带有8个主/从快速单工链路接口;提供最大256 kbit的片上本地内存接口和片上随机存取内存块(BRAM)连接,通过网络本地存储器(LMB)或AXI总线直接访问片内BRAM;使用快速点对点连接(FSL)接入系统,完成点对点输入/出或协处理器的用户IP开发[3]。图2为MicroBlaze软核的功能框架图,深色部分为可配置项,它可以通过网络局部(PLB)总线或AXI总线与EDK软件包将自带的各种软外设根据用户需求进行连接,并支持用户自定义IP通过PLB总线、AXI总线、FSL总线与MicroBlaze软核连接,发挥FPGA设计的灵活性[1]。

图2 MicroBlaze软核功能框图

MicroBlaze可以与8种外设进行交互,分别是串行外设接口(SPI)、二线制同步串行总线控制接口、UART口、中断控制接口、定时器、通用输入输出(GPIO)口、双倍速率(DDR)控制接口、以太网控制接口,实现对从属设备的控制与数据交换。在本次课题设计中,将用AXI总线连接MicroBlaze软核,并调用SPI接口、UART口、中断控制接口、GPIO口等外设。

2 射频控制系统设计

2.1 MicroBlaze软核XPS平台搭建

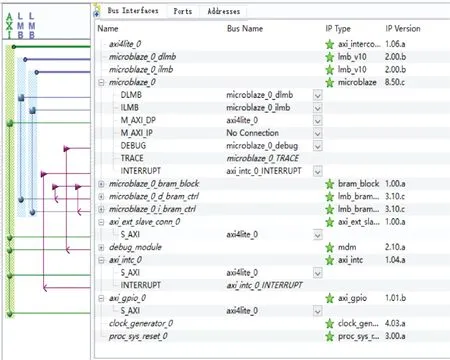

MicroBlaze软核的搭建需要在XPS(Xilinx Platform Studio)组件中完成,结合本文需求,在XPS中创建参考时钟100 MHz,本地存储64 kbit的Micro Blaze处理系统同时添加GPIO、中断控制器(AXI Interrupt Controller)、时钟产生器(clock_generator)、系统复位模块(Proc_sys_reset)、AXI外部受控连接(AXI External Slave connector)模块等所需外设。其中AXI总线协议配置为AXI4 lite,中断方式设置为上升沿触发,GPIO核设置使能中断。在总线接口(bus interface)中,确保时钟、复位以及各个模块端口连接至外部端口(External Ports)。设置完成后,生成软核配置如图3所示。

图3 MicroBlaze软核XPS平台配置

2.2 MicroBlaze软核SDK开发

Xilinx SDK提供了API开发所需的接口文件和库文件,以及必要的帮助文档。在本课题中,需要将ICD协议通过CAN总线和UART总线送至FPGA中;FPGA通过FIFO将收到的CAN总线和UART总线数据经过片内AXI总线送至软核;在软核的SDK中进行ICD信息解析,根据不同的地址空间区分CAN总线数据和UART总线数据;根据协议将UART数据解析为工作模式控制、频率控制、应答指令3类;并最终下发本振配置、衰减设置、加电、带宽设置、频率码等控制参数;将CAN数据解析后,设计出BIT处理、状态查询、程序更新、系统时下发、二本振开关设置等功能;控制参数通过AXI总线送给FPGA射频控制寄存器,完成对射频模块的控制。SDK开发的软件最终生成.elf文件,嵌入到FPGA工程中,集成编译。软件开发框图如图4所示。

图4 射频控制系统SDK开发框图

2.3 AXI接口通信设计

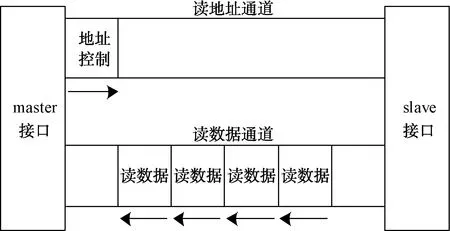

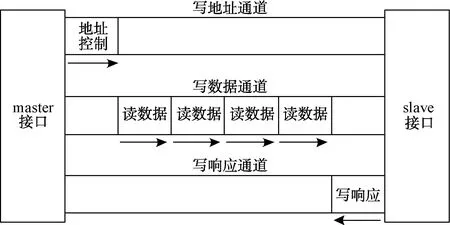

AXI总线是由ARM公司提出的面向高性能、高带宽、低延迟的片内总线。本文应用AXI总线进行软核与FPGA寄存器/FIFO的数据传输,定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。地址通道携带控制消息,用于描述被传输的数据属性;数据传输使用写通道来实现master到slave的传输,master端首先向发送写控制,然后写入要发送的数据,slave在收到本次写的数据后给出写响应信号代表接收完成;读通道用来实现数据从slave到master的数据传输,master向slave发送要读取数据的地址,slave收到后再将数据通过读数据通道发送给master。图5为AXI读架构图,图6为AXI写架构图。

图5 AXI读架构图

图6 AXI写架构

3 射频控制系统验证

3.1 AXI总线时序仿真验证

本文设计AXI总线作为MicroBlaze软核与FPGA端通信总线,并进行了写数据、写地址、写响应、读地址、读数据仿真。当软核通过AXI写数据时,首先将写地址通道的M_AXI_AWVALID拉高,M_AXI_AWADDR与之对齐输出;再将写数据通道的M_AXI_WVALID拉高,M_AXI_WDATA与之对齐输出,并且注意1个WDATA对应1个WVALID,当收端收到后会将M_AXI_BVALID拉高;当软核通过AXI读数据时,将读地址通道的M_AXI_ARVALID拉高,M_AXI_ARADDR与之对其输出;收到的数据将会通过读数据通道的M_AXI_RDATA和对应的M_AXI_RVALID给过来,此时M_AXI_RREADY信号也会在数据有效时拉高。如图7所示,模拟发端发送数据111111、222222、333333、444444,收端收到后同时将4个数据回传给发端,仿真时序结果与设计一致,验证了AXI总线设计的正确性。

图7 AXI收发时序仿真验证

3.2 控制系统集成上板验证

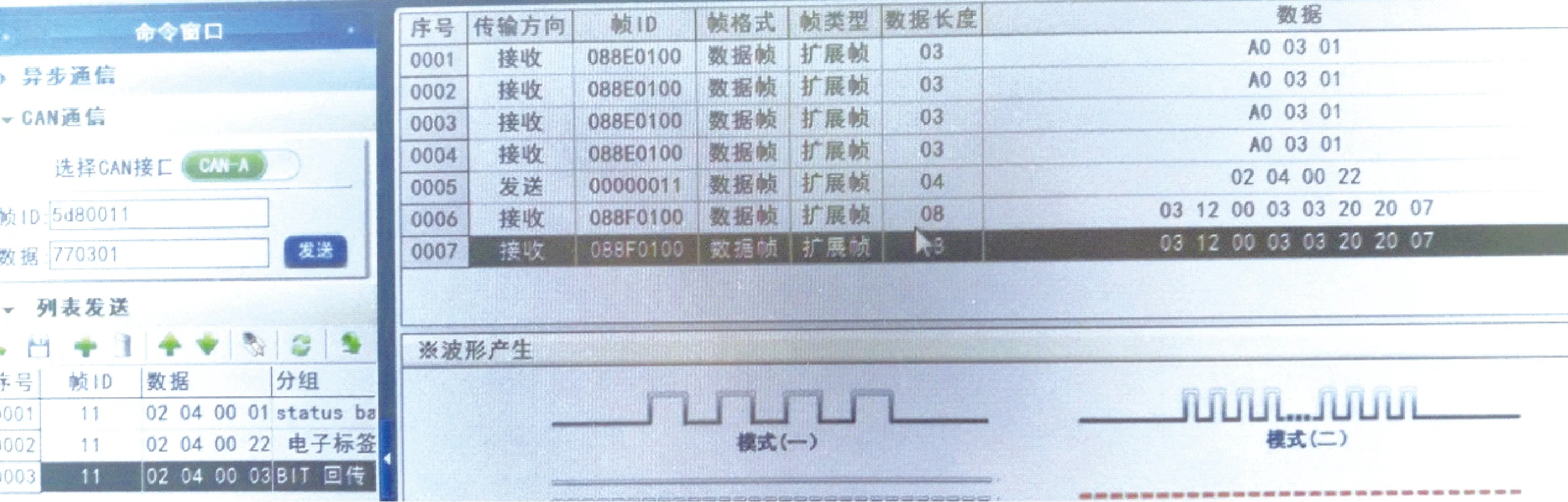

将生成好的MicroBlaze软核以及ICD解析文件.elf嵌入至FPGA工程中。在FPGA工程中,利用收到的软核数据分别完成对射频组件的频点、本振、衰减、加电、模式等的控制逻辑,集成编译,生成.bit文件,下载至射频模块的数字接口板上的FPGA里,利用上位机下发ICD控制指令,通过上位机接收的回传信息以及频谱仪、功率计的测试结果,判定控制系统工作是否正确。上位机界面如图8所示。经测试,接收的回传信息与ICD核对无误,频谱仪测试发射及接收的频谱、本振、接收模式与控制指令相符,功率计测试信号大小与衰减指令相符。后续射频模块随整机测试,功能、性能满足要求,进一步验证了射频控制系统设计的正确性。

图8 上位机测试界面

4 结束语

MicroBlaze软核因其可定制IP的方便性,以及软核的成熟、稳定性,让FPGA中内嵌软核开发越来越成为通信系统设计的趋势。尤其是在板卡硬件资源紧张、逻辑开发ICD协议解析复杂度高、开发周期长的背景下,选用1片内嵌MicroBlaze软核的FPGA来实现ICD协议解析和通信系统的控制,缓解了硬件资源紧张,降低了开发复杂度,缩短了开发周期,极大凸显了应用软核的优势。本文依据某课题,设计了基于MicroBlaze软核的射频控制系统,描述了软核生成和配置设计、SDK开发设计以及AXI总线通信设计,并通过仿真和集成上板调试,验证了设计的正确性。