基于JavaScript的计算机组成原理虚拟实验系统的设计

2023-06-03白家璇辛雨雯崔天宇

白家璇 辛雨雯 崔天宇

关键词:JavaScript;虚拟实验;计算机组成原理

中图分类号:G642;TP391 文献标识码:A

文章编号:1009-3044(2023)10-0059-04

0 引言

计算机组成原理是中国民航大学本科计算机专业的专业基础课,通过学习,体会到本课程的实践性很强,需要动手操作实践才能真正理解理论内容,但传统的只在实物实验箱上进行实验操作存在很多不足。譬如:1)固化的内部电路,内部的每个功能模块硬件电路已焊接好,只需连接I/O导线即可搭建电路连接图,对硬件电路缺乏设计动手能力的培养,而且也只能做相对固定的实验,不方便扩展,难于进行设计性和综合性实验,更新换代等都很难跟上时代的发展需求;2)已经封装好的实验箱,其内部的实现原理、运行状态等都无法直接观察;3)实验室的开放时间有限,因人力资源、学生自身的上课安排、实验室课程安排等现实原因造成大多数情况下,学生能使用实验箱的时间远远不足,学生的实验时间和空间受到极大限制;4)在实验连线时,容易对同颜色的接线进行混淆,同时,如果实验箱有问题或者部分接线的损坏,对于学生来说都是未知的,在排查错误时,不容易将这些硬件的自身问题找出来,会导致实验效率低下[1]。本文主要介绍一种基于JavaScript设计开发的实验仿真平台,配合实物实验箱进行实验,能大大提高学生的实验和学习效率。

1 系统设计方案

本系统在功能上主要开发数字逻辑课程中的基本逻辑元器件,譬如与、或、非等各种门电路,D触发器等芯片,对所生成的器件功能验证完成之后,再将这些器件组合应用于计算机组成原理课程的各种功能模块的设计实验中,譬如运算器、微程序控制器、总线电路、RAM存储器读/写、模型机的模拟实验等[2]。在此基础上,作为扩展可以再完成微机接口技术课程的实验,譬如8253计数器/定时器、8255A并行传送、8259A中断等。其中的每一个器件或模块都是分解成一个个小的实验分步实现,最后再组合形成一个具有独立功能的模块。

系统前端采用HTML、CSS、VML 工具,其中CSS实现系统外观的设计及各个部件的具体外形,VML实现组件间的线路连接生成功能;后端采用JavaScript工具;通过UI界面选择实验所需芯片;通过HTML5File API将电路保存为.txt文件(.txt文件具有还原电路功能);选用Webstorm作为代码编译平台(Webstorm具有项目重构、快捷搜索、自动排版、代码提示、错误提示等优点)。另外,还需引入组件调度模块,因为在通过组件库与电路绘制模块设计好电路图之后,运行时还需要解决如何让各个组件协调有序的工作,否则会出错。系统总体功能模块结构如图1所示。

2 系统芯片设计

本系统开发涉及逻辑与、或等各种门电路器件的设计,74LS139、74LS175、74LS273、74LS374等多个数字功能器件的设计,continuousPulse等多个基本原件的设计、EPROM2716只读存储器等多个存储芯片的设计和SuqueTimer脉冲发生器的设计和运算器等多个模块的设计。

2.1 数字功能器件设计

设计一个芯片器件,首先需通过代码定义每个芯片的外观,主要包括定义芯片上对应位置引脚的类型type、数据源器件source、中间器件intermediat、目的器件destination等,每个芯片的设计大同小异,本文以74LS273为例介绍数字功能器件的设计方法。涉及的外观属性主要有:id—芯片编号(唯一,为后面设计前端时引用);type—寄存器上对应位置引脚类型;source—数据源器件;intermediate—中间器件;destination—目的器件;name—器件外观显示名称;width—器件外觀宽度;Height—器件外观高度;PaddingLR—器件左右边距;Pinname—器件引脚名称,Pinwidth—器件引脚宽度(不小于16)。

芯片外观设计好后,还需对芯片的运算条件进行设计与判断。74LS273首先对用户的输入值进行有无变化的判断,如果有变化,返回true,否则返回false,同时判断mr、cp的值(mr为pinNO=0的引脚,cp为pinNo=10的引脚),此处mr为0,处于清0状态,判断函数返回true不为0时,通过cp时钟信号对数据进行锁存。对于74LS273的功能实现函数,还需判断其pinNo是否为0,即mr 引脚,如果本引脚处于低电平,则74LS273芯片处于清0状态,否则正常输出[3-4]。在本74LS273的设计中通过使用for循环实现芯片的功能函数,具体编程代码如图2所示。

2.2 基本原件设计

本文以continuousPulse为例介绍基本原件的设计方法,主要讨论其工作方式。对于是否已达到运算标准的函数判断,因为此功能相当于给一次脉冲,一旦按下这个脉冲,器件就到达了运算条件,所以只需要简单地判断输入端口是否有值输入即可。

对于输入引脚值的设置,系统中使用了if结构进行判断,如果设置输入的值为0,则将其值设置为1,否则设置为0,同时判断芯片是否达到了运算条件[5-6]。

2.3 虚拟组件设计

本文以EPROM2716c4为例介绍虚拟组件的设计方法,其重要引脚为第11(ce)与12(oe)引脚。首先判断芯片所有的值是否已经输入,如果ce片选信号与oe读信号中有一个输入,则返回True,否则返回False;对于只读存储器是否满足运行条件的判断,需通过输入值进行,如果输入的值没有变化,就无须再重新计算,当ce或oe中有一个引脚的值为1时,则各个io引脚变为高阻态。

3 计算机组成原理仿真实验

3.1 全加器仿真实验

全加器仿真实验的电路图设计如图3所示,共用到3个与门、2个或门、2个异或门,3个输入、2个输出(输入、输出见表1)。当Ai和Bi异或后再与Ci-1进行异或可得到SUMi,当Ai、Bi、Ci-1中只要有两个以上的输入为1,则进位Ci=1。所以,只需要将其中的两个变量求与,然后再将结果求或,具体逻辑表达式为:

此全加器共有3个输入量,按照所设计的进行电路连接,分为输出“和”SUMi、进位输出Ci,这样就设计了一个“1位加法器”[7-8]。

按照图3的设计进行电路连接,得到如图4所示的电路图。

由图3、图4和表1可知,此全加器设计都用1作为输入(3个开关均为输入),在遇到第二个与门时,因为第三排为异或门,所以就会有1个0的输入,在左边的最后一个与门处,会接受右分支输入的1个0,这个右分支的0与左分支的1相与,最后输出0结果,小灯灭;同时可以看到,如果右边的小灯为异或,相对于左边,则一个输入为0,另外一个输入为1,两者相与,就能得到1,右边的小灯就会不断闪烁,与实验结果相符。此时,如果把左边的与门改成异或门,原理上左边的小灯应该会亮[9],仿真实验结果也得到了证实,如图5所示。

3.2 RAM 仿真实验

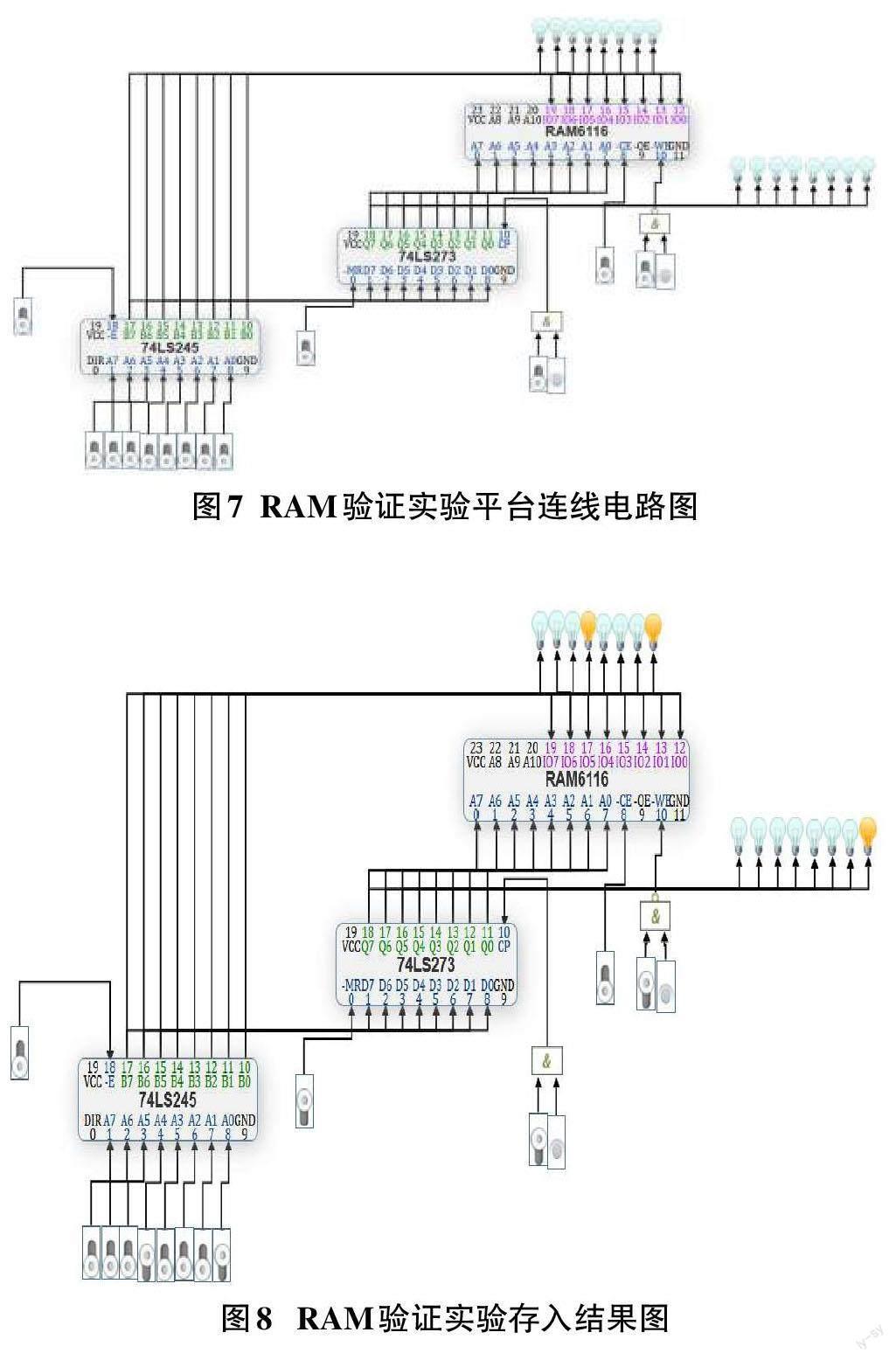

本文以RAM6116随机存储器芯片的读/写操作实验仿真为例,验证RAM的读/写操作以及AR地址寄存器的地址写入功能,验证实验电路图的设计如图6所示,用到了系统所设计的74LS273和74LS245芯片,其中74LS273作为AR地址寄存器使用,同时也作为总线向RAM6116进行写数据的传输寄存器,74LS245作为一条总线向RAM6116写入中间数据寄存器使用,起暂存数据作用,其他的还用到控制数据输入开关,给“与”上升沿脉冲的单脉冲信号P1、P2及用于数据显示的显示灯使用。

此RAM6116的实验原理:SW7-SW0数据开关用于设置读/写地址和欲写入存储器的数据,经三态门74LS245与总线相连,通过总线把地址发送至AR。静态存储器由1片6116(2K×8)构成,但地址输入引脚A8~A10接地,因此实际存储容量为256字节,其余地址引脚A0~A7与AR相连,读和写的地址均由AR给出。6116的数据引脚为输入、输出双向引脚,与总线相连,既可从总线输入要输的数据,也可以通过总线输出数据到数据灯显示。共使用了两组显示灯,一组显示从存储器读出的数据,另一组显示存储单元的地址[10]。

读数据时,在数据开关上设置好要读取的存储单元地址,并打开三态门74LS245,LDAR置1,发出P2脉冲,将地址输入6116,設置6116为读操作,即可读出数据并在数据灯上显示。

写数据时,先在数据开关上设置好要存储单元的地址,并打开三态门74LS245,LDAR置1,发出一个P2脉冲,将地址送入6116,然后在数据开关上设置好要写入的数据,确保三态门打开,设置6116为写操作,发出一个P1脉冲,即可将数据写入。RAM验证实验电路图和如此相连的电路图如图7和图8所示。设置电路的初始状态为MR=1、CE=1、SW-BUS=1。

1)写操作仿真。以存入11H 为例,调节SW7~SW0为存入的地址00000001,LDAR和WE都置为1,打开SW-BUS,点击P2,观察到中间一排灯泡仅最后一个点亮,即操作无误;关闭SW-BUS,调节SW7~SW0为存入的数据00010001,打开SW-BUS,然后打开CE,点击P1,可以观察到上面一排灯泡为00010001,1为亮0为暗(如图8所示),即操作无误,关闭CE,关闭SW-BUS。重复上述过程直至全部存入[11]。

在图8中可以看到中间一排灯泡仅最后一个点亮(操作无误),上面一排灯泡为00010001(1为点亮0为灭,操作无误),存入正确。

2)读操作仿真。以读取11H为例仿真读操作,接着以上1)中最后存入的继续,此时SW-BUS处于关闭状态。调整SW7~SW0为00000001,然后打开SWBUS,点击P2,打开CE和WE,观察到上面一排灯泡的点亮状态,然后关闭CE和SW-BUS。重复上述过程,直至完成所有数据的读操作[12]。

4 结束语

本虚拟实验系统基于JavaScript开发了许多数字逻辑组件,大致分为4类:1)74LS181、RAM等芯片器件;2)与、或、非、异或等各种逻辑门电路;3)开关、小灯、单脉冲和连续脉冲等基本元件;4)为了屏蔽电路细节或实现电路简洁,将多个功能部件封装为一个组件而成的各种虚拟组件,譬如时序电路组件、EPROM2716。在此基础上,设计了计算机组成原理课程实验中的多个模块并进行了仿真实验,譬如全加器、运算器、微控制器等[13]。新冠疫情期间,配合实物实验箱,部分模块已用在了中国民航大学计算机专业的计算机组成原理课程中。实践证明,通过开发系统,大大提高了学生的分析解决问题能力和创新能力;在实际教学中应用仿真实验,能有效提高学生的学习热情和学习积极性,收到了事半功倍的学习效果,受到了学生的极大欢迎。

同时,基于JavaScript的开发平台也存有一些不足,譬如芯片数量有限,如果在实验过程中发现芯片短缺时,还须重新设计;通过VML设计的连线也有一定的局限性,对于较复杂的实验,连线很多会很乱,没有优化机制。

另外,系统开发也参考了https://blog.csdn.net/qq_51314467/article/details/124159657 和https://blog.csdn.net/qq_51314467/article/details/124733329网站的相关内容,在此一并表示感谢。