一种基于FPGA的应急动力装置控制单元超转保护系统设计

2023-05-30黄新阳程旭喻鸣

黄新阳 程旭 喻鸣

摘要:提出一种基于现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)的超转保护系统设计方案。该系统采用三余度采集、控制架构,通过软件及逻辑表决控制单元及BIT检测单元,进一步提升了超转保护系统的可靠性。相较于传统的基于CPU的转速采集系统,其具备并行处理、运算速度快、功耗低、实时性强等特点,同时能释放大量CPU资源。该设计具备较强的通用性和实用性,对应急动力装置电子控制单元的超转保护系统设计具有一定的参考借鉴意义。

关键词:应急动力装置;超转保护逻辑;BIT设计

中图分类号:TP391.4 文献标志码:A 文章编号:1671-0797(2023)10-0042-04

DOI:10.19514/j.cnki.cn32-1628/tm.2023.10.012

0 引言

应急动力装置是以燃料分解产生的热燃气或发动机引气为动力源的涡轮动力装置[1],由涡轮、燃烧分解室、燃料箱、齿轮箱及控制部件组成,可以在发动机故障、主电源故障或主液压源故障时,通过开关指令快速启动,为飞机提供应急电源和液压源[2]。为了保证涡轮动力装置及其负载的安全可靠运转,必须可靠地监测涡轮轴转速,并据此快速、准确地控制相应执行机构的开关时机或开度大小,以保证涡轮轴转速稳定在允许范围内[3-4]。

超轉保护功能作为应急动力装置必要的安全功能之一,是实现转速稳定控制的前提保证。本文提出了一种基于现场可编程逻辑门阵列的超转保护系统,通过设计多通道并行采集、软件与逻辑独立、并行控制及BIT测试功能,具备高可靠性、强实时性等特点,可保证在超转故障初期进行有效的隔离保护,从而降低单点故障和共模故障造成的应急动力装置转速控制失效的风险,避免造成涡轮装置结构损伤及飞行安全[5]。

1 超转保护系统架构

超转保护系统架构设计中采用三余度独立转速采集和控制架构,原理架构如图1所示。

其中,CHA和CHB两通道分别应用于两路相互独立的转速传感器输出信号的采集,均可实现独立转速采集及BIT监测功能,并通过软件实现外部执行机构的切换控制,最终实现转速稳定控制。第三路CHC通道应用于独立于前两路转速传感器输出频率信号的采集,同样可通过FPGA实现独立转速采集及BIT监测功能,在软件控制失效时,能替代主控单元实现外部执行机构的切换控制,最终控制应急动力装置转速稳定在某个预期的控制区间内。

2 转速信号测量

2.1 转速采集调理电路设计

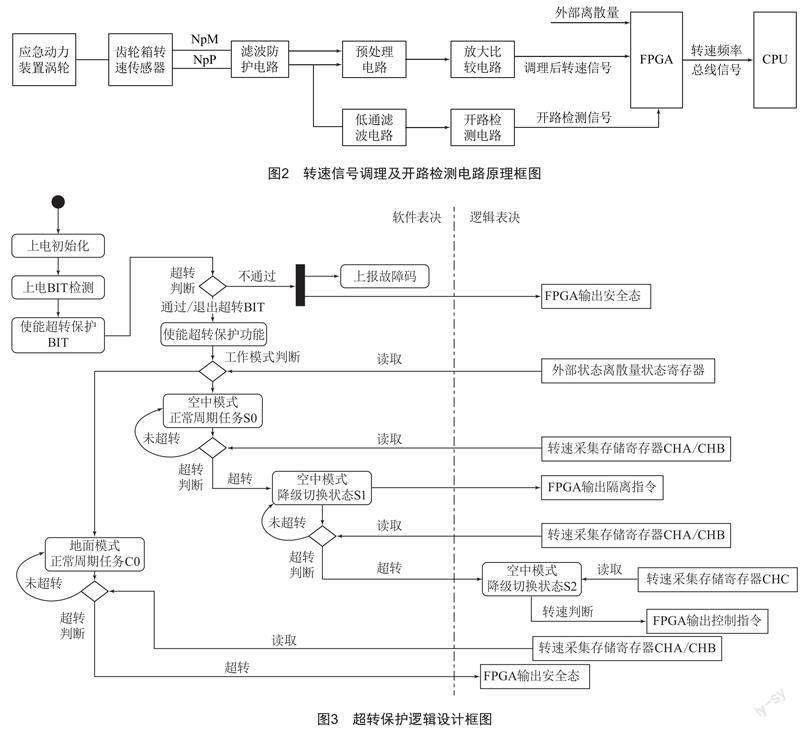

对转速信号的采集、调理和解析是超转保护系统设计实现的基础,转速采集调理电路由低通滤波电路、预处理电路、放大比较电路组成,单通道转速信号采集原理及开路检测原理框图如图2所示。

转速采集原理是将转速传感器频率信号首先通过滤波电路滤除外部高频干扰信号。随后,通过预处理电路将转速信号调理成一定幅值的非标准正弦波,可以防止当转速较高时,过高的输入信号将电路损坏。最终,通过放大电路将信号调理放大送入比较电路,将类正弦的转速信号调理成与转速传感器输出同频的方波信号,并送入FPGA进行采集测量。

2.2 FPGA采集功能设计

考虑到应急动力装置齿轮箱齿轮的工艺特性,在FPGA中采用高频脉冲计数法实现转速频率的采集,并设置采集的频率量范围下限。高频计数法的原理是采用高频脉冲对以多个转速脉冲为周期的脉冲群进行计数,并将结果存入寄存器,由CPU对脉冲计数进行读取解算,并与频率量范围下限进行比较判断,确认为有效频率后,得出最终采集频率。

同时,考虑到频率输入信号的高频干扰和涡轮转速的变化特性,在对脉冲群进行计数的同时,同步对脉冲群中每个脉冲进行单独采集,将同周期范围内差异较大的脉冲计数剔除,提高频率采集的抗干扰能力。

3 超速保护逻辑设计

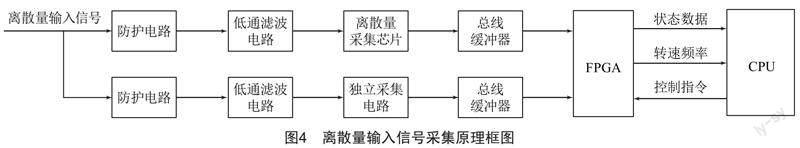

在控制单元完成BIT检测后,由CPU配置FPGA寄存器使能超转保护功能,超转保护逻辑设计框图如图3所示。

当软件判断为地面模式时,由软件进行表决,且当采集到CHA和CHB两通道任一转速超过阈值时,则CPU控制FPGA将外部执行机构置于安全态并锁定,超转保护系统进入锁定状态,实现输出保护;FPGA作为频率采集单元,同步执行转速监测功能,当发现超过软件保护阈值仍未收到保护指令时,则超转保护系统同样将外部执行机构置于安全态并锁定,实现输出保护。以上两种工况下,非控制单元下电或外部手动复位不可清除锁定状态。

当软件判断为空中模式时,由软件进行表决,且当采集到CHA和CHB两通道任一转速超过阈值时,则CPU控制FPGA对外部执行机构进行不可逆的切换控制,实现降级控制,隔离外部执行机构故障。此时,控制指令不会被锁定。切换控制后,若CHA和CHB两通道任一转速仍超过阈值,则FPGA不再读取MCU向寄存器发送的控制指令,由FPGA进行表决,依据CHC通道采集的转速频率,独立开展外部执行机构的控制功能,使应急动力装置运行在既定的转速范围,实现应急动力装置转速的切换控制。

4 BIT功能设计

机内自测试(Build In Test,BIT)技术,作为机载电子设备进行故障检测、隔离的重要手段,能够通过对系统内部软硬件的连续性监测和故障检测,提高机载电子设备可测试性,减少设备维护费用。对于超转保护系统来说,BIT功能设计主要包括采集电路BIT设计、控制状态离散量BIT设计、保护逻辑BIT设计三部分。

4.1 采集电路BIT设计

采集电路作为转速控制功能实现的基础,对三通道转速采集电路均设计开路检测BIT功能。将EMI滤波器后的频率信号端与电源分压接入比较器,当外部发生开路故障时,频率信号正端接近于电源电压,此时电压比较器正端大于负端电压,比较器输出1;当外部未发生开路故障时,由于开路检测通道上的低通滤波电路将比较器正端的交流信号幅值衰减到很低,此时比较器输出为0,从而实现开路检测功能。

4.2 控制状态离散量BIT设计

转速控制离不开准确可靠的外部状态离散量采集系统,本文所描述的超转保护系统分别采用集成离散量输入/输出接口芯片和独立离散量采集电路对涉及状态控制的离散量输入信号进行独立采集,并由FPGA送入CPU进行软件表决,采集原理如图4所示。此外,考虑到测试性设计,在硬件PCB布板时进行了分立布局设计。

4.3 保护逻辑BIT设计

超转保护逻辑BIT用于检测整个超转保护系统逻辑功能是否正常。由CPU通过硬线使能BIT功能,通过总线向转速采集测试寄存器写入预设转速,触发超转保护逻辑,由FPGA输出预设的外部执行机构控制指令。通过对执行机构驱动输出BIT及执行机构驱动回路电流回采,判断超转保护逻辑是否能够有效运行。当超转保护逻辑完成BIT检测后,由CPU通过总线寄存器使能FPGA应急动力装置超转保护功能,周期BIT中则不再进行保护逻辑BIT测试。

5 功能验证

当判定为地面模式时,测试設备仿真波形如图5所示。当启动至转速稳定后,通过外部注入超转故障信号后,控制单元将外部执行机构置于安全态并锁定,可以看出此时转速快速下降且外部执行机构不因转速下降到开启阈值而重新开启,依然保持锁定状态,从而验证了地面模式的锁定功能。当使能设备上的手动复位后,控制单元重新使能控制指令,使转速重新稳定到预设控制范围内。

当判定为空中模式时,测试设备仿真波形如图6所示。当启动至转速稳定后,首次注入超转故障信号后,使能超转保护逻辑的切换控制逻辑,外部执行机构的控制对象发生变化,保持转速稳定在预设控制范围内。当再次注入超转故障后,可以看到控制单元控制外部执行机构运行在规律的控制逻辑中,与设计的逻辑规律一致,可满足系统的设计要求。

6 结语

本文针对基于传统CPU的超转保护系统的不足,提出了一种基于FPGA的应急动力装置控制单元超转保护系统的设计,通过高抗干扰的转速采集方法和基于软件、硬件、逻辑的BIT检测方法,进一步提升了系统的可靠性和安全性,并具有较强的通用性和实用性,对应急动力装置控制单元超转保护系统的设计具有一定的借鉴意义,可结合系统实际,经过必要的裁剪加以应用。

[参考文献]

[1] 王浩,杨恒辉,卢玉芳.飞机第二动力系统技术综述[J].信息系统工程,2014(4):38-39.

[2] 张莹.辅助动力装置全权限数字电子控制技术研究[D].南京:南京航空航天大学,2007.

[3] 江群,王道波,李猛.涡轮动力装置闭环仿真试验器的设计与应用[J].燃气涡轮试验与研究,2010,23(1):55-58.

[4] 钱小娟.组合动力装置控制技术研究[D].南京:南京航空航天大学,2009.

[5] 兰先一,黄佑,黄平,等.液压系统对应急动力装置的影响及对策[J].机床与液压,2008,36(12):203-204.

收稿日期:2023-02-10

作者简介:黄新阳(1990—),男,陕西西安人,硕士研究生,工程师,研究方向:计算机应用。