基于CPCI总线技术的相控阵天线测试系统设计

2023-04-07宋云霞刘永涛黄田韵

宋云霞 刘永涛 黄田韵

(1.中国电子科技集团公司第38研究所 合肥 230088;2.孔径阵列与空间探测安徽省重点实验室 合肥 230088)

0 引言

随着电子技术的发展和整机功能的需求增加,相控阵天线的规模越来越大、工作模式越来越复杂。在所有整机产品的研发过程中,为了能够对大规模、多模式控制的相控阵天线系统的设计性能进行全面测试,需要设计一种通用可扩展的相控阵天线测试系统,能够对相控阵天线阵面的功能指标和相位一致性等进行检测,故基于CPCI总线技术的相控阵天线测试系统便应运而生。该测试系统以CPCI机箱为测试设备组成的载体,通过CPCI总线实现板间信息高速交互,由波控计算机产生原始控制参数和全阵控制码值,波束控制板接收波控计算机的控制信息,产生控制时序和相应天线子阵单元的控制码,整个测试系统与暗室测试设备进行同步交互完成闭环测试,从而实现对相控阵天线如内定标、单个收发组件定标态、多个波位等工作模式[1]的全面性能测试。本文详细描述了相控阵天线测试系统的软硬件设计实现,并说明工程设计的实际应用验证情况。

1 测试系统的原理说明与组成设计

相控阵天线是相控阵雷达的核心组成部分,通过控制相控阵天线波束的指向变化来进行电子扫描。大量的辐射器(小天线)组成天线子阵单元,每个辐射器都有一个可控移相器,每个移相器都由控制码值来控制,通过控制码值改变天线孔径上的相位分布来实现波束在空间的扫描,从而完成相控阵天线的工作[2]。

根据天线原理可知,为了在(θB,φB)方向上获得波束能量的最大值,应有

(1)

(2)

其中λ为雷达射频信号的波长;d1、d2为阵列天线方位向和俯仰向的单元间距;(θB,φB)为天线波束指向方位角、俯仰角。系统工作时只要按照式(1)和式(2)的要求控制各个收发组件移相器的移相读数来改变“阵内相位差”β和α,即可实现相控阵天线波束的两维电控扫描。

根据两维矩形栅格相控阵天线原理,可使公式(1)、公式(2)线性简化为

C(m,n)=mα(θ,φ)+nβ(θ,φ)+Δ(m,n)+α0

(3)

式(3)中,m和n分别为该天线单元的行、列序数;Δ(m,n)为修正值;α0为初始相位值。从公式(3)可以看出,对于每一行(列)的收发组件而言,除去移相基准值后,对应任何一个波位的波控数据都是呈简单的线性递增关系[3-4]。

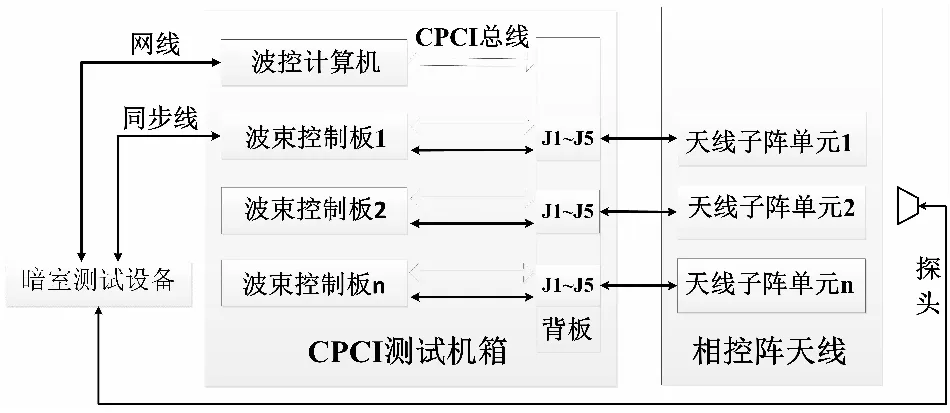

根据上述相控阵天线波束指向的原理说明,大规模相控阵天线测试系统的设计与硬件组成如图1所示,系统的硬件设备由CPCI测试机箱、波控计算机和多个波束控制板等组成,与波控计算机和多个波束控制板内运行的测试软件构成整个相控阵天线测试系统。暗室测试设备通过网线与波控计算机通信,确定测试时机,并通过暗室探头接收相控阵天线形成的波束信号进行解析处理;波控计算机接收暗室测试设备下发的工作指令开展测试工作,产生天线测试的控制参数和全阵控制码值,并通过CPCI总线传输给波束控制板;波束控制板完成CPCI总线传输的数据协议解析,产生控制码和控制时序,接收暗室发送的控制码刷新和时序同步等信号,完成与暗室交互控制的功能。CPCI总线具有高速并行和一主多从等优点,使用CPCI总线设计技术可使波束控制板具备互换性[5];波束控制板的数量越多则天线阵面测试单元数量越多,能够测试的相控阵天线的规模就越大;根据所选CPCI机箱的插槽数,可确定所承载的波束控制板的最大数量,也可以使用多个CPCI机箱及其设备实现测试系统的级联扩展。

图1 相控阵天线测试系统的原理设计与硬件组成

2 测试系统的各组成部分设计

2.1 波控计算机的主要功能设计

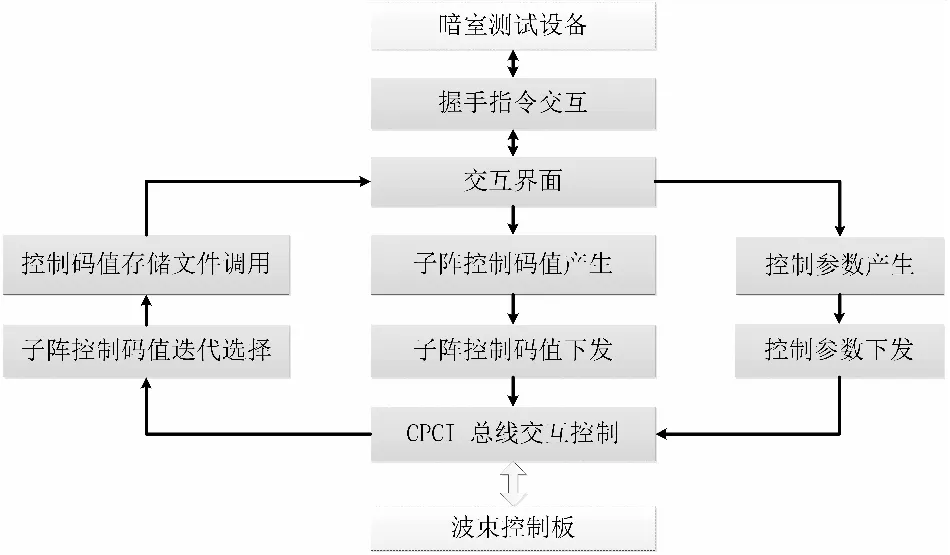

波控计算机的硬件设计是选用32位总线的通用CPCI计算机板卡即可,其操作系统环境为windows7 32bit,软件开发环境为QT4.8+VS2008,在波控计算机上主要进行相控阵天线测试软件的设计开发,实现天线时序/使能和工作模式等控制参数,以及天线幅度和相位等控制码的计算产生,再通过CPCI总线发送给波束控制板。波控计算机的软件设计流程如图2所示。

图2 波控计算机软件设计流程

波控计算机软件模块的主要功能设计如表1所示。

表1 波控计算机软件设计实现的主要功能

2.2 波束控制板的设计实现

2.2.1 波束控制板的硬件设计

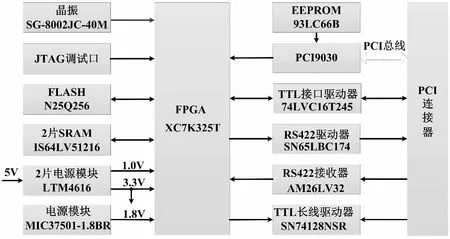

波束控制板的硬件设计如图3所示,以Xilinx K7系列FPGA为核心控制芯片,外围包括CPCI总线PCI9030桥片、EEPROM配置芯片、NOR型FLASH存储配置芯片、JTAG调试口、 SRAM芯片、TTL接口驱动器、RS422驱动器、RS422接收器、TTL长线驱动器、电源模块和PCI连接器等器件组成。其设计原理是CPCI总线桥片PCI9030解析CPCI总线协议,接收波控计算机发送的控制参数和控制码值等写入FPGA芯片,并读取FPGA芯片内容发送至波控计算机的功能;EEPROM配置芯片完成了PCI9030桥片的上电配置,完成CPCI总线设备信息及存储信息区间划分等配置;晶振芯片SG-8002JC-40M为FPGA提供40M时钟,在FPGA内部进行分频或倍频给FPGA电路提供所需时钟;FLASH芯片N25Q256用来存储FPGA的配置信息和应用程序,在波束控制板上电后,FPGA主动读取FLASH信息调用配置信息并启动应用程序;2片LTM4616电源芯片采用并联工作模式,提供5V电源转1.0V/16A和3.3V/16A电源供FPGA芯片和波束控制板上相关芯片使用,MIC37501-1.8BR提供3.3V转1.8V/5A电源供FPGA芯片使用;2片SRAM存储器IS64LV51216并联使用,其为FPGA提供512K的32位存储空间,存储相控阵天线波控码,解决了FPGA内部存储空间不足的问题;TTL长线驱动器SN74128NSR输出TTL同步信号与暗室测试设备进行交互,其它各接口驱动器完成子阵面工作信号的接收驱动和转换等功能;PCI连接器装配在波束控制板上,通过CPCI机箱背板,完成与波控计算机的信息交互。

图3 波束控制板的硬件设计

2.2.2 波束控制板的软件设计

相控阵天线测试系统实现相控阵天线的内定标、单个收发组件定标态和多个波位等工作模式测试,其中内定标对相控阵天线中组件的全状态进行测试,单个收发组件定标态对单个组件进行基态测试,多个波位对相控阵天线进行方向图测试,具体实现是由波控计算机下发不同的控制码来控制组件状态,配合暗室测试设备的同步信号,由暗室探头采样完成闭环测试。波束控制板的FPGA软件功能设计流程与软件功能模块组成如图4所示。

在硬件实现的基础上,根据测试需求进行软件开发,实现相控阵天线的测试。FPGA软件开发在Xilinx ISE14.7工具上进行,内部划分为6大功能模块包括波控计算机与FPGA地址交互、时钟产生、FPGA读写、遥测、SRAM存储器读写、控制码及遥测请求产生和控制时序产生等模块[6],具体FPGA内部模块功能实现如表2所示。

图4 FPGA软件功能设计流程与软件功能模块组成

表2 FPGA内部模块功能实现

3 测试系统的应用验证

在实际应用验证中,某相控阵天线全阵面共有600多个收发组件组成7个子阵单元,使用了本文所述测试系统进行性能指标测试,测试系统使用1个波控计算机板、7个波束控制板,测试了内定标、单个收发组件定标态、多个波位三种工作模式,设置了重频周期800~2500Hz、系统时钟频率3M/4M/5M,多种极化交叉时序等参数,完成了驻波小于1.4、辐射效率大于85%、远场交叉极化小于-25dB、接收增益大于40dB、单通道发射输出功率大于2W等天线性能指标的测试,全面验证了测试系统的设计功能,达到了相控阵天线性能测试的目的。

在设计验证中,同步握手设计非常重要。在首次对单个收发组件定标态测试时,出现暗室探头与测试组件的位置偏差,经过查验发现是控制码的下发和暗室测试设备的同步信号处理不匹配的问题,导致暗室探头的采样位置和控制通道位置不匹配,解决方法是波束控制板对接收的暗室同步信号进行计数,同时波控计算机从波束控制板回读计数,再根据回读的计数下发对应的控制码值,进而形成控制码值和同步信号以及暗室采样探头的同步,解决了测试组件位置偏差的问题。

4 结束语

本文以实际工程应用案例为依托,针对基于CPCI总线技术的相控阵天线测试系统进行了设计说明,介绍了相控阵天线测试系统的组成,说明了波控计算机软件的工作流程,详细描述了以FPGA为核心的波束控制板的硬件设计以及FPGA软件模块的设计流程与功能实现,并阐述了工程设计过程中的问题解决方法。通过工程设计和应用验证,该测试系统的设计具有一定的实际应用价值,可以对大规模、多模式控制的相控阵天线进行性能测试。