基于EDA 技术的常用串口通信总线接口逻辑设计

2023-04-06杨奇,刘红,李斌

杨 奇,刘 红,李 斌

(昌吉学院 能源与控制工程学院,新疆 昌吉 831100)

0 引言

通信总线是设备之间进行交互的关键装置之一[1]。但是,不同种类的通信总线具备不同的传输协议,致使其对应的接口属性也存在着较大的差异性,无法直接连接或者兼容应用。近年来,国内计算机、微电子、网络与通信等技术发展速度飞快,远距离数据传输需求逐渐增多,相较于并行传输模式来看,串行传输模式应用线路较少,被广泛应用于设备通信过程中。随着串行传输模式的不断发展与应用,串口通信已经成为计算机领域内常用的通信协议之一。

为了满足新兴技术的发展需求,不同设备之间的交互活动显著增多,对通信总线接口性能提出了更高的需求[2]。现有接口由于多种因素的局限,使得接口存在兼容性较差、经济成本较高、传输速度较慢、同步性较差等问题,制约着串口通信总线的应用与发展。简单的完善与修改无法明显提升接口的整体性能,故提出基于EDA 技术的常用串口通信总线接口逻辑设计,希望通过EDA 技术的引入与应用,改善接口的传输性能、兼容性能等,降低接口的经济成本,为串口通信总线的发展提供助力。

1 常用串口通信总线接口逻辑设计

1.1 接口逻辑设计框架搭建

根据常用串口通信总线接口完善需求,引入EDA技术搭建接口逻辑设计框架,为后续接口设计奠定坚实的基础[3]。

EDA 技术全称为电子设计自动化技术,其主要应用步骤如下所示:

步骤1:行为级描述。根据常用串口通信总线接口功能与性能需求,对接口整体电路进行设计与描述,实现设计接口的行为级描述。

步骤2:行为级优化。对上述步骤实现的设计接口行为级描述结果进行优化处理,主要通过适当的算法实现,并对其所需功能进行仿真验证。与此同时,由于EDA 工具只能够对RTL 级描述进行读取与处理,还需要将行为级描述转化为RTL 级描述。

步骤3:确定约束条件,完成逻辑优化。约束条件指的是接口设计指标——驱动能力、芯片面积等,以此为基础,对步骤2 获取的RTL 级描述进行映射处理,关联逻辑设计与实现器件,执行工艺操作实现逻辑设计的整体优化。

步骤4:门级仿真。门级仿真应用了仿真库、门单元延时信息、相应工艺等,对逻辑设计内容进行仿真验证,依据工艺参数选取最佳的门单元,实现门级仿真的最佳化。

步骤5:布局布线。布局布线工具主要由FPGA 控制器提供,其是EDA 技术实现的关键器件之一。

步骤6:写片与测试。将步骤5 获取的布局布线文件传输至设计接口芯片上,完成写片过程,并对设计好的串口通信总线接口进行性能测试,保障接口的可靠性与可行性[4]。

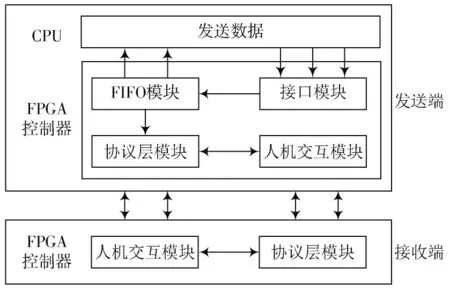

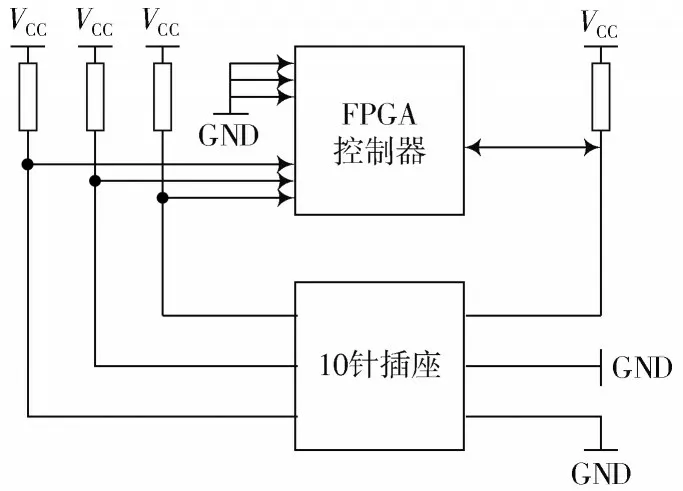

基于上述介绍的EDA 技术应用流程,搭建接口逻辑设计框架,具体如图1 所示。

图1 接口逻辑设计框架示意图

上述过程完成了接口逻辑设计框架的搭建,为后续接口逻辑设计、实现器件的选取提供支撑。

1.2 接口逻辑设计实现器件选取

以上述搭建的接口逻辑设计框架为依据,选取适当的实现器件,其是EDA 技术应用的关键所在,也是接口逻辑设计的主要环节之一。实现器件是接口配置文件的载体,根据常用串口通信总线接口逻辑设计需求,选取FPGA 控制器作为实现器件。

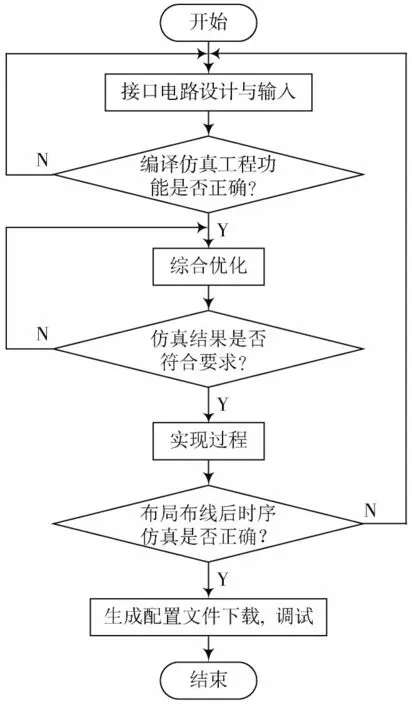

FPGA 控制器具有可重复编程的优势,可以实现复杂的逻辑设计,符合接口逻辑设计的需求[5]。但是,在FPGA 控制器应用过程中,还需要对其进行针对性设计,使其更加符合研究目标实现要求[6]。依据接口设计需求,制定FPGA 控制器设计流程,具体如图2 所示。

图2 FPGA 控制器设计流程图

综上所述,完成了接口逻辑设计实现器件的选取与设计,为后续接口的具体设计提供帮助。

1.3 接口具体设计

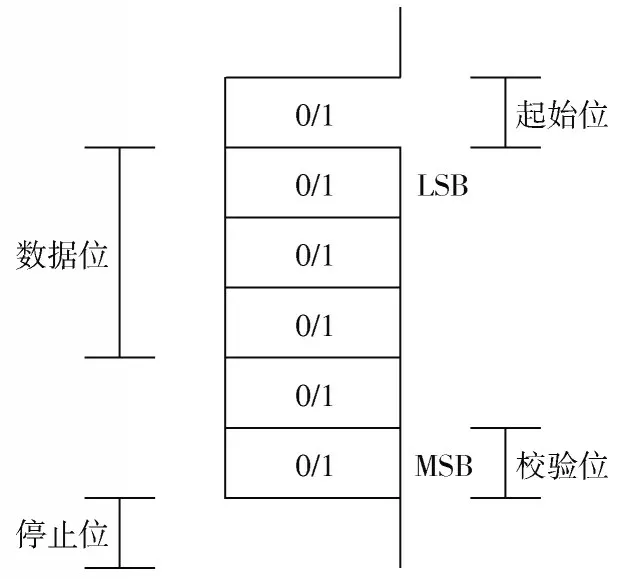

以上述选取的接口逻辑设计实现器件——FPGA控制器为工具,设计具体数字接口,其主要由RS 232 接收模块、I2C 接收模块与SPI 接收模块构成[7]。其中,RS 232 接收模块主要是对RS 232 数据模式进行接收。RS 232 数据帧格式如图3 所示。

图3 RS 232 数据帧格式示意图

由于通信双方(LSB 与MSB)具备独立时钟,使得RS 232 数据接收精度受到了一定的影响,需要对时钟频率、分频系数进行确定,以此来保障RS 232 数据接收的准确性[8]。其中,时钟频率指的是RS 232 串行驱动时钟运行的参数,表达式为:

式中:fa表示RS 232 串行驱动时钟频率;fb表示标准波特率时钟频率;M表示fa与fb之间的倍数;βo表示辅助运算参数,取值范围为[0,1 ]。

分频系数是调整通信双方时钟频率的关键参量,计算公式为:

式中:ξ表示分频系数;fc表示设计接口时钟频率数值。

依据公式(2)的计算结果对通信双方时钟频率进行合理调整,使两者保持一致,保障RS 232 数据接收的质量。

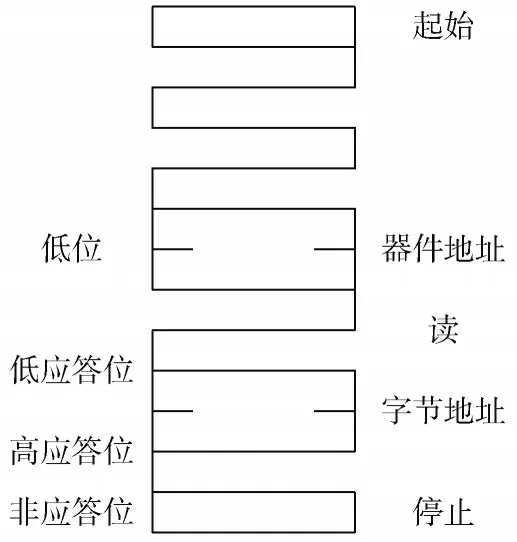

I2C 接收模块主要对开始、应答与结束三种类型信号进行传送与接收[9]。I2C 数据传输时序如图4 所示。

图4 I2C 数据传输时序示意图

如图4 所示,当SCL 逻辑为1 时,SDA 逻辑由1 变为0,起始信号变得有效,数据传输开启;当SCL 逻辑为0时,SDA 逻辑由0 变为1,停止信号变得有效,数据传输结束。需要注意的是,数据发送过程中,应该在SCL 变成高应答位之前就准备好数据[10]。

SPI 接收模块整体呈现为一个环形结构,内部包括两个双向移位寄存器,通过时钟脉冲SCLK 对数据交换进行控制[11]。由于研究篇幅的限制,不对SPI 接收模块结构进行过多的赘述与展示。

上述过程完成了接口的具体设计,为接口多种性能的稳定发挥提供支撑[12]。

1.4 接口协议层设计

接口协议层设计的优劣直接决定着设计接口的功能能否正常应用,其关键环节为数据接收前端处理,主要功能为CRC 校验、NRZI 解码与去除位填充,具体流程如下:

步骤1:设置接口输入数据格式为data_in(13:0),采用CRC 校验模块对输入数据进行整体校验。若检验结果为错误,表明输入数据错误,此时将finish 设置为低电平,提示信息error 设置为高电平,并将提示信息error反馈给发送端;反之,若检验结果为正确,表明输入数据无错误,此时将finish 设置为高电平,提示信息error 设置为低电平,转至步骤2。

步骤2:对CRC 校验结果正确的输入数据进行校验码(五位)去除处理,剩余数据记为rdata(8:0),将其传输给NRZI 解码模块。

步骤3:NRZI 解码模块对rdata(8:0)进行相应的解码作业,获取输入数据,记为new[rdata(8:0)]。

步骤4:在去除位填充模块中读入new[rdata(8:0)],将去除的校验码(五位)补充回来,即可获得数据接收前端处理最终结果data_out。

综上所述,应用EDA 技术实现了常用串口通信总线接口的逻辑设计,改善了接口整体性能,为多种设备通信提供了有效的帮助[13]。

2 常用串口通信总线接口性能测试

选取基于高速串行总线的分布式RS 485 串口通信接口设计[14]与基于FPGA 和DSP 的GNSS 总线通信接口设计[15]作为对比接口1 与接口2,设计常用串口通信总线接口性能对比测试,以此来验证设计接口的整体性能。

2.1 设计工具选取与介绍

为了保障实验的顺利进行,选取科学的、适当的设计工具,并对其进行统一配置,提升实验结论的精确性。依据常用串口通信总线接口性能测试需求,选取MAX+PLUSⅡ软件作为设计工具,具备功能全面、操作便利等优势,是现今应用较为广泛的大众化EDA 平台。MAX+PLUSⅡ软件优势如下:

1)具备集成化界面,提供了设计输入、处理、校验等开发工具,并能够对其进行动态调试,最大限度地缩短接口设计与开发的时间。

2)支持多种HDL 语言,例如AHDL、VHDL 等。

3)具备较强的数据互换性与开放性,能够与其他工具进行直接链接,再加之参数化模块库的提供,可以从多个角度帮助用户去进行逻辑设计,简化接口逻辑设计过程。

4)具备模块组合式设计工具,并能够根据用户需求对设计工具位置等进行调换,使设计环境更加用户化,为用户提供最佳的服务体验。

在MAX+PLUSⅡ软件应用环境下,可以直接对实现器件——FPGA 控制器进行串行配置,具体如图5 所示。

图5 FPGA 控制器串行配置示意图

另外,根据设计接口的实际需求,选取适当的实现器件——FPGA 控制器,其相关参数为:

等效逻辑单元:2160;系统门:100 KB;分布式RAM:15 Kbits;最大I/O:108;最大差分对数:40;CLBS:240;DCMS:2;Block RAM:72 Kbits。

上述过程完成了设计工具的选取与配置,为后续实验的顺利进行提供便利。

2.2 接口性能分析

2.2.1 接口逻辑设计资源占用率测试结果分析

接口逻辑设计资源占用率可以侧面反映接口的经济成本情况。常规情况下,接口逻辑设计资源占用率越高,表明其设计经济成本越高;反之,接口逻辑设计资源占用率越低,表明其设计经济成本越低。接口逻辑设计资源占用率计算公式为:

式中:K表示接口逻辑设计资源占用率;Qs表示接口逻辑设计应用资源数量;Qtotal表示通信总线全部资源数量。

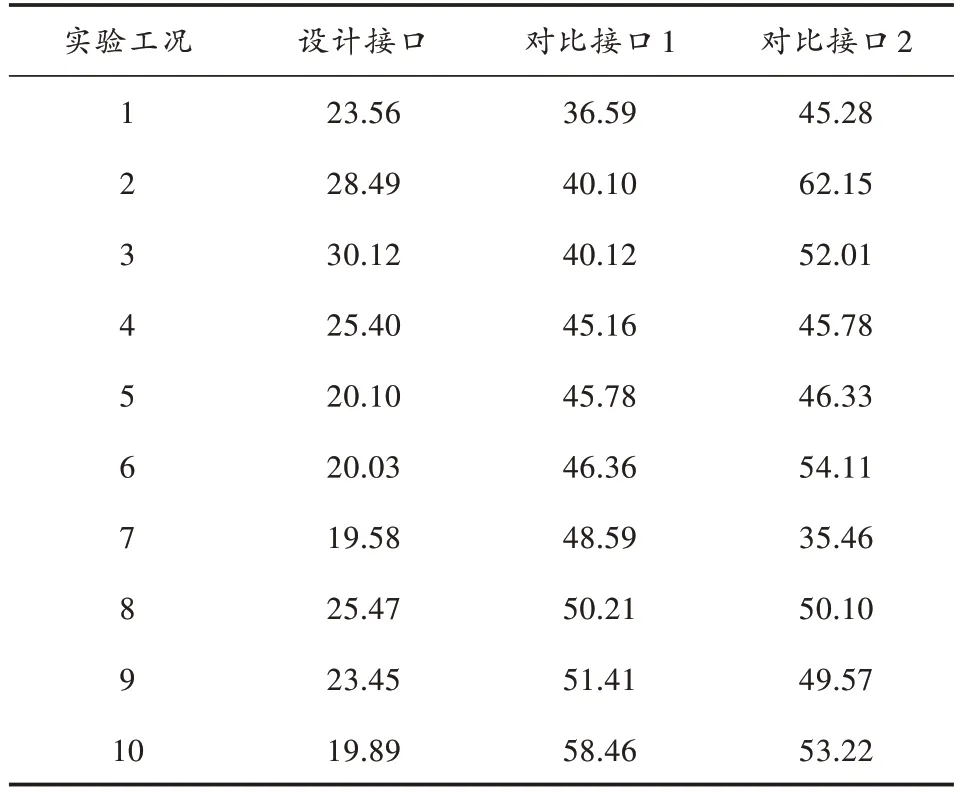

通过实验获得接口逻辑设计资源占用率如表1所示。

表1 接口逻辑设计资源占用率 %

如表1 数据所示,在不同实验工况背景下:设计接口资源占用率数值范围为19.58%~30.12%;对比接口1资源占用率数值范围为36.59%~58.46%;对比接口2 资源占用率数值范围为35.46%~62.15%。通过数据对比可知,设计接口资源占用率更低,表明其设计经济成本更低。

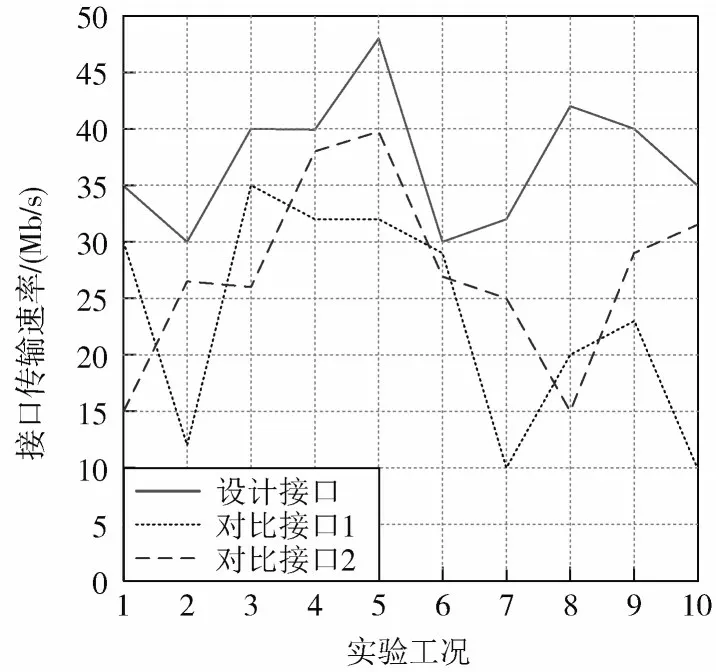

2.2.2 接口传输速率测试结果分析

接口传输速率是体现接口性能的关键指标之一,其与接口性能之间呈现着明显的正比例关系。通过实验获得接口传输速率数据,具体如图6 所示。

图6 接口传输速率示意图

由图6 可知:设计接口在第5 种实验工况背景下获得传输速率最大值48 Mb/s;在第2 种与第6 种实验工况背景下获得传输速率最小值30 Mb/s。通过线段高低位置可知,在不同实验工况背景下,设计接口传输速率均高于对比接口1 与接口2,表明设计接口传输性能更佳。

上述实验数据显示:相较于两种对比接口来看,设计接口资源占用率更低、传输速率更高,并且达到了预期的设计目标,证实了设计接口的可行性。

3 结语

伴随着网络技术的发展与普及,远距离数据传输需求急剧暴增,串口通信总线应运而生。通过调查研究发现,制约串口通信总线应用与发展的根本原因为接口性能,故本文提出基于EDA 技术的常用串口通信总线接口逻辑设计。设计接口大幅度地降低了资源占用率,提升了传输速率,能够为串口通信总线应用提供更有力的支撑,也为接口设计相关研究提供一定的借鉴。