基于以太网的FPGA 远程调试系统设计

2023-03-15钱雪磊韩留军邵春伟

官 剑,钱雪磊,韩留军,薛 培,邵春伟

(1.无锡华普微电子有限公司,江苏 无锡 214000;2.中科芯集成电路有限公司,江苏 无锡 214000)

0 引言

在工控领域,PLC 系统配套的远程在线调试技术已经非常成熟[1],而以FPGA 为核心的系统,市面上还未出现成熟的可远程在线调试的产品。当FPGA 系统出现故障时,依然需要工程师到现场分析与调试。而FPGA 动态可重构技术是实现远程升级和调试的一种可行方法。

FPGA 动态可重构指FPGA 内时序逻辑的发生不是通过调用芯片内不同区域和不同逻辑的资源组合实现的,而是通过对FPGA 全局或局部逻辑进行动态重构实现的[2],其主要分为全局动态可重构技术和部分动态可重构技术。

FPGA 动态可重构技术,有如下方法可实现:

(1)采用外围芯片,如ARM 或CPU,通过JTAG 或者selectMAP 接口对FPGA 进行动态重构[3]。该方法较灵活,但是系统中存在使用一个主控芯片,对成本、尺寸和功耗均有影响。

(2)采用FPGA 内置的MicroBlaze 或者ZYNQ 系列的ARM 对FPGA 进行全局动态重构[4]。该方法较灵活,成本较低,但是该方法为全局重构方式[5],对Flash 大小有限制,同时全局重构方式是采用存储于Flash update 空间中的bin 文件来完成FPGA 更新功能,该bin 文件所对应的待更新FPGA 程序为正式版程序,不适合远程调试时而使用的中间版调试程序。

(3)在特殊领域中,采用部分局部可重构技术,可实现FPGA 内SRAM 区域动态重构[6],以避免特殊环境中FPGA 可能发生的单粒子翻转而影响到FPGA 核心功能,但是其应用领域较狭窄,不适合本研究所处的工控领域[7]。

基于以上三种方法的优缺点,本文设计了基于以太网方式的FPGA 远程调试系统,实现了服务器端的远程调试和远程升级重构,成本较低,适用于网络中的FPGA设备。

1 系统架构

本系统中的设备是以Xilinx 7 系列FPGA 为硬件平台,整体架构如图1 所示。

图1 FPGA 远程调试系统架构

在图1 中,系统由FPGA、PHY 芯 片、Flash 芯片及DDR3 芯片组成。其中PHY 实现TCP/IP 以太网的物理层功能、DDR3 为FPGA 缓存芯 片、Flash 芯片为FPGA 程序存放的位置。FPGA 系统通过Internet 与工作服务器和远程服务器建立连接。

用户正常使用时,设备只与工作服务器保持连接通信;当用户需要厂家对设备维护而进行远程调试时,设备与远程服务器建立通信连接,并实现以下三个功能:

(1)远程重构数据注入:远程服务器通过Internet 下发部分动态可重构的bin 文件数据注入到FPGA ICAP(Internal Configuration Access Port)中,FPGA 部分模 块实时执行重构后的功能;

(2)调试数据上传:设备向服务器上传实时状态以便厂家调试设备,分析设备问题;

(3)远程升级:当厂家解决设备问题后,将最终版本的升级程序bin 文件通过Internet 下发到FPGA,FPGA 将文件更新到Flash 芯片中。

实现以上功能,则完成了一次完整的设备远程调试与维护的流程。

2 FPGA 设计

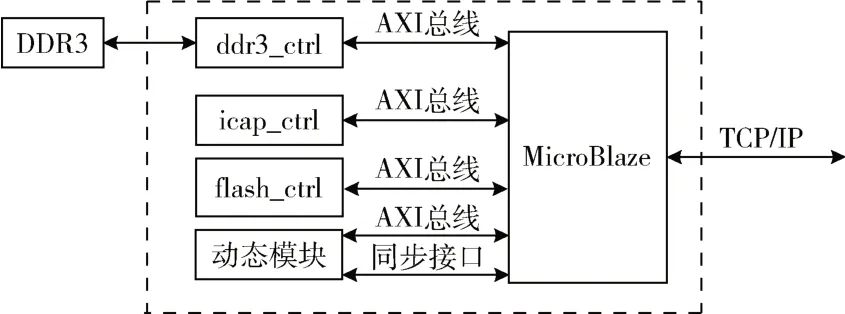

FPGA 主要由静态和动态两类模块组成,模块之间的通信通过AXI4 总线和同步接口来进行。图1 中的部分可重构模块即为动态模块,在远程调试和升级时可重构;除部分可重构模块外的FPGA 其他模块为静态模块,在远程调试和升级时不可重构。

FPGA 内部的子模块如图2 所示。子模块功能如表1 所示。

图2 FPGA 内部模块图

表1 FPGA 子模块功能表

2.1 重构文件生成流程

使用Vivado 的Partial Reconfiguration Wizard 工具可将两个或多个具有同样模块名称的HDL 文件在同一工程中实现[8],该工具所设定的HDL 文件即为动态模块,其内部可包含多个子模块。不同的动态模块在同一个工程中编译后会生成多个不同的下载bit 文件,这类bit只会对动态模块重构,对静态模块无影响。

在实际系统中,动态模块的区域约束是厂家通过预估动态模块所需要的LUT、寄存器、管脚、RAM 和DSP等资源大小来综合设定的。

工程编译完成后,将生成两类比特流:多个部分重配置(Partial Reconfiguration,PR)比特流和全功能(full)比特流。其中PR 比特流文件转换后的PR bin 文件即为本系统中用于动态模块重构的更新文件。full 比特流转换后的full bin 文件即用于全局模块重构的更新文件。

2.2 动态模块

动态模块含用户模块和同步接口模块。其中用户模块的核心功能设计在此文中不涉及,而由于模块动态重构的特殊性,需要考虑动态模块与静态模块之间的同步。因此系统设计了一个专门的同步模块以处理该问题。动态模块的接口框图如图3 所示。

图3 动态模块接口框图

用户模块与静态模块的接口包含两种接口:(1)与MicroBlaze 软核之间数据交互的AXI4 接口,主要用于接收远程注入指令和本地调试信息上传;(2)与静态模块数据交互的其他逻辑接口。在远程重构动态模块时,HDL文件的代码修改,动态模块的输入输出信号不能有任何的改变。

动态模块重构后,其逻辑会重新复位,此时系统设计了同步模块,以确保静态模块可以输出同步触发信号给动态模块,实现两个模块之间时间上的一致。其接口时序设计如图4 所示。

图4 同步逻辑模块时序

clk 信号为时钟信号,由静态模块提供,无论在更新PR bin 文件前、中、后的过程中,该信号状态均能稳定保持。

reset 信号为复位信号,与静态模块的主复位信号保持一致。

static_sync 信号为静态模式输出给动态模块的同步信号,该信号为周期信号,每隔8 个clk 信号输出1 个高电平。在更新PR bin 文件前、中、后的过程中,该信号状态均能稳定保持。

dynamic_sync 信号为动态模块输出给静态模块的同步信号,该信号与static_sync 一致,也为周期信号,其信号在static_sync 延后2 个周期。由于动态模块在重构过程中该信号处于未定态,如图4 所示,“启动动态模块可重构”到“动态可重构文件ICAP 更新成功”的时间内,该信号为0。该信号使静态模块可以获取动态模块的实时状态。

trigger 信号为静态模块输出给用户模块的触发信号,其信号只有当完成动态模块重构流程后,获取static_sync 后才会拉高,此刻用于触发用户模块时间同步开始。

基于以上设计的同步模块,可实现动态模块与静态模块之间的同步,确保用户模块的时间上保持一致。

2.3 静态模块

静态模块是为实现动态模块重构、全局模块重构和TCP/IP 以太网通信等功能而设计的确定性逻辑,含MicroBlaze、ddr3_ctrl 模块、icap_ctrl 模块、flash_ctrl 模块等模块。其中MicroBlaze 处理器实现各个模块与TCP/IP以太网数据的交互;ddr3_ctrl 模块为DDR3 读写缓存模块;icap_ctrl 模块为远程调试时PR bin 文件写入ICAP 的控制模块;flash_ctrl 模块为远程升级时full bin 写入到Flash 芯片的控制模块。

2.3.1 MicroBlaze 处理器

MicroBlaze 实现LwIP 协议栈,此协议栈在保持了TCP/IP 协议主要功能的基础上减少了对资源的占用[9]。FPGA 的动态重构和全局重构,均是远程服务器通过TCP/IP 将待更新的PR bin 文件和full bin 文件下发给FPGA 内部的MicroBlaze 软核,MicroBlaze 解析TCP/IP包后,按照包内计数器的顺序,解析出有效的数据,通过AXI4 总线把数据写入ddr3_ctrl 模块的DDR3 地址中,在确认MicroBlaze 收到最后一个PR bin 或者full bin 数据后,启动重构文件的下载。

2.3.2 ddr3_ctrl 控制模块

ddr3_ctrl 模块采用XILINX 提供的MIG IP,接口为AXI4 接口,通过AXI4-interconnect 互联模块实现与MicroBlaze 处理器连接。其实现的功能为:

(1)从以太网中接收的以太网包中解析出PR 数据bin 或full bin 文件,写入到DDR3 颗粒;

(2)从划分好的动态重构DDR3 地址读出动态模块重构bin 文件,按时序写入到icap_ctrl 模块;

(3)从划分好的全局重构DDR3 地址读出全局模块重构bin 文件,按时序写入到flash_ctrl 模块。

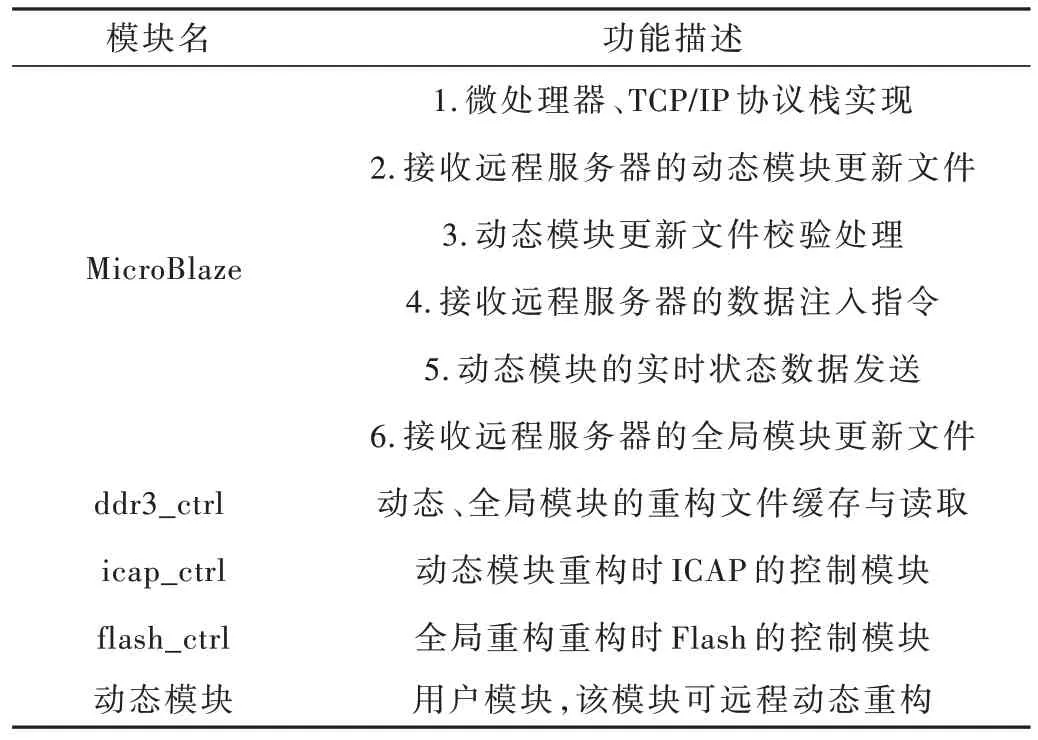

2.3.3 icap_ctrl 控制模块

动态模块的重构是通过部分动态可重构技术实现的。该技术采用CAP 原语的方式。

在Xilinx7 系列中,ICAP 即为实现该技术的原语,其功能与Selectmap、JTAG 等方式类似[10],区别在于ICAP是可以通过HDL 代码直接代码,方便集成到工程中。

ICAP 原语框图如图5 所示。

图5 ICAP 原语框图

其信号如下:

(1) O:配置数据的输出;

(2) CSIB:使能信号,低电平有效;

(3) CLK:时钟信号;

(4) I:原语配置数据的输入信号;

(5) RDWRB:读写使能信号,低电平有效。

icap_ctrl 设计为AXI4-lite 接口方式,其基地址为0x80000000。控制流程为:

(1) MicroBlaze 向地址0x80000000 写1 为启动ICAP动态模块更新;

(2) MicroBlaze 向地址0x80000004 写PR bin 文件数据(32bit);

(3) 写完所有的PR bin 文件内容;

(4) MicroBlaze 向地址0x80000008 写1 为bin 文件传输结束标志。此时MicroBlaze 完成了一次动态模块的重构。

2.3.4 flash_ctrl 控制模块

flash_ctrl 模块为当完成远程调试、进行远程升级时所使用的全局重构控制模块。本系统采用SPI Flash 存FPGA 全局重构文件。FPGA 的程序加载运行是通过读取Flash 中的数据进行的,Flash 包括3 个部分:Header、initial bitstream area 和update bitstream area。

全局重构的full bin 文件即通过该模块写入到update bitstream area 空间。该技术在此不详述,可参考文献[11]。

3 软核软件设计

3.1 MicroBlaze 主流程设计

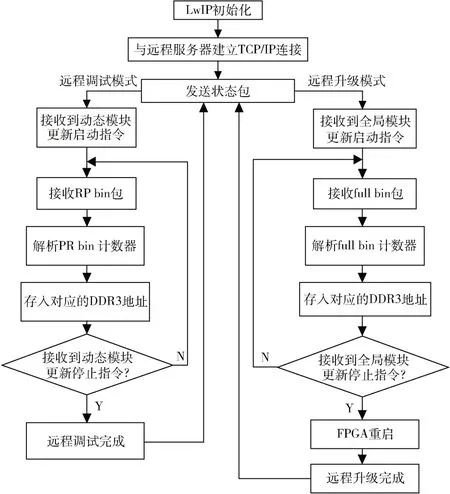

MicroBlaze 处理器的软件流程图如图6 所示。当设备进入到远程调试模式时,与MicroBlaze 远程服务器通过以太网建立起TCP/IP 连接。

图6 MicroBlaze 软核流程图

默认状态下,MicroBlaze 发送状态包(含动态模块的实时状态)到服务器端,服务器端显示设备的状态,并进行远程调试。

当设备端MicroBlaze 接收到服务器端动态模块更新启动指令后,进入到动态模块更新模式并接收PR bin 文件。MicroBlaze 接收到动态模块更新停止指令,接收完成,并从ddr3_ctrl 模块中读出存入的bin 文件,并发给icap_ctrl 模块,实现ICAP 的更新,更新完成后返回到默认状态。

当设备端MicroBlaze 接收到服务器端全局模块更新启动指令后,进入到全局模块更新模式并接收full bin 文件。MicroBlaze 接收到全局模块更新停止指令,接收完成,从ddr3_ctrl 模块中读出存入的bin 文件,并发给flash_ctrl 模块,实现Flash 存储内容的更新,更新完成后,控制FPGA 的PROGRAM 管脚,实现设备远程重启。

3.2 动态重构更新软件设计

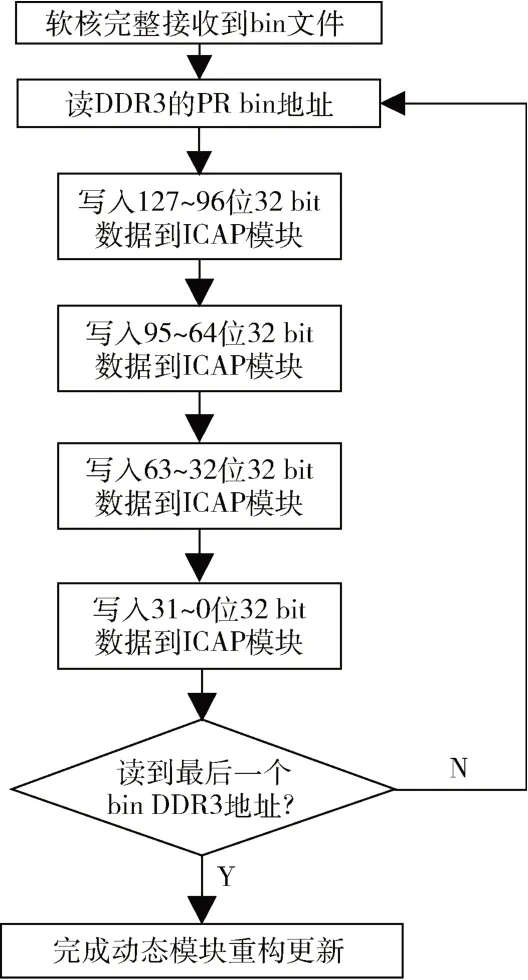

完 成PR bin 文件存DDR3 后,MicroBlaze 需要将 存在DDR3 中的bin 数据完整地通过icap_ctrl 模块下载到ICAP 中。该过程的软件流程图如图7 所示。

图7 动态模块更新流程图

MicroBlaze 通过读取DDR3 地址中的bin 数据,通过AXI4-lite 接口写入到icap_ctrl 模块。icap_ctrl 模块输入为AXI4-lite slave 接口,输出为ICAP 接口信号。

首先MicroBlaze 从DDR3 读出首地址中的数据,由于DDR3 中单地址读出的数据为128 bit,而ICAP 接口最大为32 bit 位宽,因此首地址的数据分4 次写入到ICAP 接口。完成后,响应ACK。MicroBlaze 继续完成后续DDR3 地址数据的读出。直到最后一个地址,即实现部分动态可重构bin 文件的更新。

3.3 全局重构更新软件设计

在完成full bin 存DDR3 的操作后,MicroBlaze 需要将存在DDR3 中的bin 数据通过flash_ctrl 下载到Flash存储芯片中的update 区域。该过程的实现如图8 所示。

图8 全局模块更新流程图

与icap_ctrl 软件控制流程类似,其差别在于完成bin数据更新后,MicroBlaze 需要重启FPGA,实现远程升级文件的生效。

4 远程服务器设计

远程服务器运行于带Internet 互联网的PC 或者服务器上,采用C++语言开发,其集成了服务器端的TCP/IP协议、自定义的数据收发和控制协议,通过Internet 网络,与FPGA 进行数据交互,实现远程调试,同时上位机集成有可导入PR bin、full bin 两种文件的控件,实现将文件通过网络传输到设备以完成FPGA 远程调试与升级。

当FPGA 系统接入网络时,连接上后的服务器页面如图9 所示。页面上显示的是IP 为172.16.1.10、端口号为5001 的FPGA 设备连上后的状态。

图9 远程服务器操作界面

当用户选择进行,选择更新界面,并选择更新的文件后点击升级按键,如图10 所示。

图10 设备远程更新过程中

服务器通过网络开始以包的形式下发bin 数据给设备,成功后,软核反馈更新后的状态给远程服务器,并显示到上位机。升级完毕后的页面如图11 所示。

图11 远程升级成功

远程调试页面显示为设备的状态信息,与设备的功能有关联,在此不展示。

5 结论

本文以Xilinx 公司7 系列FPGA 为研究对象,采用MicroBlaze 软核处理器,搭建了基于LwIP 的TCP/IP 协议栈,作为动态和全局可重构数据传输的通信方式。该方式不需要任何硬件状态的改变,只改变远程更新模块的功能,更新后立即生效并反馈到升级后的动态模块和全局模块实时的状态,方便地进行远程调试和远程升级[12]。

基于以上技术的远程调试系统可靠性高,可实现FPGA 资源的时分复用、动态调制[12],在人员无法流动的情况下,可方便地实现系统设备的远程维护。