基于VHDL 语言的序列发生器设计

2023-02-19江苏商贸职业学院焦鹏邓正万

江苏商贸职业学院 焦鹏 邓正万

在介绍了序列信号发生器的基础上,给出了利用VHDL 语言设计的具体方法。结合MAX+PLUS II 的波形仿真功能,验证设计的正确性。

1 序列信号发生器简介

数字信号采用二值信息“0”和“1”来表示两个相对的状态,如脉冲的有、无或电平的高、低。例如:若用“1”表示高电平,则“0”可表示低电平;若用“0”表示有脉冲,则“1”可表示无脉冲。数字电路中,“0”和“1”仅表示两种相对独立的状态,没有数值上的大小概念,在实际应用中,两个相对独立的状态可用电子器件的开关特性来实现,就是利用二极管、三极管、场效应管等元器件的开关特性,如完全导通表示一种状态,完全截止表示另一种状态。因此,数字电路的传输与信号处理无论在电路结构还是研究内容、分析方法均与模拟电路不同。

序列信号发生器,能够在时钟信号作用下,产生具有周期性的二进制信号,这类逻辑器件又称序列发生器,它是一种常见的数字电路。根据结构的不同,序列信号发生器可分为移位型序列信号发生器信号发生器和计数型序列信号发生器。前者是由若干移位寄存器和组合逻辑电路两部分构成,组合电路的输出信号,可以作为寄存器的输入信号;后者能够产生不同的序列信号,它是一种具有多种测量功能、多种用途的电子计数器。

序列信号发生器的构成方法有多种。其中,利用计数器和数据选择器组合实现就是常用的一种做法。具备数据选择功能的逻辑电路即数据选择器,它的作用是,选择相应的信号,并把处在不同通道的数据传送至公共数据通道,也称多路选择器或多路开关。例如,需要产生一组8 位的序列信号10110101,可使用八进制计数器和八选一数据选器实现。带反馈逻辑电路的移位寄存器也可以用于序列信号发生器的设计,但是,设计中选用的移位寄存器位数与序列信号的位数密切相关。若仍然要求产生10110101 这样一组8 位的序列信号,需要3 位移位寄存器和相关组合逻辑电路方可实现[1]。

2 EDA 技术概述

EDA 技术指的是以计算机硬件和系统软件为基本工作平台,结合多个学科的最新成果,开发而成的通用支撑软件,涉及了电子、数学、图论等多个领域[2]。其功能复杂,实用性强,代表了当今电子系统设计技术的最新发展方向,其自顶向下、从整体到局部的设计理念与设计平台的构建,为电子技术设计人员提供了更加方便、更加便捷的电子系统设计方法。随着高性能的电子芯片出现,人们对于先进的EDA 软件工具和芯片制造商开发平台需求日益旺盛。如今,EDA 技术已经成为众多电子设计工程师的必备技能之一。

EDA 开发工具通常由器件生产厂家提供,如拥有CPLD/FPGA 市场大量份额的Altera 公司和Xilinx 公司,都有专门针对各自公司芯片的开发平台。其中,MAX+PLUS II 是Altera 公司第三代开发工具,ISE 是Xilinx 公司推广的开发工具。

EDA 设计使用硬件描述语言对系统的行为、功能进行正确的描述。硬件描述语言作为一种电路设计的工具,它的使用与普通高级语言类似,首先经过编译器的语法、语义检查,接着,转换为某种中间格式。它们的区别是,用硬件描述语言编程的最终目的是要生成实际的硬件电路。

3 VHDL 语言

VHDL,超高速集成电路硬件描述语言,是最具推广前景的硬件描述语言。1994年,电子与电气工程师协会对其进行了修订,增加了部分新的命令与属性,增强了系统的描述能力,目前,VHDL 语言已经成为系统描述的国际公认标准,得到了众多EDA 公司的支持,越来越多的电路设计工程师采用VHDL 语言描述系统的行为。在各种硬件描述语言中,VHDL 语言的抽象描述能力最强,因此,用VHDL 进行复杂电路设计时,往往采用自顶向下分层设计的方法。首先,从系统功能设计开始,对系统的高层模块进行行为与功能描述并进行高层次的功能仿真,然后从高层模块开始往下逐级细化描述。它能形式化地抽象表示电路的结构和行为,支持逻辑设计中层次与领域的描述,可借用高级语言的精巧结构简化电路的描述[3]。

VHDL 语言能够得到硬件设计者的不断重视,还具备以下优点:(1)VHDL 行为描述能力明显强于其他HDL语言,使设计人员不必考虑具体的器件工艺结构,便于设计电路系统;(2)能在设计的各个阶段对电路系统进行仿真模拟,使设计者在设计早期就能检查系统的功能,减少可能发生的错误,降低开发成本;(3)VHDL 语言能将复杂的系统分解成若干部分,实现多人多任务的并行工作方式,提高工作效率;(4)EDA 平台和VHDL 综合工具性能日益完善。

4 程序设计

本文将使用MAX+PLUS II 开发平台,利用VHDL语言,设计一个“01111010”序列发生器,结合波形仿真功能,可直观、便捷地验证设计的正确性。MAX+PLUS II 是目前使用极为广泛的EDA 开发工具之一,使用MAX+PLUS II,设计者无需精通器件内部的复杂结构,而只需要用自己熟悉的设计输入工具(如原理图或高级行为语言)建立设计,MAX+PLUS II 会自动把这些设计转换成最终结构所需的格式,如图1 所示。由于有关结构的详细知识已经装入开发工具,设计者不需手工优化自己的设计,因此,设计速度非常快。

图1 MAX+PLUS II 启动界面Fig.1 MAX+PLUS II startup interface

MAX+PLUS II 具有以下特点:(1)开放的界面,支持多家公司提供的工具接口;(2)与结构无关,MAX+PLUS II 的编译器,提供强有力的逻辑综合与最小化功能,使用户比较容易将其设计集成到器件中;(3)多平台,它的设计输入、处理与校验功能一起提供了全集成化的一套可编程开发工具,加快调试进程,缩短开发周期;(4)全集成化;(5)模块组合式工具软件;(6)支持硬件描述语言VHDL[4]。

在序列发生器的设计中,选用计数器作为状态切换的控制电路。计数器可以完成对脉冲的个数进行计数,以实现数字测量、状态控制和数据运算等,它是数字系统最常用的基本部件,是典型的时序电路。序列发生器的设计原理是,结合VHDL 语言的判断和赋值功能,按照“0-1-0-1-1-1-1-0”自左向右的顺序,实现串行输出。计数器的输出,可以作为CASE 语句的判断信号,从而产生对应的输出,实现状态的有序切换,得到特定的序列。序列发生器的程序如下:

在本次设计中,定义了名为“BEHA”的实体,整个电路共有2 个输入端“CLR”和“CLK”。其中,“CLR”为电路的异步复位端,它的优先级最高,当复位信号有效时,电路输出信号“0”;“CLK”是时钟信号的输入端,它是计数器工作的核心控制信号,当时钟信号的上升沿出现时,计数器正常计数。

在电路功能描述部分,定义了名为“XLFS”的结构体,声明了名为“Q_TEMP”的信号,用于电信号传输,内设了2 个进程,使有关语句有序执行。

程序运行时,一个进程先确定电路的复位信号是否有效,然后,对计数的结果进行判断,若计数结果为“111”,则执行下一周期的计数,否则,程序在上升沿到来时刻,正常计数。另一个进程,根据计数器输出的结果,选择输出对应的值。如此循环往复,可得到序列“01111010”。由于电路采用串行输出,所以,电路输出的值相对序列本身是自右向左的。

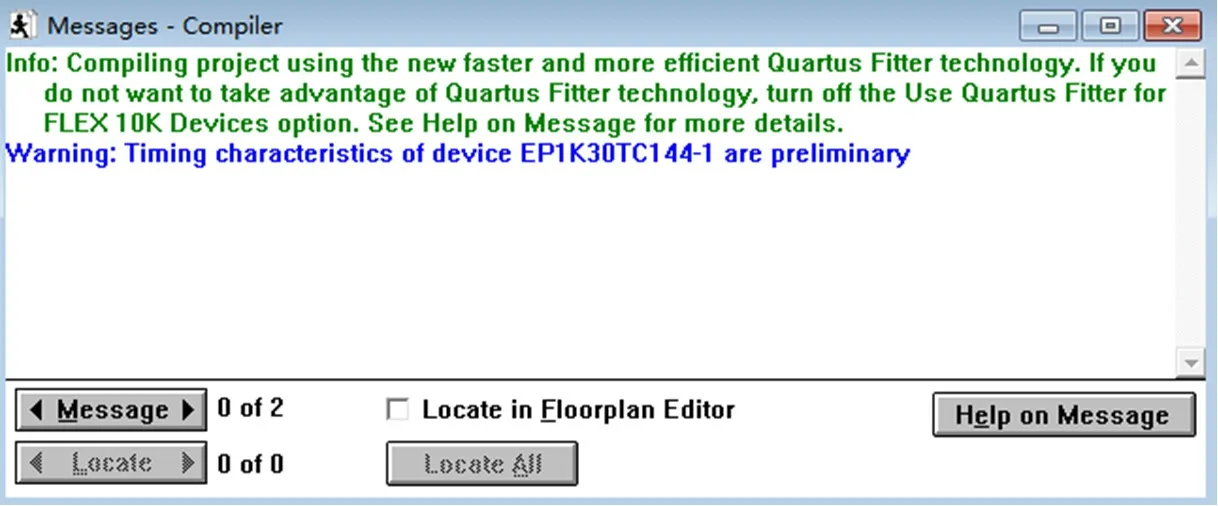

程序的编译结果如图2 所示。

图2 程序编译结果Fig.2 Program compilation results

目前,仿真技术已广泛运用于不同学科的研究工作中,它具有十分重要的作用。当所研究的对象实验成本高、实验周期长或需要花费很长时间才能得出系统的影响因素时,它能够帮助研究人员快速得出相关结论。在航空航天领域,仿真已是飞行器和卫星运载工具研制必不可少的手段,可以取得很高的经济效益。在研制、鉴定和定型全过程都必须全面地应用先进的仿真技术[5]。在集成电路生产中,它可以有效得到不同工艺对良品率的影响;在电路设计领域,结合波形仿真图,可直观地看出输出端的具体状态,确定电路功能设计是否正确,如图3 所示。

图3 添加电路端口信号Fig.3 Adding circuit port signal

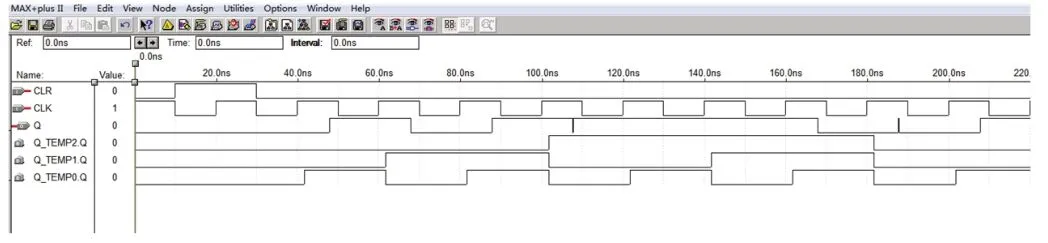

本次设计中,序列发生器的波形如图4 所示,在10ns-30ns 期间,电路的复位信号有效,即使时钟信号的上升沿已经出现,电路也不能正常计数;当电路的复位信号无效时,计数器正常工作,序列发生器有序输出“01111010”。从图中还可以看出,电路存在延时现象,这是不可避免的。

图4 电路仿真波形Fig.4 Circuit simulation waveform

5 结语

本文在深入理解序列发生器工作原理的基础上,在MAX+PLUS II 设计平台中利用VHDL 语言,完成序列发生器的设计,针对编译提示的问题,对程序进行修改,完成波形仿真,实现预定的电路功能。

引用

[1] 程秀英,侯卫周.基于NI Multisim 10.1数字逻辑选择器的虚拟仿真[J].实验科学与技术,2015(3):56-58.

[2] 魏欣,顾斌,姜志鹏.数字电路EDA设计(第三版)[M].西安:西安电子科技大学出版社,2016.

[3] 顾斌,赵明忠,姜志鹏,等.数字电路EDA设计[M].西安:西安电子科技大学出版社,2010.

[4] 胡赟鹏.一种可编程ASIC的开发软件[J].现代电子技术,2001 (8):52-54.

[5] 李华.开放式仿真系统的设计与关键技术[J].电子对抗技术,2002(1):35-38.