基于FPGA 的多通道ARINC429 总线测试系统

2023-02-14秦旭军

孙 骜,秦旭军

(中国电子科技集团公司第四十七研究所,辽宁 沈阳 110000)

0 引言

目前,有大量的机载设备在使用ARINC429 总线进行数据交互,为提高具有ARINC429 接口设备的测试效率,降低开发成本,本文基于FPGA 强大的并行处理能力、丰富的I/O 接口资源以及半定制化的设计理念,利用NIOS II 软核处理器,结合FPGA 的可编程逻辑端,设计了一款多通道ARINC429 总线测试系统。系统通过PCI接口与计算机通信,完成被测设备与计算机的数据交互,实现ARINC429 总线接口的自动化测试。

由于PCI 总线以及ARINC429 总线协议相对复杂,本设计采用了成熟的总线接口芯片[1−2],降低了系统的开发难度,其中PCI 接口选用了PCI9054 芯片,ARINC429 接口选用了HI-3584、HI-3182 芯片。即使PCI 总线的设计采用了接口芯片,但PCI9054 芯片的功能还是非常繁多,对此本文介绍了设计中PCI9054 芯片选用的模式、数据位宽等基本参数信息,此外重点对EEPROM 的使用方法、读/写操作的时序分析以及调试过程中的注意事项进行了详细阐述,希望能够达到抽丝剥茧的目的。

1 硬件架构设计

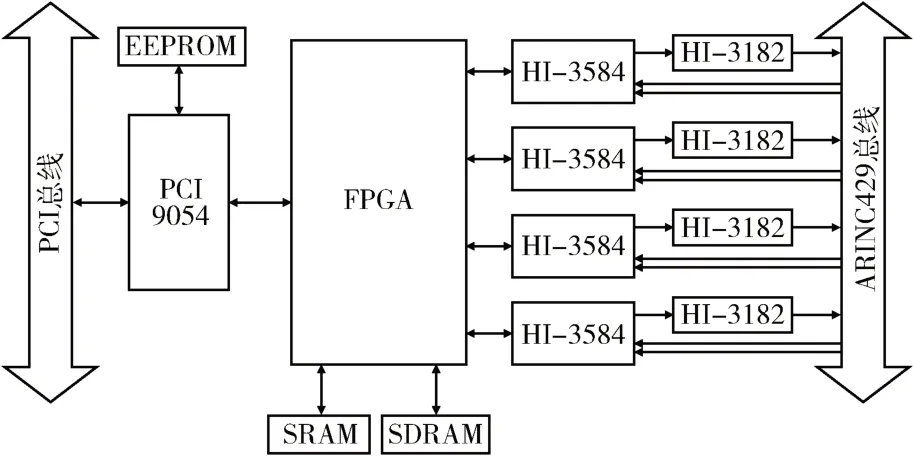

本设计中系统有4 路ARINC429 发送通道以及8 路接收通道,计算机可对板卡的各个数据通道进行参数配置、状态读取、使能收/发数据等操作。采用可编程逻辑端(以下简称逻辑端)与NIOS Ⅱ处理器相结合的开发方式[3],逻辑端主要负责PCI、ARINC429 等外设芯片的驱动层逻辑,NIOS Ⅱ软核处理器主要负责完成系统业务层功能,硬件功能框图如图1 所示。

图1 硬件功能框图

上位机收发ARINC429 数据时,SRAM 作为上位机和板卡之间的数据缓冲区,通过PCI 总线实现上、下位机的数据交换[4],FPGA 将数据存储在SDRAM 中,FPGA中的软核处理器按照上位机的指令完成ARINC429 数据收发、状态维护、参数配置等功能[5]。

板卡硬件资源主要由FPGA、PCI 接口芯片、电源、SRAM、SDRAM、ARINC429 控制器及其驱动器组成[6−7]。为适应不同的应用场景,本设计采用SDRAM 作为板卡的ARINC429 数据存储区并分成12 块,分别对应4 路发送及8 路接收通道。

2 FPGA 设计

由于系统功能复杂并且互连所需的I/O 数量多,因此选用的FPGA 型号是Altera 公司的EP4CE30F23C7N,其内部有28 848 个逻辑单元,可用的GPIO 最多可达328个,满足设计要求。

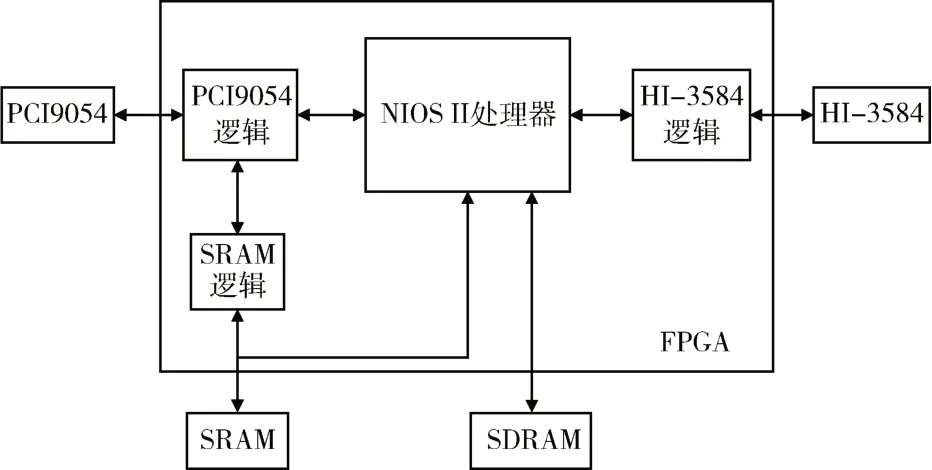

设计时在Quartus Ⅱ软件中创建工程,并用硬件描述语言实现外设芯片的逻辑功能,使其满足芯片的时序要求。然后使用集成工具Qsys 搭建基于NIOS Ⅱ处理器以及相关功能IP 核的SOPC 系统,本设计所用的IP 核有PIO、中断、定时器、SRAM 及SDRAM 控制器等。在Quar‐tus Ⅱ软件中创建顶层文件,将逻辑端的模块与NIOS Ⅱ处理器的端口在顶层文件进行例化实现互连[8]。FPGA 内部逻辑主要由PCI9054 逻辑块、SRAM 逻辑块、HI-3584 逻辑块以及NIOS Ⅱ处理器组成,框图如图2 所示。

图2 FPGA 逻辑框图

PCI 接口的传输速度较快,并且本设计采用32 位数据位宽,而板卡上的SDRAM 读写速度较慢,数据位宽是16 位,两者传输速度相差很大,系统无法实时地将PCI总线上的数据写入SDRAM 中,因此选用一片SRAM 解决读写速度相差过大的问题[9]。SRAM 读写速度快,当上位机向板卡写入数据时,FPGA 先将PCI 总线上的数据暂存在SRAM 中,在上位机发送数据完成后,FPGA 再将数据存入SDRAM,读取数据反之亦然。

考虑到上位机收发数据与ARINC429 收发数据都需要使用SDRAM,涉及的仲裁、决策、状态判断比较复杂,用硬件描述语言来实现相对困难,因此设计中使用NIOS Ⅱ处理器来完成SDRAM 相关业务。此外,考虑到PCI 总线读写速度较快,设计中采用逻辑端控制PCI接口芯片与SRAM 的数据交互。NIOS Ⅱ处理器与ARINC429 的各个收发通道之间用逻辑端分别设计了FIFO,它将自动控制接口芯片收/发数据。对NIOS Ⅱ处理器而言收/发ARINC429 数据只需要访问相应FIFO 即可,减小了处理器的使用率。

3 PCI 接口设计

PCI 接口开发常见的有两种:一种是采用CPLD 或FPGA 来实现,采用这种方法时需要购买相应的IP 核,用户可采用比较简单的逻辑实现PCI 总线的通信,但成本较高。另一种是采用PCI 接口芯片,例如PLX 公司的PCI9054、PCI9052[10],这种方法可大幅度降低设计难度,开发者无需投入大量时间研究总线协议的详细内容,接口芯片在系统中充当“桥”芯片的作用,可缩短系统的开发周期,同时成本相对也低很多。

本设计采用了第二种方法,采用了PLX 公司的PCI9054 作为PCI 接口芯片[11],该芯片具有成熟度高、成本低的特点。PCI9054 芯片按功能可分为3 类接口:PCI总线接口、本地总线接口以及EEPROM 接口。PCI 总线接口用于完成PCI 协议相关的功能,与计算机的PCI 总线互连,当PCI9054 配置好后PCI 总线上的操作由该芯片来完成。本地总线接口负责PCI9054 与FPGA 之间的数据交互。EEPROM 接口负责读取外部EEPROM 的配置信息,这些配置信息是PCI9054 的寄存器参数,系统上电后PCI9054 通过EEPROM 进行参数配置,设计中选用的型号是93LC56B。

当EEPROM 为空时需要特别注意,否则可能会出现操作系统无法启动或者启动后无法找到板卡的问题。EEPROM 的烧录有多种方式,本设计使用PLX 公司提供PLXMon 软件进行烧录。首次烧写时,需要将93LC56B的DI、DO 引脚下拉,同时PCI9054 的TEST 引脚也下拉,这样操作系统上电后会按照PCI9054 内部的默认参数进行配置。操作系统正常启动后DI、DO 引脚上拉,然后通过PLXMon 软件进行烧录即可。EEPROM 正确烧录后,DI、DO 引脚保持上拉即可。

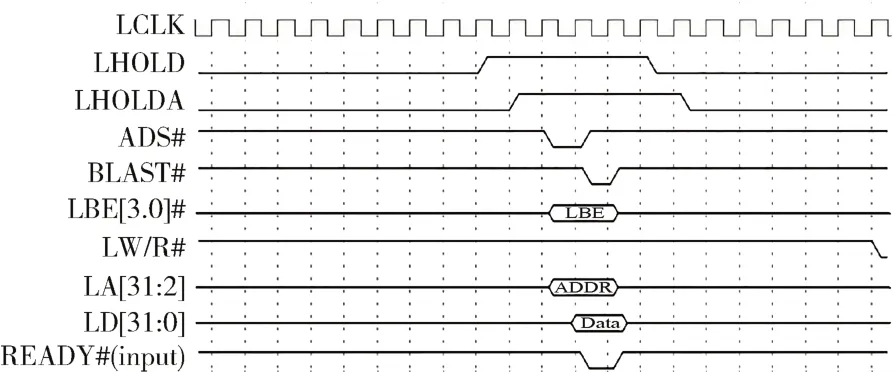

本设计中PCI9054 采用C 模式,本地总线采用32 位数据总线,单次读/写、DMA 或突发传输模式。在PCI 总线侧,PCI9054 会根据寄存器的配置自动响应总线信号,而本地总线的控制需要在FPGA 上实现。本地总线主要涉及的信号有:LHOLD、LHOLDA、ADS#、BLAST#、LW/R#、LA[31:2]、LD[31:0]、READY#,其中对于FPGA 来说关键的输出信号是LHOLDA 以及READY#。

单次写操作时序图如图3 所示,首先由PCI9054 使能LHOLD 信号来申请使用本地总线,FPGA 拉高LHOLDA 信号来做应答。然后PCI9054 驱动LW/R#信号,指示本次操作是读还是写。在ADS#信号出现下降沿时,表示地址总线LA[31:2]已经有效可用。在ADS#信号出现上升沿时,由PCI9054 驱动的数据总线LD[31:0]上出现有效数据,此时READY#需要开始输出低电平脉冲作为响应信号。在数据总线输出最后一个数据时,PCI9054 驱动BLAST#输出低电平脉冲。FPGA 检测到BLAST#有上升沿时,驱动READY#由低电平变成高电平,以此表示本次的写操作完成。

图3 单次写操作时序图

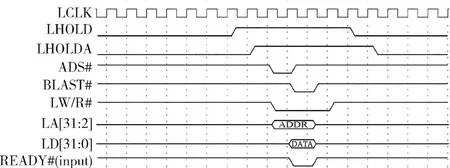

单次读操作时序图如图4 所示,与写操作类似,但需要注意的是LW/R#信号是低电平,并且数据总线需要由FPGA 来驱动。

图4 单次读操作时序图

不论写操作还是读操作,地址总线都是由PCI9054驱动,这是因为本设计中PCI 总线通信的发起者是计算机,在读、写数据时计算机作为主机给出地址。

此外,突发模式以及DMA 模式的时序与此类似,重点是LHOLDA、READY#信号以及对数据总线的控制。经过多次调试发现如果LHOLDA、READY#信号响应不及时会导致计算机死机。

4 ARINC429 接口设计

ARINC429 总线协议是由美国航空电子工程委员会制定的一种机载总线规范,该总线具有性能稳定、架构简单以及可靠性高等优点,已广泛应用于民用、军用飞机的航电系统中。

本设计中ARINC429 接口的控制器采用HOLT 公司的HI-3584 芯片,驱动器采用HI-3182 芯片。HI-3584 具有两路接收和一路发送通道,发送端需要驱动器才能连接在ARINC429 总线上,每个通道各自有独立的FIFO。FPGA 与HI-3584 的数据总线是16 位的,通过2 次数据交互将16 位 数据变为32 位ARINC429 数据[12]。在FPGA 侧来看,收/发ARINC429 数据相当于操作常规FIFO,使用起来非常方便。

HI-3182 芯片的供电需要+5 V、±15 V,它将HI-3584发送端的逻辑电平转换为ARINC 429 电平。在使用时注意它的调速电容,总线工作在100 KB/s 时,推荐选用75 pF;工作在12.5~14 KB/s 时,推荐选用500 pF。

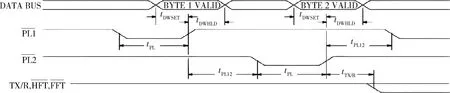

发送数据时,FPGA 驱动PL1n 输出低电平脉冲,HI-3584 接收第一个16 位数据,再驱动PL2n 输出低电平脉冲,HI-3584 接收到第二个16 位数据后TX/R 会变为低电平,表示FIFO 已经不为空。FPGA 检测到TX/R 为低电平后拉高ENTX,HI-3584 会将FIFO 中的数据逐个发出。FPGA 拉低ENTX 后发送数据结束,写入FIFO 以及发送数据的时序图分别如图5 及图6 所示。

图5 写入FIFO 时序图

图6 发送数据时序图

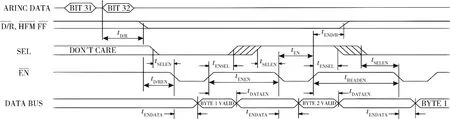

接收数据时,FPGA 检测到D/Rn 为低电平,先拉低SEL 驱动ENn 输出低电平脉冲,接收第一个16 位数据。然后拉高SEL 再次驱动ENn 输出低电平脉冲,接收第二个16 位数据,时序图如图7 所示。

图7 接收数据时序图

5 验证与测试

5.1 时序验证

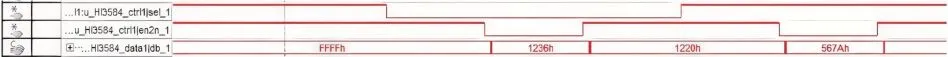

在SignalTapⅡ逻辑分析仪下观测到的PCI9054 以及HI-3584 的时序分别如图8~图11 所示,可见设计的时序与芯片手册相符。

图8 PCI9054 写操作实测时序图

图9 PCI9054 读操作实测时序图

图10 HI-3584 写入FIFO 实测时序图

图11 HI-3584 接收数据实测时序图

5.2 ARINC429 总线波形测试

ARINC429 总线在12.5 KB/s、100 KB/s 下的实测波形如图12、图13 所示。由图中可见信号的上升沿、下降沿具备单调性,无明显过冲、振铃等严重失真现象,信号的保持时间较长,满足信号完整性方面的要求。

图12 12.5 KB/s 下的实测波形图

图13 100 KB/s 下的实测波形图

5.3 系统整体测试

为验证系统的功能及实用性,本设计对系统进行了整体测试,上位机界面如图14 所示。测试前需要在界面中加载配置文件以及数据文件。配置文件包括系统的主要参数配置,包括中断方式、缓冲区大小、发送/接收时间间隔、总线速率等。数据文件包含了ARINC429总线的测试数据。

测试时,板卡的ARINC429 总线接口与被测设备的发送、接收接口互联。上位机通过PCI 总线将测试数据传送给板卡,板卡再将数据传送给被测设备。被测设备接收数据后,将数据通过板卡传回上位机,以此实现回环测试。上位机将发送数据与接收数据进行对比,全部相同则判定相应的通道为合格。

本设计对ARINC429 总线的4 路发送、8 路接收通道分别在12.5 KB/s、100 KB/s 下做了1 000 次的通信测试,均合格。

6 结论

本设计研究了PCI 总线以及ARINC429 总线的软硬件设计,通过FPGA 作为主控芯片,PCI9054、HI-3584 作为接口芯片,从工程应用角度出发,实现了计算机和ARINC429 总线设备的高效、多通道通信,并可配置成多种模式,适用于大多数ARINC429 接口设备的测试。本设计对PCI 总线及ARINC429 总线的互联、测试具有指导性意义,提高了ARINC429 接口设备的测试效率,降低了系统开发难度。

经验证测试,系统在不同的ARINC429 总线速率下都可以稳定、可靠工作,并具有成本低、高可靠性、开发周期短等特点,具备实际应用意义。