2.5D/3D硅基光电子集成技术及应用

2023-02-10欧祥鹏杨在利李志华王文武

欧祥鹏,杨在利,唐 波,李志华,罗 军,王文武,杨 妍

(中国科学院微电子研究所 集成电路先导工艺研发中心,北京 100029)

0 引 言

从2017到2022年,全球互联网流量以31%的年复合增长率增长了4倍[1]。随着流量的激增,数据中心的规模不断扩大,相应的能源消耗不断增加。到2030年,全球数据中心的用电量预计将达到3 PWh,最高甚至可能达到8 PWh[2],相当于80个三峡水电站1年的发电量总和。急剧增长的数据传输流量和能源消耗对传输系统的带宽和功耗提出了严峻的挑战。传统的电子交换技术是基于电子在铜介质中传导实现的,通常可通过增加输入/输出(Input/Output,I/O)接口的数量和提高数据传输频率来提高整体的带宽密度[3]。但是由于阻容时间常数(Resistive Capacitive(RC)Time Constant)和电学损耗的存在,信道内的衰减和串扰随着频率的提高而越发明显,导致传输效率下降,基于电子的数据传输系统已无法满足日益增长的带宽以及节约能源消耗的需求[4]。

以光子作为信息的载体,实现集成光电子芯片(Electronic-Photonic Integrated Circuit, EPIC)是突破目前电子数据交换系统瓶颈的最有潜力的方案。硅基光电子芯片具有带宽宽、体积小和功耗低等优点,并且可以利用现有成熟的互补金属氧化物半导体(Complementary Metal-oxide-semiconductor, CMOS)工艺平台进行大规模、低成本生产[5-8]。除此之外,硅基平台还可以与其他多种材料异质集成,例如氮化硅(Si3N4)、锗(Ge)和磷化铟(InP)[9-12]。经过数十年的发展,硅基光电子器件已经取得了许多突破性的进展,矩形硅波导损耗低于1 dB/cm[13],氮化硅波导低于0.1 dB/m[14-15],硅基电光调制器的带宽超过了110 GHz[16],锗硅(GeSi)光电探测器的带宽达到了265 GHz[17]。2006年,美国Intel和UCSB的John Bowers课题组联合研发了硅基异质集成的激光器,三五族材料通过直接键合方式集成在硅衬底上,再对其进行工艺加工,实现硅基片上激光器,解决了硅基光电子集成芯片(简称硅光芯片,SiPho chip)上的光源难题[18];基于这一重大突破,Intel 在2016年推出了首个基于硅基光电子技术(简称硅光技术)的100 Gbit/s光模块产品,现每年出货超过百万只[19]。美国Inphi公司于2017年推出了100 Gbit/s密集波分复用(Dense Wavelength Division Multiplexing, DWDM)数据中心光模块[20]。此外,Cisco、Broadcom和惠普等国际光通信巨头也通过收购、自主研发等手段对硅光投入重金进行研发。近年来,国内多家高校、科研院所和企业也纷纷对硅光技术加大研发力度。2021年,国内首款1.6 Tbit/s硅光互连芯片在国家信息光电子创新中心(National Optoelectronics Innovation Center,NOEIC)完成研制[21]。硅光模块成功应用于数据中心光互连架构中和巨头公司的不断涌入,充分证明了硅基光电子集成芯片在光通信市场中的应用价值[22-23]。同时,随着硅基光电子技术的不断成熟,其在激光雷达和光计算等领域的应用也越来越受到关注。

本文首先介绍了硅基光电子集成的发展现状,然后介绍了目前主流的光电集成技术方案,并且回顾了每种技术方案的代表性工作和最新进展,最后展望了2.5D/3D硅基光电集成芯片的潜在应用,包括数据通信、激光雷达、光计算以及生化传感等。

1 硅基光电子集成发展现状

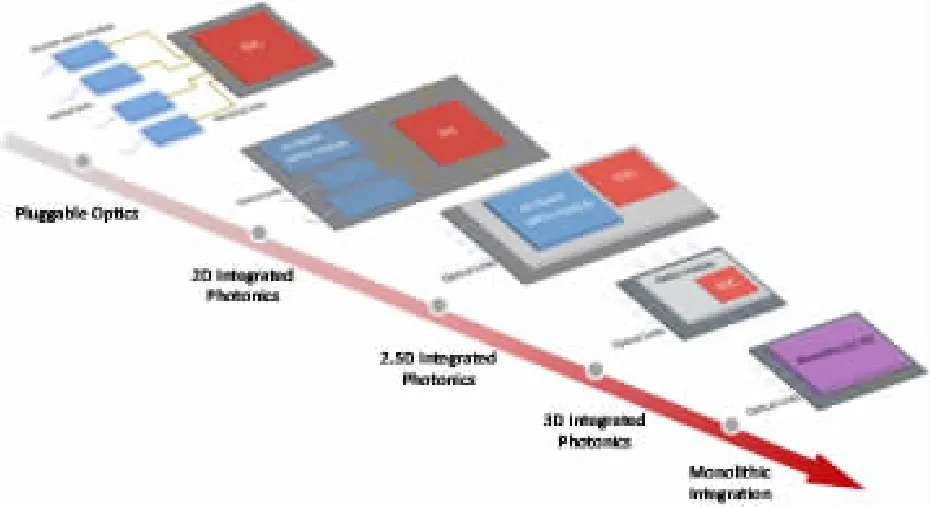

随着近年越来越多研发机构和行业巨头的加入,硅基光电子芯片以一种爆发式的速度向前发展:集成器件数目和集成速度不断提高,功耗不断降低,应用范围从光通信领域向激光雷达[24-25]、生化传感器[26]、高性能计算[27]和人工智能[28-29]等领域拓展[30-31],如图1所示。图2展示了包括磷化铟(InP)、硅(Si)、异质集成磷化铟/硅(InP/Si)或异质集成砷化镓/硅(GaAs/Si)3种平台上集成的光子器件数量的演变[32]。基于硅基平台设计和制备光子集成芯片(Photonic Integrated Circuits,PIC)起源于21世纪初,由于硅和二氧化硅的折射率差大,所以硅光器件尺寸非常紧凑。硅基光电子芯片可以利用先进的CMOS工艺进行加工,因此其集成度快速增长,目前硅基平台单个PIC上的光子器件的数目已经远远超过了从80年代就开始发展的InP平台。InP/Si(或GaAs/Si)异质集成平台因其可以在硅上集成片上激光器和光放大器在近些年备受关注,集成器件数量也在急剧增加[33]。随着集成光电子器件数量的不断增加,光电集成芯片性能在不断提高,新的挑战也随之而来[34-35]。传统的光电集成芯片的集成方式是PIC和集成电路芯片(Electronic Integrated Circuit, EIC)在同一个二维(2D)平面通过引线键合(Wire-bonding)的方式实现光信号和电信号的互连和控制[36]。但是Wire-bonding方式的引线较长,会占用比较大的面积,同时当信号频率越来越高时,寄生效应越来越明显,导致芯片的集成密度、带宽密度和能效明显下降。2.5D/3D集成(目前也被归为光电共封装(Co-packaged Optics, CPO)技术)是缩短互连长度、减小芯片尺寸从而减小寄生效应、提高集成密度和减小功耗的最具潜力的方案之一[37-39]。2.5D集成是将PIC和EIC都通过倒装键合(Flip-chip)的方式集成在转接板(Interposer)上,并通过Interposer上的金属布线实现PIC和EIC之间的电学互连,Interposer或硅通孔转接板(Through-Silicon-Via(TSV)Interposer, TSI)再与下方的封装基板或印刷电路板(Printed Circuit Board, PCB)相连。3D集成是将PIC直接作为Interposer或TSI,实现和EIC的垂直互连。2.5D/3D集成芯片的尺寸、重量和成本都将下降,功耗也随之降低[40-41]。图3展示了硅基光电子集成技术的发展趋势。

图1 硅基光电子的应用

图2 单片PIC在3种不同平台上集成的光子元件数量随时间变化的演变[22]

图3 硅基光电子集成技术的发展趋势

2 硅基光电子集成技术

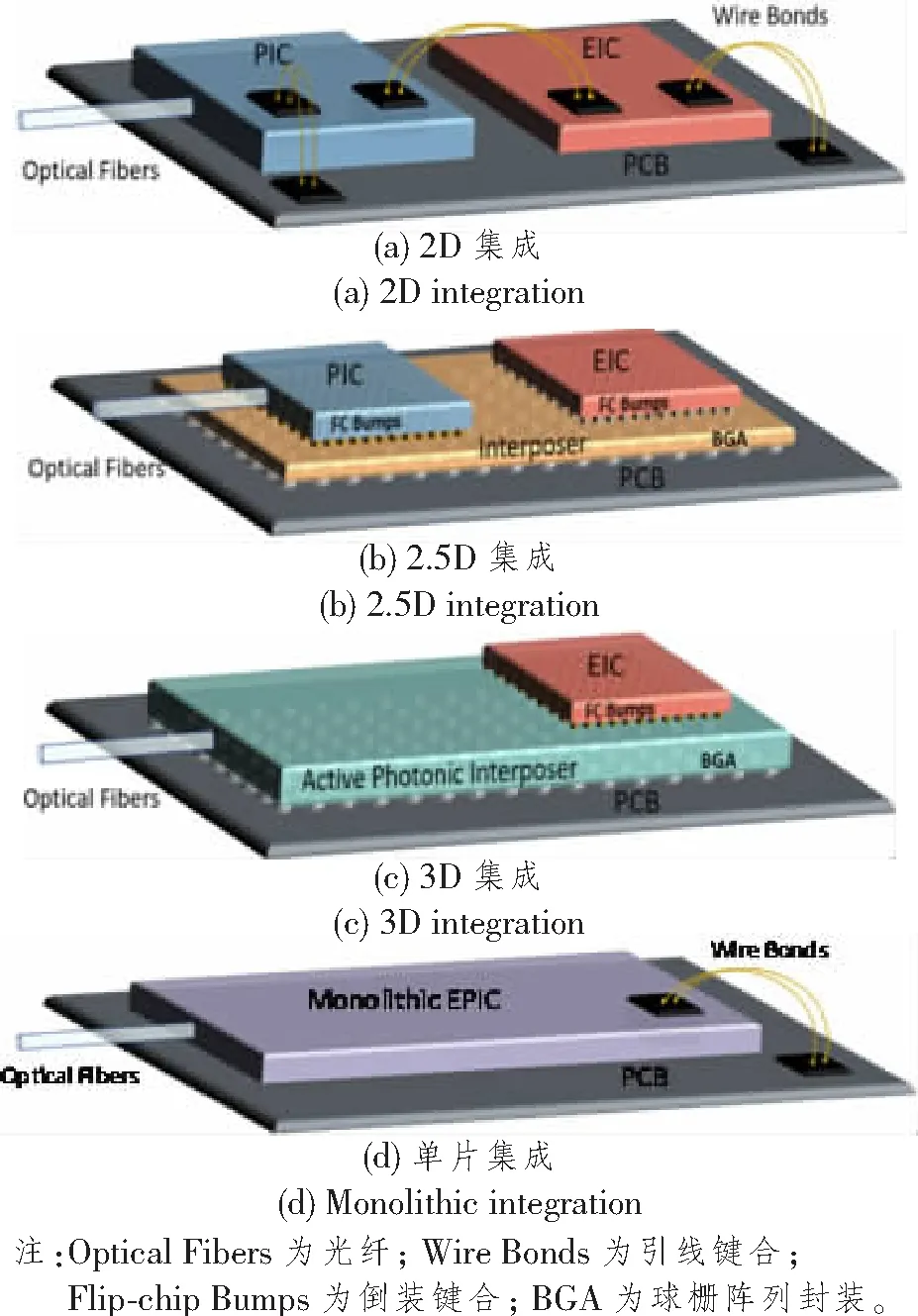

硅基光电子芯片的集成结构主要分为以下4种:2D平面光电集成、2.5D光电集成、3D光电集成和单片光电集成,如图4所示[42]。

图4 硅基光电集成结构

2.1 2D集成

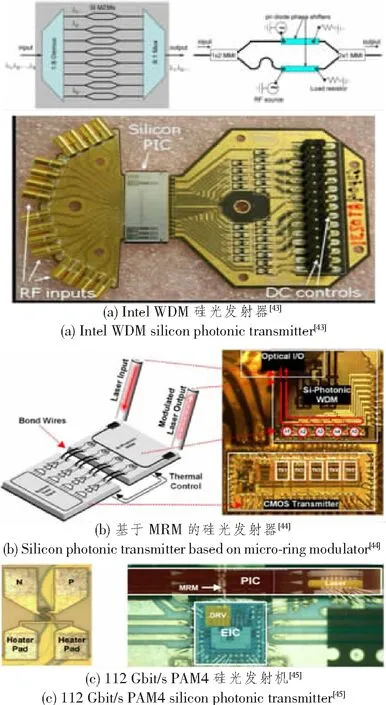

2D平面光电集成结构如图4(a)所示,EIC和PIC水平排列封装在PCB上,采用Wire-bonding的方式实现PIC和EIC的互连互通,最后通过板上芯片封装(Chips on Board, COB)技术实现 2D 集成。2D集成的优势在于可以单独设计制备EIC和PIC,具有很高的灵活性。同时,2D集成封装工艺比较简单,目前已得到广泛商用。但是,EIC和PIC之间的电学互连较长,当传输高频信号时,信号在传输过程中会发生明显的衰减,导致2D集成的光模块性能下降。此外,由于Wire-bonding所占的面积比较大,导致光模块整体尺寸和功耗较大。图5所示为2D集成的硅基光电子芯片。

2009年,Intel实现了具有波分复用(Wavelength division multiplexing,WDM)功能的2D集成硅光发射器(Transmitter)芯片,如图5(a)所示[43]。该芯片的结构由8个高速马赫曾德尔电光调制器(Mach-Zehnder Modulator,MZM)阵列、复用器(Mux)和解复用器(DeMux)组成,并且单片集成在同一绝缘体上硅(Silicon-on-Insulator, SOI)衬底上。其中,为了实现高速性能,每一个MZM的行波电极终端阻抗都经过了优化,以减少射频(Radio Frequency,RF)反射,从而最大程度地保持信号完整性。该发射器采用2D光电集成,光芯片位于整个模块的中间,两边分别是RF信号输入和热调控制模块。光芯片和电芯片通过Wire-bonding的方式实现电学互连,整个模块尺寸为~8 mm×20 mm。每个信道实现了25 Gbit/s的数据传输速率,整个光模块的数据传输能力超过200 Gbit/s,证明了硅光技术将来可以应用于Tbit/s速率级的数据传输系统。但是基于马赫曾德尔干涉仪(Mach-Zender Interferometer,MZI)的光传输模块的体积较大,功耗较高,包括射频和热调谐在内的总功率消耗约为2 W。如何减小尺寸,提高集成密度,降低功耗成为硅光芯片未来的重点研究方向。

基于微环谐振器(Microring Resonator, MRR)的调制器因其结构紧凑,驱动电压低,并且带宽和MZM相接近,成为了下一代更高带宽密度、更高集成密度和更低功耗的光互连系统最有前景的解决方案之一[46-49]。但由于微环受温度的干扰较大,基于微环调制器(Microring Modulatorm,MRM)受环境的影响很大。Li Hao等人利用MRM首次实现了在温度波动的环境下,传输速率能稳定在5×25 Gbit/s的硅光发射器[44],其结构如图5(b)所示。2019年,他们在原先的工作基础上进一步利用MRM实现了112 Gbit/s的四电平脉冲幅度调制(4 Pulse Amplitude Modulation,PAM4)硅光发射机,并且实现了调制器、片上激光器和CMOS 电芯片的共封装[45]。如图5(c)所示,光芯片和电芯片在同一个平面上以Wire-bonding实现电学互连,功耗仅为6 pJ/bit。相比基于MZM的硅光发射器功耗得到了明显的下降。

图5 2D集成的硅基光电子芯片

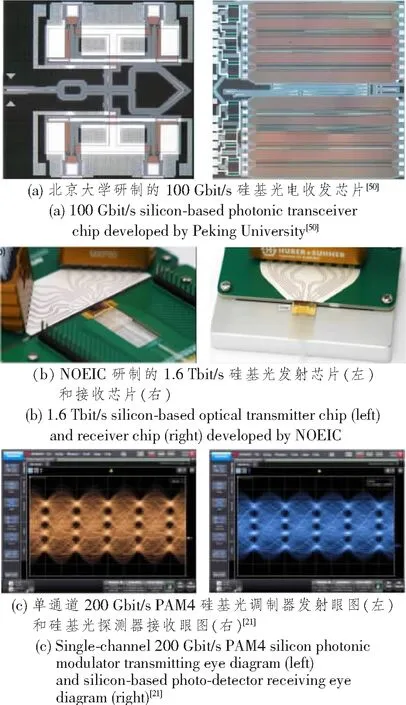

近年来,硅基光电子芯片也得到国内许多科研院所和企业的高度重视,图6所示为高速集成硅光收发芯片。2014年北京大学验证了100 Gbit/s硅基光收发芯片,集成了偏振分束器、光栅耦合器、光混频器、调制器和探测器等核心光电器件,如图6(a)所示[50]。2018年,NOEIC及合作单位联合研制的首款具有自主知识产权的100 Gbit/s硅基相干光收发芯片,并实现量产[51]。2021年,NOEIC团队研制出了我国首款1.6 Tbit/s硅基光收发芯片,实现了硅光芯片技术向Tbit/s级的跨越。如图6(b)所示,单颗硅基光发射芯片和硅基光接收芯片上分别集成了8通道电光调制器和光电探测器,实现了单通道200 Gbit/s PAM4信号传输[21]。

图6 高速集成硅光收发芯片

2.2 2.5D集成

2.5D集成是EIC和PIC都通过flip-chip的方式集成在Interposer上,并通过Interposer上的金属布线实现PIC和EIC之间的电学互连,Interposer再与下方的封装基板或PCB相连,其结构示意图如图4(b)所示。转接板可以通过两种方式与下方的封装基板或PCB相连,一种是利用Wire-bonding使转接板连接到下方的封装基板或PCB,另一种是在转接板中制备TSV,使其成为TSI,上方的PIC和EIC通过TSI垂直连接到封装基板或PCB。图7所示为2.5D集成的硅基光电子芯片。

图7 2.5D集成的硅基光电子芯片

基于Wire-bonding的2.5D集成技术工艺相对简单,并且近年来的研究成果展现出了良好的性能。2017年,新加坡微电子所(Institure of Micro Electronics,IME)实现了一个2.5D集成的多通道硅基集成光收发器[38]。电芯片和光芯片倒装在硅基转接板上,再通过Wire-bonding与底下的PCB实现互连,如图7(a)所示。该收发器实现了单通道超过50 Gbit/s的传输速率,通过多通道或者多芯片的共封装,实现了超过400 Gbit/s甚至更高的传输速率。2018年,Ari Novack实现了64 Gbaud传输速率的集成可调激光器的2.5D集成相干硅光收发模块[52]。光引擎、驱动电路和跨阻放大器(Trans-impedance Amplifier, TIA)等被封装到PCB上,该相干硅光收发器如图7(b)所示,其尺寸仅与1枚一元硬币相当。

基于TSI的互连使电芯片和光芯片与底下载板实现更短电学互连长度和更高的布线密度[54]。2013年,佐治亚理工大学在玻璃基板上实现了2.5D光电集成芯片[53]。该方案将PIC和EIC倒装在玻璃基板上,通过在玻璃转接板上做通孔引出电学信号,其结构示意图如图7(c)所示。2020年,Abrams 等人利用在硅转接板上集成多个PIC和EIC实现了以微盘调制器(Microdisk modulator, MDM)为基础器件的多通道、多芯片的光模块,其中每个传输信道传输速率达到10 Gbit/s,如图7(d)所示[42, 55]。MDM可以大幅度减小光引擎的尺寸和降低功耗,从而提高集成带宽密度和能效。

2.5D集成具有电学互连长度短、互连密度高和功耗低等优点,并且可以实现在同一个载板上放置多个PIC和EIC,具有很高的灵活性,可以将更多的功能集成到同一个模块里。但是2.5D的电学互连长度会比3D集成要长,相应的RC时间常数和电学损耗也会增加。2.5D集成结构被认为是当前技术水平下最合理的集成方案,工艺发展相对成熟,电学互连长度较短,带宽密度较高,很好地平衡了光模块的性能、工艺难度和成本。2021年,Broadcom 推出了一款用于数据中心的2.5D集成的光模块[56]。该模块采用了光/电共封装的方案,拥有128条信道,单通道传输速率达到200 Gbit/s,整体实现了25.6 Tbit/s的传输速率,将光模块的传输速率由百Gbit/s向百Tbit/s迈进。Broadcom公司称跟现在的光开关相比,采用2.5D/3D光电共封装的结构可以节约40%的功耗和40%的Cost/bit成本。

2.3 3D集成

3D 集成方案是将PIC直接作为Interposer,与EIC在垂直方向上实现堆叠,实现更短的互连长度、更高的集成密度以及更好的高频性能,如图4(c)所示[57]。一般来说,3D光电集成是通过EIC倒装在PIC的顶部,再从PIC的边缘引线到PCB上,实现光电集成芯片和封装基板或PCB的互连。另外,还可以在PIC上直接制备TSV,做成有源光子TSV转接板(Active Photonic TSI),将EIC倒装在PIC上,通过PIC上的TSV与下方封装基板或PCB实现垂直互连,从而进一步缩短电学互连长度。但是硅基光子器件对折射率变化敏感,在硅光芯片上实现TSV金属通孔会引入应力,从而改变材料的折射率,需要在设计制备时考虑TSV对光子器件性能的影响[58]。图8所示为3D集成的硅基光电子芯片。

图8 3D集成的硅基光电子芯片

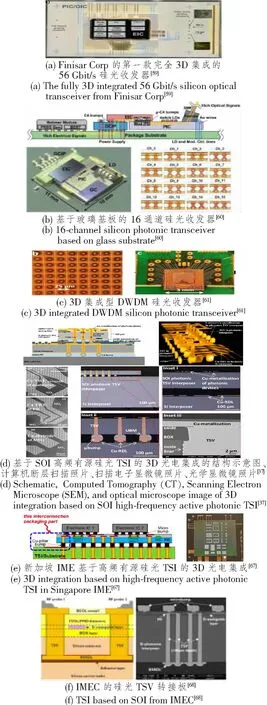

近年来,3D光电集成不断发展,基于第一种方案的3D光电集成芯片越来越成熟。2015年,Finisar Corp.的Gilles Denoyer等人研发出了传输速率为56 Gbit/s的一款不归零码(Non Return to Zero,NRZ)3D集成硅光收发器,如图8(a)所示[59]。EIC主要包括了两个MZM的驱动和两个发射机和接收机的TIA/限幅放大器(Limiting Amplifier,LA),通过microbump与下面的PIC相连,封装好的光模块总功耗为11.2 pJ/bit。2018年,日本富士通公司验证了具有3D集成的单通道传输速率超过25 Gbit/s的16通道硅光收发器,如图8(b)[60]所示。在该结构中,一个EIC芯片和一个PIC芯片通过微凸块(Microbump)/凸块下金属(Under Bump Metal,UBM))直接倒装键合,最大限度地减少了EIC和PIC之间的布线长度和寄生电容,并减轻TIA和光电探测器、驱动器和调制器之间电信号的衰减。并且该收发器还利用玻璃转接板支撑键合的EIC和PIC,利用solder bumps实现二者金属互连并利用Wire-bonding与PCB实现互连。与硅作为转接板相比,玻璃转接板的电学损耗更小,但是目前玻璃的加工工艺仍未成熟且玻璃的散热能力比较差。2021年,哥伦比亚大学的Stuart Daudlin等人利用DWDM实现了64通道的3D集成型的硅光收发器[61],EIC通过flip-chip键合在PIC上,PIC再通过Wire-bonding连接到PCB上,如图8(c)所示。该收发器利用频率梳光源实现DWDM和MRM高速调制,180 nm CMOS工艺实现驱动和放大电路,最后通过周期为25 μm的Cu pillar实现PIC和EIC的电学互连。最终利用光电共封装技术CPO实现光模块制备,实现面积为0.25 mm2的Tbit/s级数据传输速率及高达5 Tbit/s/mm2的集成带宽密度。利用频率梳光源实现DWDM和3D集成的方式可以极大地提高光模块的集成带宽密度和降低功耗[62-64]。

相比于第一种方案,基于有源硅光TSI的方案能实现更短的电学互连和更高的集成密度,但其实现的难度也更大。2016年,新加坡IME 的Yang Yan等人把TSV转接板的功能集成到PIC中并解决了TSV和硅光芯片光耦合之间的制备工艺兼容困难以及TSV对光器件性能的影响,如图8(d)所示[37, 65, 66]。该3D集成模块中,可调波导阵列光栅(Silicon Arrayed Waveguide Grating, AWG)的调节范围超过600 GHz,电光调制器带宽超过20 GHz,光电探测器的带宽为28 GHz,模块整体实现了30 Gbit/s的数据传输速率。2018年,新加坡IME的Kim等人在SOI硅光芯片中制备TSV,将EIC倒装键合在硅光芯片上,以与PCB进行电互连,该结构如图8(e)所示[67]。采用硅光TSI的3D集成方案具有紧凑封装、更小的外形尺寸和更低的RF损耗等优势,其单通道带宽能达到50 GHz。2021年,IMEC也报道了自己在硅光TSI方面的研究进展,实现了112 Gbit/s的NRZ传输速率,如图8(f)所示[68]。

2.4 单片集成

单片集成是指在同一个平台上(比如SOI衬底)同时制备光器件和电器件,两种器件之间的电学互连通过芯片内部的金属实现,如图4(d)所示。单片集成结构因为PIC和EIC在同一个管芯中,PIC和EIC之间的电学互连大大缩短,从而减小了RC时间常数以及电学损耗对信号传输的影响,功耗也得到了降低[69]。其次,单片集成结构可以最高效率地利用现有的CMOS工艺平台,实现低成本的大规模量产[70-71]。图9所示为单片集成的硅基光电子芯片。

图9 单片集成的硅基光电子芯片

2006年,Luxtera研发出了世界上第一款单片集成硅光收发器[72]。该收发器采用0.13 μm CMOS工艺,在片上集成了10 Gbit/s硅调制器、高性能的WDM、18 GHz锗探测器和RF电路和热调直流控制电路,实现了可用于高速光互连的硅光芯片。封装好的硅光收发模块如图9(a)所示。2015年,IBM利用美国Global Foundry 90 nm工艺技术在硅光平台上实现了单片集成结构的粗WDM收发器,其结构和测试眼图如图9(b)所示[71]。该收发器每个通道都能实现25 Gbit/s的传输速率,整体传输速率超过100 Gbit/s。同年,美国UC-Berkeley和MIT的研究组研发出了一款集成了7 000多万只晶体管和850个光子器件的光电子芯片,如图9(c)[73]所示。该芯片可用于逻辑运算、存储和通信。该成果证明了硅光芯片可以与现有的微电子芯片相融合,利用光子在信息传输方面的优越特性能够解决电芯片I/O接口所面临的瓶颈,将来可用于数据中心和超级计算机。2021年,瑞士苏黎世联邦理工大学开发了一款基于MRM的单片集成硅光收发器,如图9(d)[74],其利用45 nm “zero change” CMOS工艺在仅有0.015 mm2的尺寸上实现了满足10 Gbit/s所需的所有信号发射和接收器件,芯片带宽密度高达1.4 Tbit/s/mm2,其功耗仅为1.91 pJ/bit。

虽然单片集成结构的硅基光电集成芯片具有功耗低、尺寸小和封装简单等优点,但PIC和EIC的工艺存在一定的差异,想要完全兼容两种器件需要对电路进行协同设计,对工艺进行协同开发,而整个工艺开发的费用是极其昂贵的。并且由于光器件的工艺节点远远落后于电器件,为了单片集成二者,需要在两种器件性能上做一些妥协。单片集成可以最高程度实现光电融合,但若要高效地将光器件和电器件利用CMOS工艺单片集成于硅基平台上仍需要学术界和工业界共同努力。表1中列出了基于4种不同硅基光电子芯片集成技术的部分代表性工作。

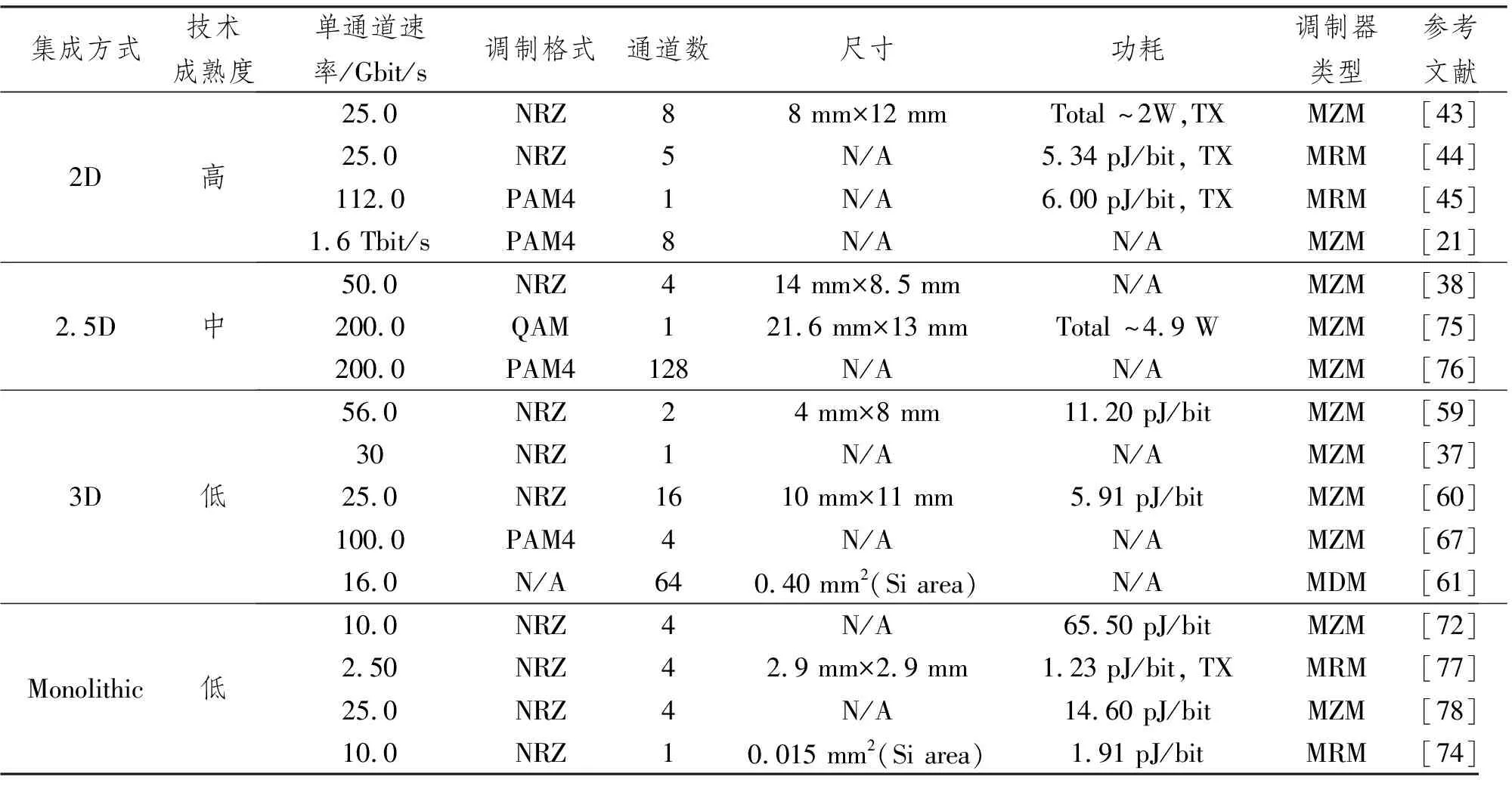

表1 基于4种不同集成技术的硅光通信芯片

3 2.5D/3D集成硅基光电子芯片的应用

随着硅光技术的不断成熟和集成工艺技术的不断进步,硅光芯片正在向大规模集成方向发展,单个光芯片集成的光子器件的数量增多和集成密度的提高,其功能也愈加多元化,其应用领域也开始从光通信向激光雷达、生化传感和光计算等领域拓展[79-80]。在硅光芯片中,许多光器件需要外部电路去调控或者驱动,例如调制器、探测器、移相器和光开关等,因此在大规模集成光器件的同时还需要考虑如何将控制电路与硅光芯片集成,最大程度地发挥硅基光电子芯片的集成优势[22, 81]。而传统Wire-bonding的光电集成方式已经开始限制硅基光电子大规模集成。

正如前文所述,硅基光电子芯片从传统的基于Wire-bonding的2D集成向基于Interposer或TSI的2.5D/3D集成发展,以实现更高的集成密度,更小的尺寸,更高的性能以及更低的功耗。在光通信和数据中心的应用中,2.5D/3D集成的硅基光电子芯片的传输速率已经从Gbit/s数量级提升到Tbit/s数量级。本节将介绍硅基光电子芯片在激光雷达、生化传感和光计算中的应用,并展望2.5D/3D集成技术对于这些应用的的潜在优势。

3.1 激光雷达

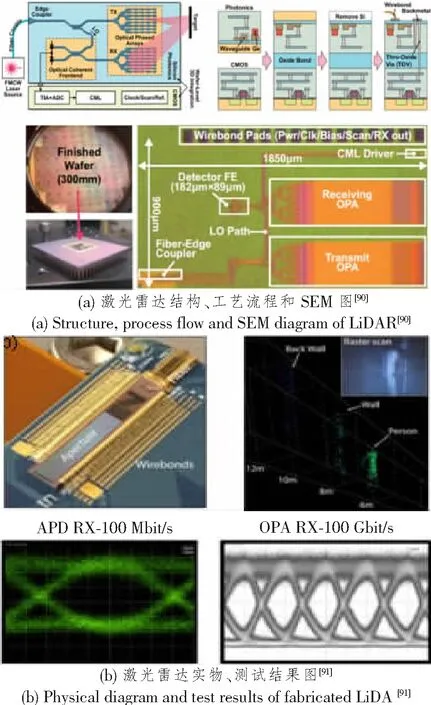

激光雷达是自动驾驶的核心器件之一,但是目前无论是机械式还是微机电系统(Micro-Electro-Mechanical System,MEMS)激光雷达的价格都过于昂贵,并且某些性能指标比如探测距离和速度、分辨率和器件尺寸等无法满足车载激光雷达的性能需求。基于光学相控阵(Optical Phased Arrays, OPA)和调频连续波(Frequency Modulated Continuous Wave, FMCW)的激光雷达,是目前业内认为未来最有前景的解决方案之一,可以将传统体积较大、价格昂贵的激光雷达在芯片上实现[82-84]。得益于硅基光电子技术在光通信和光互连方向多年的技术积累,硅基光电子集成平台是最有希望实现基于OPA的激光雷达的平台之一[85-87]。图10所示为基于硅基OPA的激光雷达。

图10 基于硅基OPA的激光雷达

2009年,根特大学首次在硅基平台上实现了一维OPA[88]。该OPA在1 550 nm的工作波长实现了2.3 °的横向扫描范围,并且通过改变入射波长的办法实现了14.1 °的纵向扫描范围。2013年,麻省理工学院的Sun等人实现了第1个二维OPA,其扫描角度为12 °×12 °[89]。随着学术界和工业界越来越多的研究和投入,基于硅基光电子平台的激光雷达得以快速发展。除了大规模集成OPA,还需要在芯片上集成驱动电路、控制电路和接收电路,以驱动激光器出射频率和波长、控制OPA的扫描范围和实现微弱回波信号检测。2019年,美国加州大学伯克利分校和麻省理工学院联合研发了第1款3D集成的FMCW相干激光雷达[90]。如图10(a)所示,该激光雷达将高灵敏度的相干探测器、OPA和CMOS电路集成在一个芯片里,并且利用300 mm的CMOS 工艺平台实现。在该工艺平台中,光子器件使用193 nm 浸没式光刻技术在300 mm SOI 晶圆上制造,使用65 nm光刻技术在体硅晶圆上制备CMOS电路,然后将PIC和EIC键合在一起。紧接着去除SOI 晶圆上的硅衬底,并用氧化通孔(Through-oxide Via, TOV)技术实现光子和 CMOS 器件之间的接触。该激光雷达最终实现了3.3 cm的扫描精度。此外,激光雷达的感知功能可以与无线空间通信功能集成到同一个芯片中,如图10(b)所示[91]。该3D集成的硅基激光雷达芯片可以实现约180 m的2D探测距离,约10 m的3D探测距离并且同时具备1 Gbit/s的无线通信能力。在2021年的国际消费电子展(Consumer Electronics Show,CES)上,Mobile Eye推出了基于硅光平台的集成式FMCW激光雷达,在一个微小的芯片上实现184线扫描[92]。这个模块集成了激光雷达所需的有源和无源元件及驱动电路,使基于硅光子学的激光雷达在商业化方面迈出了一大步。

对于集成大量需要调控的光器件的激光雷达芯片,2.5D/3D集成技术可以缩短电学互连长度,大大减小光电互连的面积,从而减小激光雷达模块的尺寸、重量和降低成本。因此,推动硅基2.5D/3D集成技术的发展可以促进更大规模的光电器件的集成,从而实现更高性能的硅基激光雷达芯片。

3.2 光计算

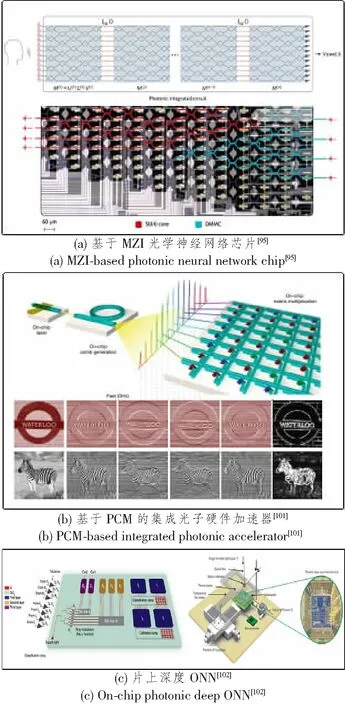

近年来,随着大数据、云计算、人工智能和图像识别等技术的发展,对海量的数据进行实时快速处理产生了急切的需求[31, 93]。但随着晶体管的特征尺寸已经接近摩尔定律的极限,基于传统微电子芯片的计算机算力已经接近瓶颈。而光子芯片由于光子本身具有传输速度高、低功耗和可并行等优点,因此光子计算芯片是实现高性能计算的一个非常有潜力的方案[94-96]。硅基光子计算芯片的主要光学结构包括MRR[97-98]和MZI[95,99]。同时,MRR或者MZI都需要一个匹配的控制电路去实现快速的矩阵操作,例如修改权重等[100]。图11所示为基于硅基光电子技术的光学神经网络芯片。2017年,MIT的Shen 等人在硅基平台上利用56个可编程的MZI实现了光学神经网络(Optical Neural Networks, ONN),如图11(a)所示[95]。研究人员为了验证其性能,将该芯片应用于元音识别实现了76.7%的准确率,证明了利用硅基光电子芯片实现ONN是可行的。2021年,Feldmann利用CMOS工艺,基于超低损耗的氮化硅波导,在片上集成了光频梳、16×16的相变材料(Phase-change-material, PCM)记忆矩阵,片上高速调制器和探测器,实现了集成光子硬件加速器,如图11(b)所示[101]。该加速器可以实现多路并行计算,计算能力高达每秒1012次成绩累加计算(Multiply Accumulate,MAC)运算,图中也展示了其对图像进行处理的结果。2022年,宾夕法尼亚大学Aflatouni等人在硅基平台上实现了深度ONN,其器件结构和封装成品如图11(c)所示[102]。该芯片直接对光信号进行读取和处理,避免了将光信号转换为电信号,并且消除了内存模块,从而大大加快了对信号处理的速度。该芯片可以在0.5 ns内实现对手写字母的分类,2类和4类准确率分别高达93.8%和89.8%。

图11 基于硅基光电子技术的光学神经网络芯片

但是上述光子计算芯片采用的是外置的电路驱动和激光器,如果能将激光器和驱动电路通过2.5D 或者3D集成的技术集成到计算芯片上,将会大大缩小光子计算芯片的尺寸和降低芯片整体的功耗,从而集成到现有的计算机上。此外,当矩阵越来越大时,所需要的光器件数量也随之增加,此时通过Wire-bonding等传统的方式去实现可编程控制电路是不理想的,其所需面积和功耗都会明显增加。而2.5D/3D集成技术可以在很小的尺寸内实现矩阵操作所需要的控制电路,进而获得高集成密度的低功耗硅基光子计算芯片。

光计算是目前研究的热点方向,它与人工智能、脑科学和大数据等行业相关联,又与传统的半导体技术、光电集成技术紧密相关,但是目前相关的研究仍处于初步探索阶段。推动光计算的发展需要半导体材料技术、微电子技术、光子技术、封装技术和算法等多学科共同努力,加速软件与硬件的融合,从而使光计算可以应用于实际,解决目前所面临的算力瓶颈。

3.3 生化传感

2019年新冠疫情席卷全球以来,具有生化、健康监测功能的传感设备出现了巨大的市场需求[103-104]。硅光传感技术因其具有灵敏度高、尺寸小和多功能集成等优点受到了很大的关注。基于硅光平台的传感器主要分为两种,分别是基于光谱和折射率变化。前者是观察吸收光谱和拉曼光谱的变化[105-106],而后者主要是基于MRR[107]、MZI[108]或者光子晶体[109]等结构,利用强度或谐振波长的变化将折射率改变提取出来。图12所示为基于硅基光电子平台的传感器。

图12 基于硅基光电子平台的传感器

基于折射率改变型的硅光传感器具有灵敏度高和分辨率高等优点,但是其自身无法识别特定的待检测物,需要进行表面功能化修饰。2015年,Genalyte在MRR表面形成生物功能修饰,实现了对多种蛋白质和脱氧核糖核酸(Deoxyribo Nucleic Acid,DNA)的同时检测,如图12(a)所示[110-111]。基于该技术,该公司成功实现了在30 min内实现对新冠病毒COVID-19的检测,并且产业化。但是该传感器仍依赖于外部的激光器和光谱仪,无法实现微型化和便携化。2020年,Ruiz-Vega等人提出了一种即时COVID-19 诊断和冠状病毒监测的纳米光子生物传感器,如图12(b)所示[104〗。该传感器基于双模波导(Bimodal Waveguide,BiMW),可在30 min内检测到 aM-fM级别微小浓度的核糖核酸(Ribonucleic Acid,RNA),其准确度可与基于标准聚合酶链式反应(Polymerase Chain Reaction,PCR)的分析仪器相媲美。

基于光谱变化型传感器具有可“识别”待测物的优点,可用于复杂环境的生化传感。2017年,IBM实现了首个集成硅光甲烷传感器,如图12(c)[26, 112]所示。由于甲烷在1 651 nm波长处有吸收峰,IBM利用先进的CMOS技术在SOI上制备了长达10 cm的波导结构,并且通过倒装键合的方式混合集成了出射波长为1 651 nm的片上激光器和其他光子,并且与外部驱动电路等实现封装。该硅光传感器实现了5 ppmv的高灵敏度、0.6 mW的低功耗以及只有0.25k美元的单个价格。在性能接近的前提下,实现了远远低于竞品的功耗和价格。2021年,Rockley Photonics公司报道了一款可用于血糖、酒精等生物特征进行监测的硅光传感芯片,如图12(d)所示[113]。该传感芯片采用频率梳光源和片上光谱仪实现对拉曼散射信号的分析,具有精度高、功耗低并且可以集成到可穿戴设备等优点[114-115]。

硅光传感器近些年取得了非常显著的进展,已经逐渐开始从实验室走向大众消费市场。采用2.5D/3D集成技术将控制电路和分析电路集成到同一个芯片上,可以进一步提高硅光传感器芯片的集成密度,缩小芯片尺寸和降低功耗。硅光传感器尺寸的减小和功耗的降低对于内部空间“寸土寸金”和续航能力有限的可穿戴设备具有重要的意义。若能实现2.5D/3D集成的硅光传感器,将能极大地推动其在可穿戴设备内的实际应用。

除了以上3种应用,硅基光电子芯片还可以用于光量子芯片和量子信息处理等领域,并且已经取得了许多突破性的进展[116-117],而这些应用需要庞大而复杂的控制电路,因此2.5D/3D硅基光电子集成技术对这些应用的发展有着关键的作用。

4 结束语

本文针对2.5D/3D硅基光电集成技术面向数据交换中传输带宽高、传输速率快和功耗低等需求,对硅光集成方案进行了介绍和总结。2.5D/3D集成不仅可以缩短光芯片和电芯片之间的互连长度,从而减小寄生效应,提高芯片的集成密度和性能,还可以使芯片封装的尺寸、重量下降,整体的功耗也随之减小。此外,回顾了硅基光电子技术在通信、激光雷达、光计算和生化传感方面的最新进展及其巨大的商业价值。同时,展望了这些芯片的关键性能可以利用2.5D/3D硅基光电集成技术得到大幅提升。未来,随着2.5D/3D硅基光电集成技术的发展,必将推动这些应用向高密度集成、高性能、低功耗和低成本方向发展,从而促进信息社会的进步。