基于模拟开关的低成本正交鉴相器实现

2023-01-11王明全关贝贝

王明全,关贝贝

(东北大学计算机科学与工程学院,辽宁沈阳,110167)

0 引言

在传统的测距以及测量仪表中,往往都需要进行鉴相,而此类应用的测量信号频率都属于中低频,而其往往对运算速度、开发难度以及成本控制都有较高的要求,追求更高的性价比。故而传统的基于现场可编程门阵列(Field Programmable Gate Array,FPGA)的数字鉴相以及以硬件乘法器为核心的模拟鉴相器由于其价格昂贵以及开发难度大的问题,在一些追求低成本、中低频鉴相的设计中不便使用。

而基于模拟开关的低成本正交鉴相器具有响应速度快、成本适中以及设计难度低的特点。

1 硬件正交鉴相器方案设计

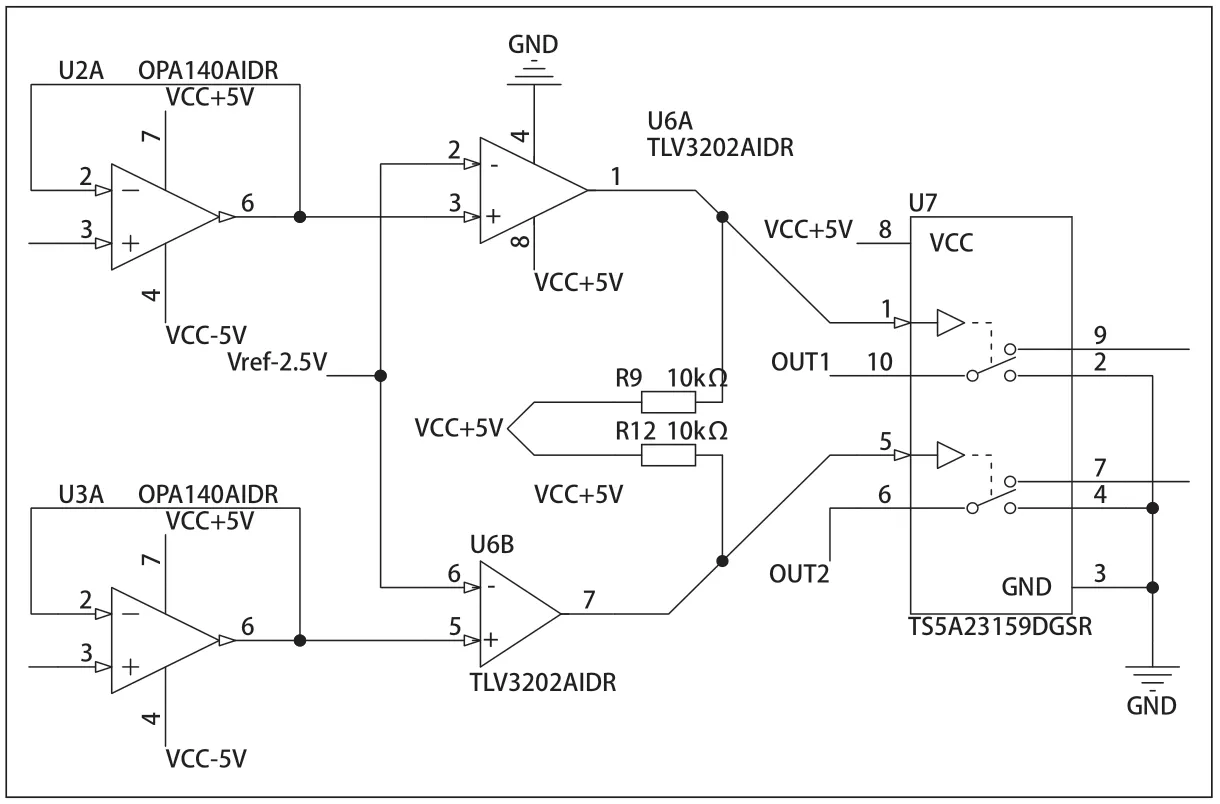

在市面常见的硬件鉴相器中,多使用的是价格昂贵的模拟乘法器或者混频器,而往往这些器件本身所带来的谐波失真与非线性也是相对难以处理的。因此在综合考虑了硬件成本、设计复杂度以及测量精度的情况下,提出了采用使用模拟开关进行调制,从而代替传统乘法器。整体方案如图1所示。

图1 硬件正交鉴相器设计框图

2 正交鉴相器设计

2.1 正交鉴相器整体硬件概述

正交鉴相器需要通入正弦信号以驱动模拟开关工作,因此此处使用了比较器TLV3202AIDR,用以将输入信号转化为方波。

而后将方波与需要检测的信号一并通入模拟开关TS5A 23159DGSR。在方波的驱动下模拟开关对输入的待测信号进行斩波与调制。

形成两路调制信号,通入后级的低通滤波器滤波,在经过后级滤波后,只剩余两路直流信号,而后通过这两路直流电压的大小即可计算出输入信号与驱动信号的相位差。

在系统设计中,由于电路带负载能力以及本身设计的需求,在多处使用了OPA140AIDR这款运算放大器,该款运放,本身具有11MHz增益带宽积与20V/us的压摆律,具有高精度、低噪声与轨到轨输出的特点,同时为保持该运放良好的性能,本系统采用+5V与-5V双电源供电。

2.2 参考电压产生电路

由于使用了比较器用以处理正交正弦信号,要使其变为正交方波信号。因此需要产生基准电压Vref,用以将正弦波转变为方波,且电压值为2.5V。本系统所采用的基准电压生成电路如图2所示。

图2 基准电压生成电路

在综合考虑了性价比与可操作性之后,这里选择采用了两个分别为50kΩ的电阻进行分压,以产生2.5V电压。其上并接的2.2μF电容C1用于削减电阻所带来的热噪声与FR噪声,以确保Vref的稳定与精准。

而后为避免负载效应以及不可预测的情况,使用OPA140接为跟随器模式,以提高输出能力,进一步保证基准电压Vref的稳定。

2.3 正交调制电路设计

正交正弦信号在经过OPA140构成的跟随器,使前后级隔离,而后通过TLV3202。TLV3202将输入信号与基准源Vref进行比较,从而将正交正弦整形为正交方波。TS5A23159DGSR在两路正交方波的控制下对输入信号进行斩波,而后生成调制信号,而后送入后级低通滤波器进行滤波。如图3所示。

图3 正交调制电路

此处需要注意,由于驱动信号的特殊性,为保持严格正交,因此此处在PCB板级布线时需要按照差分对布线,由于方波包含有较多的频率分量,应尽量避免线路过孔,避免由于传输线路问题使得频率分量过度丢失进而导致方波无法以较好的边沿驱动模拟开关。以保证最终计算结果的精确性。

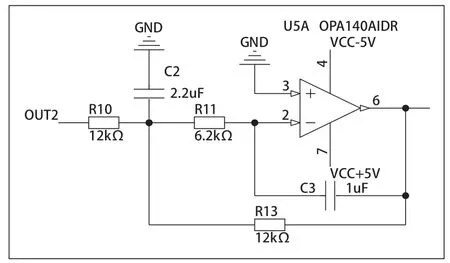

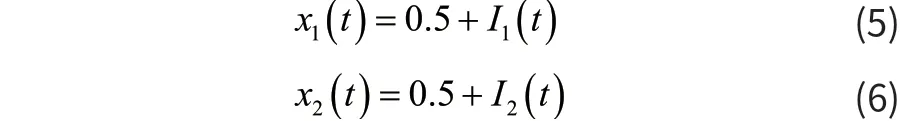

2.4 低通滤波器电路设计

输入的待测信号在经过模拟开关斩波与调制后,输出的信号包含着丰富的频率分量。因此为了更好地抑制非直流分量,设计采用了多重负反馈滤波器(MFB)在进行滤波。

有源滤波器的过渡带陡降与稳定性以及带负载能力都要远远优于无源滤波器,因此采用了多重负反馈滤波器。滤波器设计如图4所示。

图4 MFB低通滤波电路

此处通过计算可知其截止频率fc=100Hz。

2.5 正交鉴相原理推导

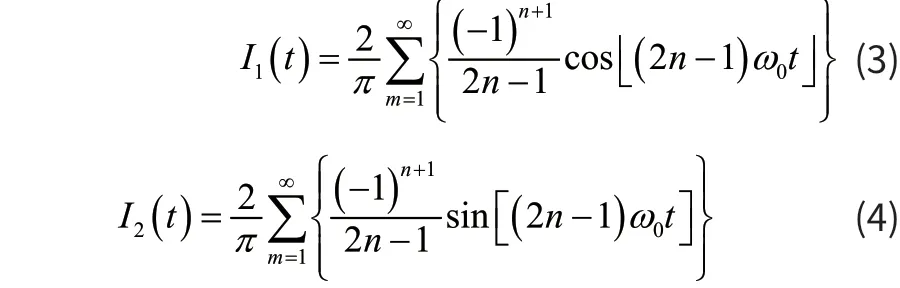

模拟开关TS5A23159DGSR的两路控制信号为正交方波,结合控制信号的特点可知,模拟开关等效于将两路正交的方波与输入信号进行混频,即将与控制信号等效的0-1-0-1序列与待测信号相乘,因此等效方波的直流电压为0.5V。

令两路正交方波为x1(t)、x2(t),经过傅里叶分解得:

令:

将(3)与(4)分别带入(1)与(2)得:

假设待处理的信号为:

模拟开关的调制可以等效为方波与待处理信号进行混频。

因此(1)与(2)分别与(3)相乘得:

这里令:

对于k1(t)由积化和差公式得:

其中在(12)公式中的差频项出现直流成分,即:

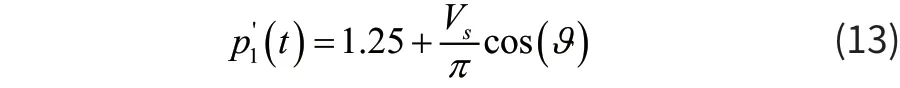

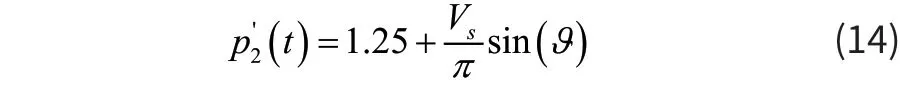

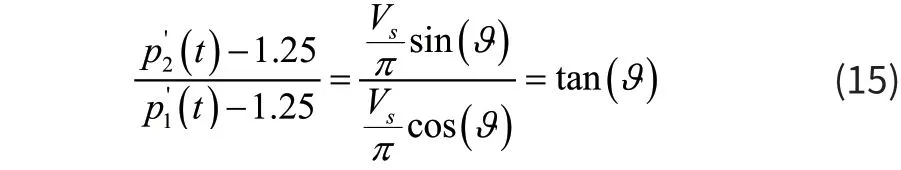

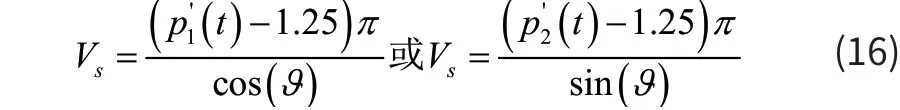

而调制后的信号p1(t)经过滤波器,去除非直流成分后为:

同理得:

而后经过数学公式变换可得:

同时:

至此便可以利用(15)与(16)这两个公式以及()′1p t与()′2p t所得到的直流电压数值计算出ϑ,同时也可以计算出Vs。

2.6 去耦设计

系统中存在比较器,模拟开关等器件,在正常工作时,由于其本身功能的特殊性,需要在短时间内完成电压的大幅度跳变或者开关状态的快速切换,因此会导致器件在工作时会出现周期性的推拉电流能力激增的情况。

因此十分有必要在以上器件靠近电源的部分添加去耦电容,以满足突发性的电流瞬变,同时抑制电源毛刺。使以上芯片保持良好的工作状态,以达到更好的鉴相性能。

3 测试结果与分析

测量时使用的标准值测量仪器为Tektronix公司的FCA3100,使用的信号源是RIGOL公司的DG4202,电压测量使用的是Tektronix公司的DMM4020-五位半台表。

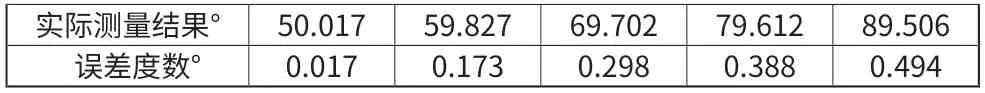

鉴相频率选择了1kHz与10kHz,测试结果如表1与表2所示。

表1 鉴相数据统计(1kHz)

注:实际测量结果保留小数点后3位,仪器测量误差为±0.005°,误差度数为两个结果的差值的绝对值,下同。

表2 鉴相数据统计(10kHz)

4 结论

(1)相较于传统使用单片机的数字鉴相来说,运算速度快、反应迅速、极大减轻了单片机内浮点运算的压力;相较于使用FPGA的数字鉴相,结构简单、反应迅速、价格便宜。

(2)使用以模拟开关为核心、以比较器与滤波器为辅的鉴相模块,代替了传统的模拟乘法器,有效解决了模拟乘法器所带来的谐波失真与直流漂移等问题。

(3)目前该硬件鉴相器在频率比较高时的鉴相精度还有待提高,在改进中可以尝试使用更好的模拟开关与比较器,同时优化板级布局,精度与可使用的范围将会有比较大的提升空间。