FPGA供电网络工作在亚稳态的解决方案研究

2023-01-10杨东亮田琳宇

杨东亮,田琳宇,姬 进,闫 稳

(航空工业西安航空计算技术研究所,陕西 西安710065)

0 引言

目前数字电路设计中使用的主流FPGA均为低电压、低功耗型器件。FPGA供电网络主要有两个特点:1) 需要使用多种电源轨道,如常见的3.3 V、1.5 V、1.0 V电源等,分别用于I/O BANK、内核、DDR存储器的供电;2) 电源电流不固定,在很大程度上取决于实际的逻辑电平及FPGA实现的功能[1]。因此,各电源轨道的稳定性(在不同使用工况下电源电压保持稳定的能力)直接决定了FPGA是否可以正常工作。

本文讨论的对象是一种在机载通用输入输出模块上使用的FPGA,它使用了两种电源轨,分别为3.3 V和1.5 V。在实际工程应用中,3.3 V供电网络的亚稳态引起了通用输入输出模块上电BIT报故,且在周期任务运行中工作异常。针对该问题,通过设计排查、仿真分析,给出3.3 V供电网络工作在亚稳态的解决方案,并对解决方案的有效性进行了实验验证。

1 FPGA供电网络设计方案

机载产品使用的电源为二次电源,从飞机28 V直流汇流条上取电,通过内部的DC/DC模块将其转换为各类型电路使用的±15 V、5 V电源。FPGA使用的3.3 V、1.5 V、1.0 V电源为三次电源,由二次电源经过稳压电源芯片而来。二次电源转换为三次电源一般会采用如图1所示的设计,线性稳压电源模块会产生一个恒定的电压基准,双调压电阻的分压关系决定了三次电源与二次电源的比例,输入端、输出端一般都要对地接入电容,起去耦[2]的作用。

图1 二次电源转三次电源电路原理图

2 FPGA供电网络工作在亚稳态的原因分析

在通用输入输出模块出现上电BIT故障时,3.3 V电源的波形出现震荡。上电BIT过程中,3.3 V电源的最低电压约2.50 V,最高电压约4.2 V,远超出FPGA正常工作的电压范围3.0 V~3.6 V。

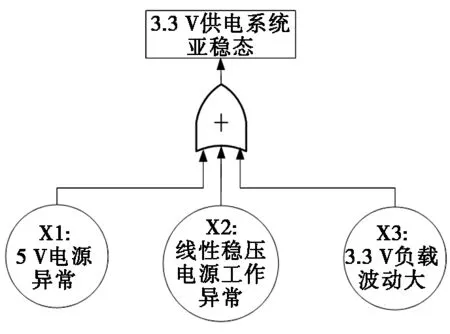

对该问题产生的原因进行分析,图2为造成3.3 V供电网络工作在亚稳态的故障树。

图2 3.3 V供电网络工作在亚稳态的故障树

从测量结果看,5 V电源的电压是比较稳定的,因此可以排除底事件X1。将线性稳压电源与后级负载之间的连接断开,测试3.3 V电源的波形,电压较稳定;该模块上5 V转1.5 V电路中使用的线性稳压电源芯片与5 V转3.3 V电路中的线性稳压电源芯片为同型号产品,1.5 V电源轨工作稳定,综上,可以排除底事件X2。因此,3.3 V电源系统工作在亚稳态的原因应为:3.3 V电源的负载电流波动较大,超出了线性稳压电源芯片可正常工作的负载电流范围,3.3 V电源电压出现大幅度波动。

3 3.3 V供电网络亚稳态问题的解决方案研究

3.3 V电源的主要用电负载是FPGA器件的各IO接口。当复位信号有效后,FPGA的各输出接口被初始化,每个输出接口的扇出电流[3]基本是稳定的,不会导致3.3 V电源电压震荡不稳定的情况,所以重点关注从上电开始到FPGA执行复位操作这段时间,FPGA的各输出接口的扇出电流变化情况。当前对外部复位信号的处理方法是:对外部输入的复位信号SYSRESET进行6个周期的同步处理[4],最后一级的同步信号作为FPGA内部的复位信号FRESET,该信号有效后,FPGA的各输出接口被初始化。据此分析,在外部输入信号的同步过程中,FPGA的各输出接口存在或“高”或“低”的非稳定态,这是导致3.3 V电源网络波动的原因。

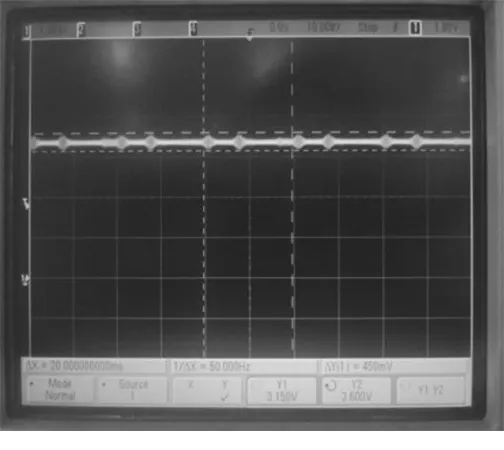

对可编程逻辑设计进行优化,对外部输入复位信号SYSRESET不再进行同步处理,直接将外部输入复位信号传送至FPGA内部复位信号FRESET。可编程逻辑优化后,模块上3.3 V电源网络的波形如图3所示。

图3 可编程逻辑优化后3.3 V电源震荡情况(总体视图)

相比可编程逻辑优化前,3.3 V供电网络的品质明显得到了改善,但仍有小幅震荡。为进一步研究减小3.3 V电源震荡幅度的方案,使用安捷伦ADS2016软件对3.3 V电源网络进行仿真,仿真拓扑如图4所示。其中,R1与L1为电源的寄生参数,R2与L2为印制电路板的寄生参数,四个电流源是为了模拟不同频率的负载电流变化,负载电流的频率依据图5中实际测量到的负载波动频率设定,分别为35 kHz、40 kHz、45 kHz、50 kHz。拓扑图下方为二次电源转三次电源电路中的去耦电容。

图4 3.3 V电源网络初始状态仿真拓扑图

先将去耦电容设置为当前使用的0.1 uf,仿真结果显示,3.3 V电源波动为3.14~3.62 V,与图3所示的实测结果基本一致。

分别在输入端和输出端上增加对地的更大容量的去耦电容[5](原0.1 uf电容保留),根据仿真结果进行逐次迭代,寻找最优解。当输入端对地增加一个47 uf的去耦电容,输出端对地增加一个100 uf的去耦电容后,3.3 V电源的仿真结果如图5所示,其电压仅在3.26~3.34 V之间波动,相比未增加大容量去耦电容前的仿真结果,3.3 V电源的品质得到了明显的提升。

图5 输入输出端增加大容量去耦电容后3.3 V电源波形仿真图(总体视图)

基于上述仿真结果,在通用输入输出模块上进行实验验证。输入端增加47 uf去耦电容,输出端增加100 uf去耦电容后,3.3 V电源的波形如图6所示。

图6 去耦电容增大后3.3 V电源波形

可以看出,3.3 V电源的电压非常稳定,基本没有震荡。因此,大容量去耦电容的增加可以在可编程逻辑优化的基础上更进一步减小3.3 V电源的震荡,保证了3.3 V电源的稳定性,消除了FPGA供电网络工作在亚稳态的风险。

4 总结

本文首先介绍了FPGA供电网络的设计方案,然后就实际工程应用中FPGA的3.3 V供电网络工作在亚稳态的问题进行了原因排查、仿真分析,根据排查结果,对可编程逻辑中复位信号的处理进行了设计优化,同时基于仿真结果,在3.3 V供电网络的输入和输出端分别增加大容量去耦电容,最后的实验结果表明,该解决方案对减小3.3 V电源震荡、消除3.3 V电源网络的亚稳态、提高FPGA的工作可靠性方面具有明显的效果。