p-GaN HEMT器件动态栅应力下的性能退化机理

2023-01-05黄静雯刘斯扬孙伟锋

黄静雯 李 胜 张 弛 刘斯扬 孙伟锋

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

氮化镓高电子迁移率晶体管(GaN HEMT)作为功率器件之一,凭借其临界击穿电场高、二维电子气(2DEG)迁移率高、开关速度快的特点,成为高频电力电子系统中的首选方案[1].传统GaN HEMT为常开器件,在系统应用中会增加功率损耗,并且存在驱动不匹配的问题,从而增加电路设计的复杂度.增强型(E-mode)GaN HEMT由于其常关特性更符合实际应用的需求,受到了广泛关注与研究[2].目前较为常用的2种增强型GaN HEMT分别为p型栅结构GaN HEMT(p-GaN HEMT)和级联型GaN HEMT(Cascode),相比于Cascode结构,p-GaN HEMT器件由于封装形式简单、开关速度快,成为一种主流方式,但相应的可靠性问题应值得关注[3].

在电力电子系统中,功率器件最常见的工作状态为高频下的开关切换,不可避免地需要面对高频动态栅应力考验,但是与金属-氧化物半导体场效应晶体管(MOSFET)器件不同,p-GaN HEMT栅极金属与半导体为肖特基接触,不存在栅氧结构,其栅极可靠性问题是一个值得关注的热点问题[4].近几年,国内外一些研究人员对p-GaN HEMT在高温栅偏实验(HTGB)、负栅压应力、动态栅应力下的电学特性展开相关研究,发现在静态正栅压应力下阈值电压存在正漂和负漂的现象、动态栅应力下只有阈值电压正漂现象以及负栅压应力下导致导通电阻退化的现象等[5-7].然而HTGB为静态栅应力考核,负栅压应力为一种加速老化的考核手段,无法全面反映p-GaN HEMT在实际工作状态下的电学参数退化情况;已有的动态栅应力研究缺少对比实验和仿真分析手段,且传统的测试电路切换时间长,测量误差大,有待进一步改进.

鉴于此,本文设计了一种双管控制快速切换测试电路,可实现在器件施加应力后300 ns内精确测量器件导通电阻Ron及阈值电压Vth;通过控制不同应力状态(开关应力、栅压应力、漏压应力)下的实验以及计算机辅助设计软件(TCAD)仿真分析,对动态栅应力下器件的性能退化机理进行了详细探讨.

1 器件结构及实验平台

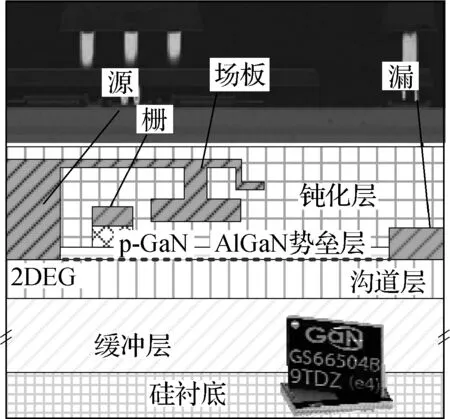

本文选用一款商用650 V增强型硅基GaN HEMT(GaN Systems公司的GS66504B)为待测器件(DUT),具体器件结构如图1所示.

图1 器件剖面结构图

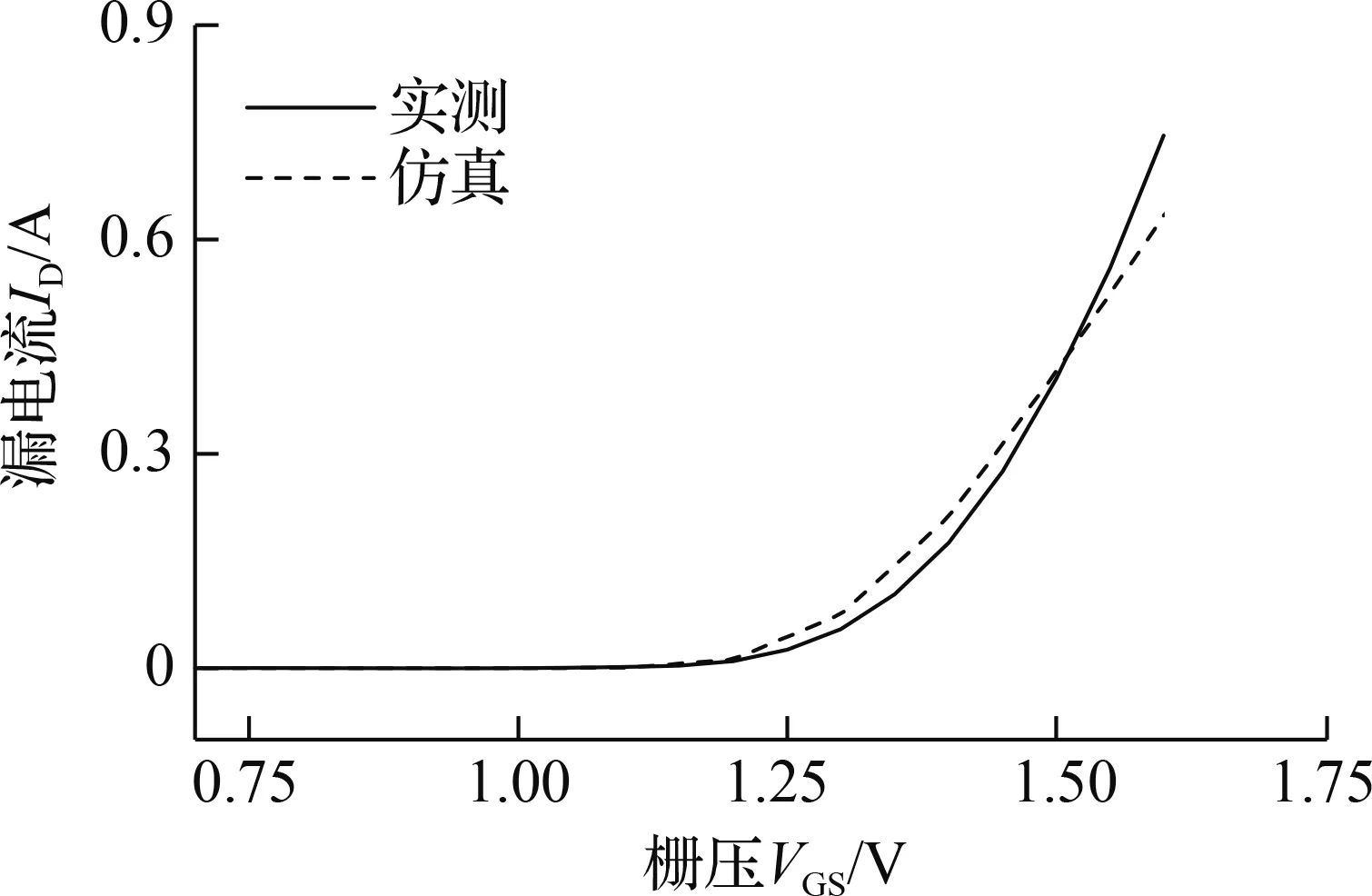

GS66504B为p-GaN栅结构,栅极与p-GaN的接触为肖特基接触,p-GaN层的厚度为110 nm,长度为1.4 μm(即栅长),栅源距离为0.5 μm,漏源距离为17.5 μm,采用源极场板结构.基于上述结构参数,采用TCAD仿真软件Silvaco对该器件结构进行搭建,并在仿真中加入高场迁移率模型(GaNsat.n)、碰撞电离模型(selb)、低场迁移率模型(albrct.n)以及极化效应模型(ten.piezo)等进行电学参数校准,其转移特性仿真曲线(仿真条件为漏压1 V)和输出特性仿真曲线分别如图2(a)和(b)所示.转移特性曲线反映器件漏极到源极间的电流(漏电流ID)随栅极电压(栅压VGS)变化的趋势,输出特性曲线则表示栅压取固定值时器件漏电流ID随漏极电压(漏压VDS)变化的趋势.与半导体功率器件分析仪(B1505)实测曲线进行对比,基于Silvaco的仿真曲线与实测曲线基本吻合,说明仿真效果良好,具备参考价值.

(a) 转移特性曲线

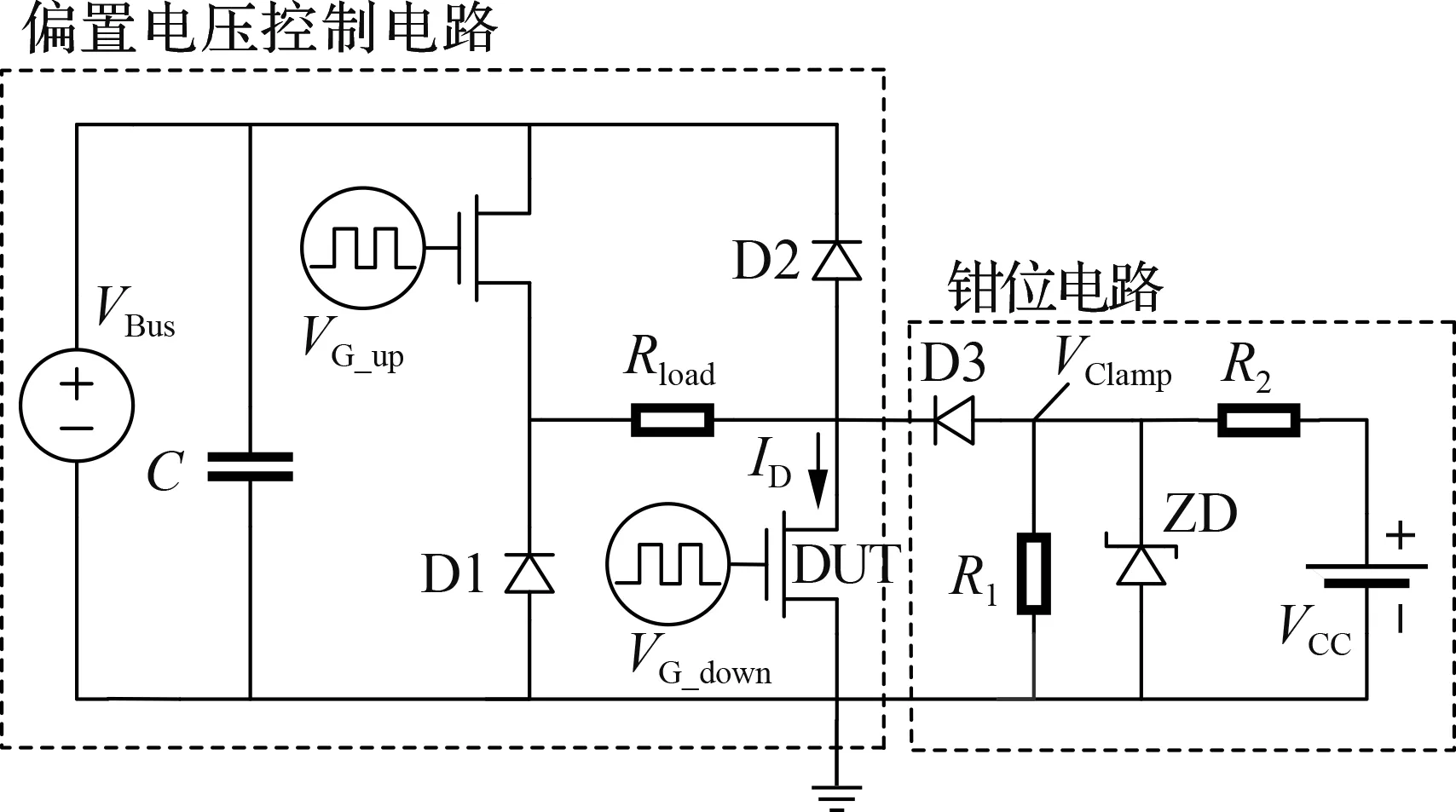

本文设计了一种双管控制快速切换的测试电路,可通过上管的导通与关断实现应力阶段与监测阶段的快速切换.待测器件的导通电阻可以通过测量电路中器件导通电压VDS(on)和导通电流(漏电流ID)来获得[8].具体的测试电路如图3所示,图3(a)为测试电路的原理图,偏置电压控制电路由电源电压(VBus)、滤波电容(C)、上管和下管(下管为待测器件DUT)、2个高压二极管(D1、D2,C3D10060A)以及负载电阻(Rload,2 Ω)组成.其中,上管和下管的栅极脉冲信号(VG_up、VG_down)由函数发生器提供;钳位电路由2个电阻(R1、R2,151 Ω)、二极管(D3,C3D12065A)、稳压二极管(ZD)组成,由小电源VCC供电,通过稳压二极管将下管关断状态时承受的高漏压钳位在一个较小的值以提高测量精度[9-10].所搭建的测试平台如图3(b)所示,主要仪器有函数发生器、示波器、电源,通过电压探头、分流器等探测DUT的漏压VDS、漏电流ID以及钳位电压VClamp.

(a) 测试电路原理图

2 测试方法

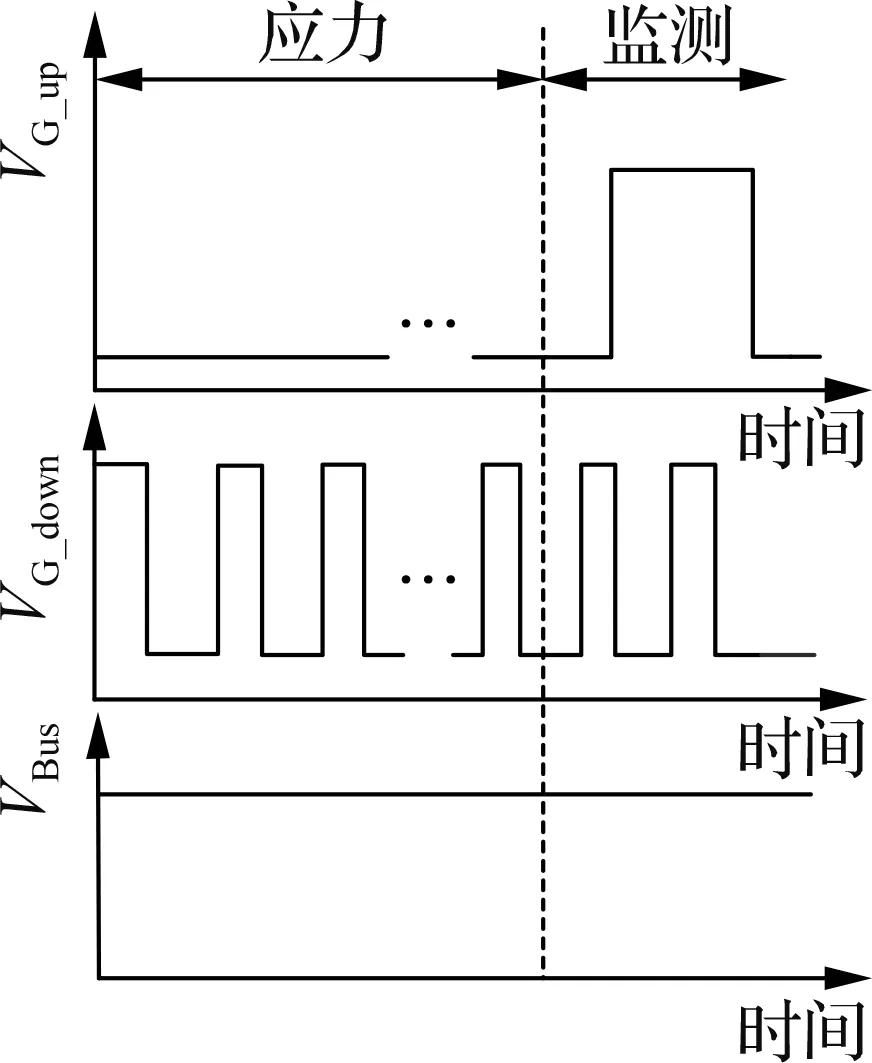

动态栅应力过程中包括3种应力状态,通过控制上管栅信号(VG_up)、下管栅信号(VG_down)和电源电压(VBus),在测试电路可实现对器件施加3种不同状态的应力,同时监测器件电学参数的退化情况.如图4所示,每种应力状态的控制波形均包括应力阶段和监测阶段,器件在应力阶段承受一定时间的应力之后,可在监测阶段对器件的电学参数退化情况进行实时监测.

图4(a)为栅压应力状态,下管栅信号VG_down为脉冲波,VBus为高电平5 V,为避免下管承担漏压,令上管栅压为低电平使其关断,从而使下管只承受栅压应力;图4(b)为开关应力状态,VBus为高电平5 V,上管栅压为高电平使其导通,下管在动态栅脉冲下重复开关,承受开关应力;图4(c)为漏压应力状态,这里需要注意的是,在图3(a)所示的偏置电压控制电路中,电源电压通过直流电源来实现,无法施加脉冲形式的漏压应力,因此需要切换电压源.如图4(d)所示,脉冲形式的漏压应力可用2461源表来实现,上管为高电平导通,去掉回路中的负载,上管源极与下管的漏极直接短路连接,下管为低电平关断时承受脉冲形式的漏压应力.

(a) 栅压应力下控制波形

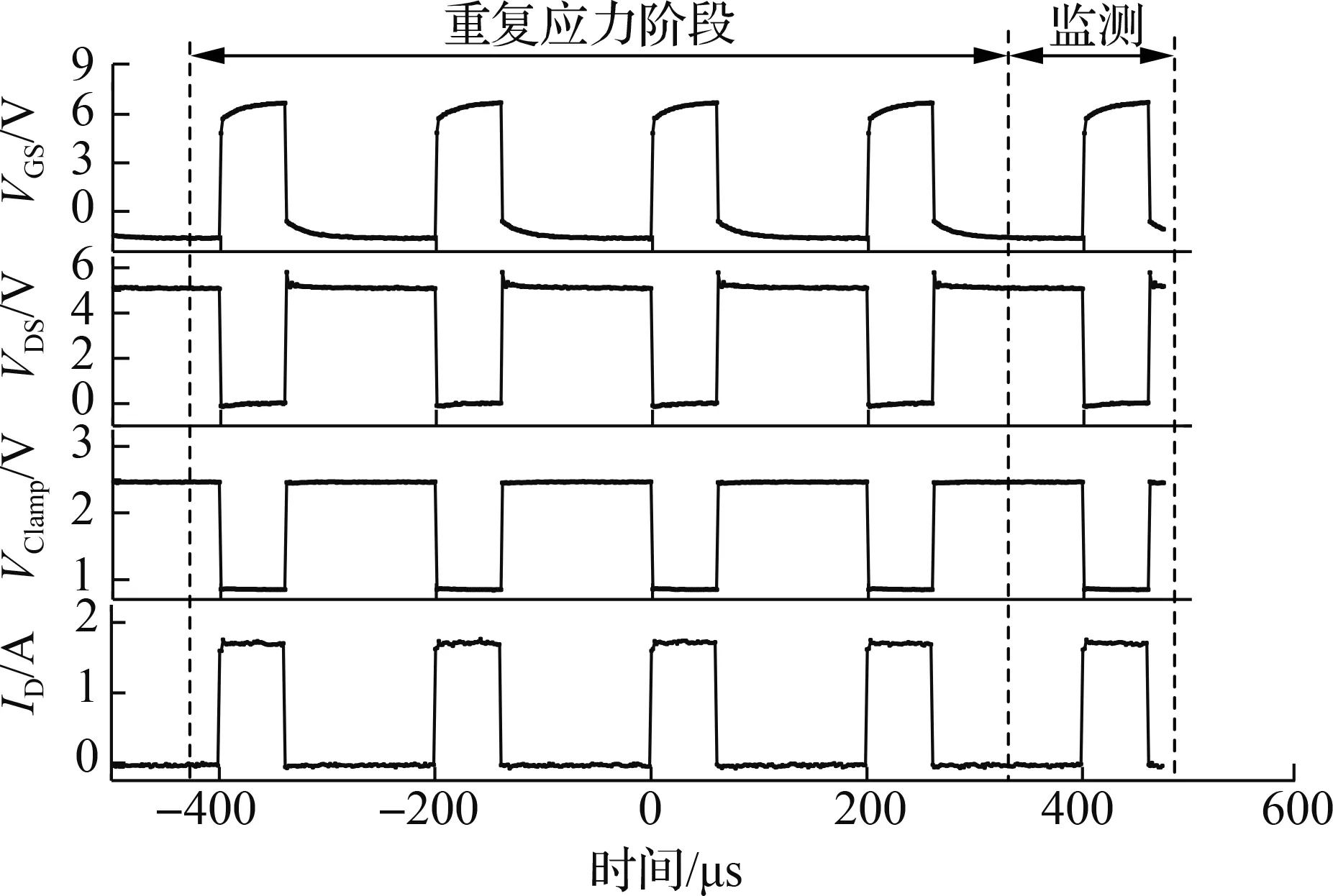

如图5(a)所示,实验波形包括重复应力阶段和监测阶段,器件在应力阶段承受一定时间的应力之后,可在监测阶段对器件的电学参数退化情况进行实时监测,其中VGS、VDS、ID分别为待测器件的栅压、漏压、漏电流,VClamp为钳位电路的钳位电压.图5(b)为待测器件在监测阶段的实测波形图,当下管导通时,在VBus作用下上管、负载电阻、下管之间形成通路,下管有漏电流流过,通过增大下管栅极的上拉电阻值(采用200 Ω),可延长器件的开启时间.如图5(b)所示,下管开启时栅压VGS和漏电流ID均有一个较为缓慢上升的过程,本次测试读取漏电流ID=0.1 A时对应的栅压作为阈值电压Vth.根据图3(a),下管导通时,钳位电压(VClamp)包括钳位电路中二极管D3上的压降(VD3)以及下管的导通压降(VDS(on)),导通电阻值可通过下管导通时的波形读取[11],即

(a) 动态栅应力下待测器件实测波形图

3 实验结果与讨论

3.1 不同应力状态下变频测试

为了研究增强型p-GaN HEMT在动态栅应力下的退化情况,本文选用的动态栅应力条件为漏压VDS=5 V,栅压VGS=6.5 V,Rload=2 Ω,脉冲占空比为30%.测试条件漏压设置为5 V是为了让器件开启有电流流过,从而可以对导通电阻和阈值电压进行测量,且漏压为5 V,与其耐压650 V相比非常小,可避免漏压应力对器件的影响.在上述条件下,对待测器件进行频率为0.01、0.1、5、10、50 kHz的动态栅应力测试.所有测试过程在室温下进行,对器件的电学参数进行监测,包括导通电阻、阈值电压等.结合器件电学参数随有效应力时间的退化情况,分析器件在不同频率动态栅应力下的退化机理.有效应力时间如图6所示,为栅极开启的时间.

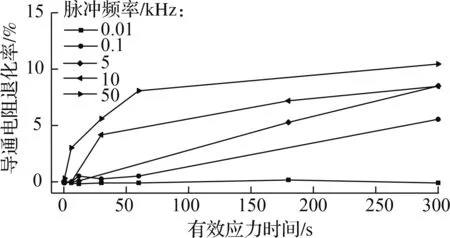

器件不同频率条件下动态栅应力后的电学参数退化情况如图7所示.由图7(a)可知,随着有效应力施加时间的增加,器件导通电阻退化率也随之增大,当有效应力施加时间达到300 s时,器件导通电阻退化率可高达10.82%;且动态栅应力脉冲频率越高器件导通电阻退化率越大,施加有效应力300 s后器件导通电阻退化率由0.01 kHz下的-0.087%增长为50 kHz下的10.82%,说明相同时间内器件开关次数越多,导通电阻退化越明显.图7(b)为阈值电压变化情况,随着有效应力施加时间的增加,阈值电压略有波动,施加有效应力300 s后阈值电压退化率仅为2%,可认为在本次测试的动态栅应力条件下器件的阈值电压没有产生退化,且与频率无关.由于本次测试的动态栅应力条件下器件漏压和漏电流都比较小,可认为器件导通电阻的退化既不是长时间承受大电流引起,也不是高漏压下存在的电流崩塌现象引起[12],需要进一步探究动态栅应力下器件导通电阻的退化机理.

图6 器件开关过程栅压和漏压波形图

(a) 导通电阻退化率

为了探究动态栅应力对器件导通电阻退化的影响,首先应排除关断持续阶段漏压应力对器件的影响,同时应进一步研究导通持续阶段栅压应力对器件的影响.按照图4(c)设置控制信号,漏压应力条件为漏压VDS=5 V,栅压VGS=0 V,2461脉冲频率选取5、10 kHz,占空比同样设置为30%,其他测试条件相同.器件在施加300 s有效漏压应力后的退化情况如图8(a)所示,在漏压应力下,导通电阻的退化率小于2%,阈值电压略有波动,说明漏压应力对器件的影响并不显著.同样,按照图4(a)设置控制信号,栅压应力条件为栅压VGS=6.5 V,漏压VDS=0 V,栅压脉冲频率为5、10、50 kHz,占空比30%,其他测试条件相同.器件在施加300 s有效栅压应力后的退化情况如图8(b)所示,导通电阻和阈值电压几乎均没有退化,说明栅压应力对器件的影响也不显著.

(a) 漏压应力下导通电阻和阈值电压退化率

3.2 机理分析

首先应明确器件在动态栅应力下为重复开关状态,如图6器件单次开关过程栅压和漏压波形图所示(其中漏电流与栅压变化趋势一致),存在开启、导通持续、关断以及关断持续的工作阶段.器件在单次开关过程中不同阶段承受不同的应力:① 在开启、关断阶段,器件从开启到完全导通和从导通到完全关断存在一定的缓变时间,漏压和漏电流同时存在均不为零,此时器件承受开关应力;② 在导通持续阶段,器件完全导通,漏压被拉低到低电位近似为零,此时器件承受栅压应力;③ 在关断持续阶段,栅压为低电位,器件完全关断,此时器件承受漏压应力[13].由上述分析可知,器件在单次开关过程的不同阶段所承受的应力不同,对器件退化的影响不同.其中开启、关断阶段漏电流和漏压同时存在,有热载流子产生,存在一定的功率损耗,且相同应力时间下频率越高开关次数越多,导通电阻退化越明显,因此这一阶段对器件导通电阻退化的影响最为显著.

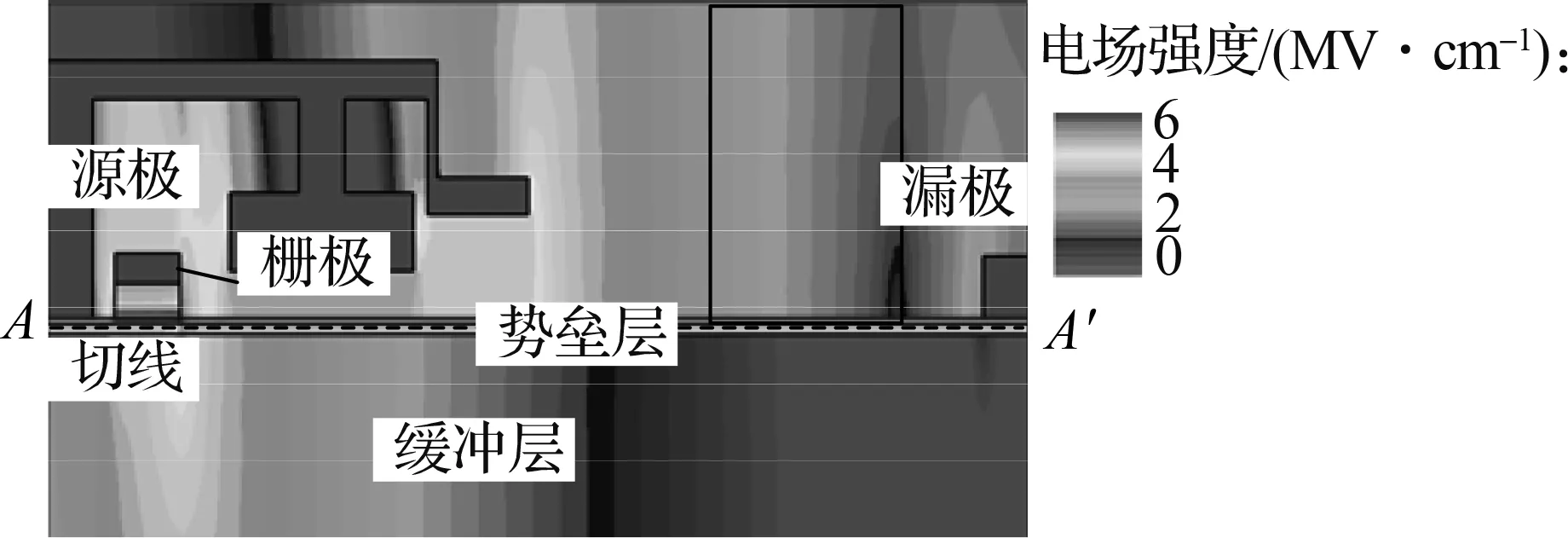

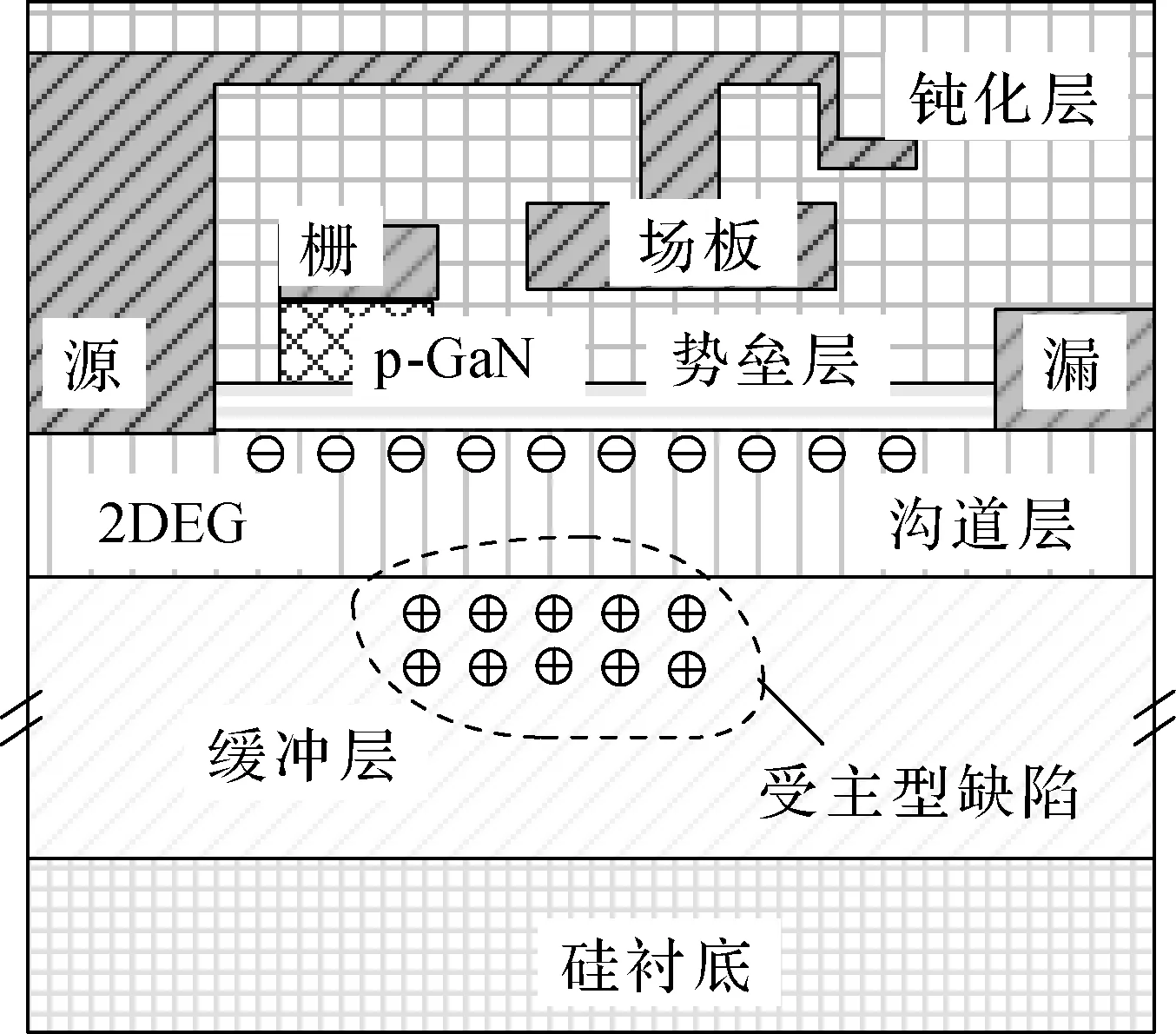

根据测试结果可确定器件在动态栅应力过程中导通电阻产生退化的阶段,为了更加深入地探究器件导通电阻退化的机理,可利用Silvaco仿真软件进行混合仿真,模拟器件动态栅应力过程,并提取器件在开启、关断阶段的电场强度和电流密度[14].图9为器件在开启、关断阶段的势垒层电场强度、沟道电流密度分布图,其中AA′线表示沿势垒层切线进行电场强度的提取.可以看出,在动态栅应力的开启、关断阶段,栅极靠近漏极一侧存在一个强电场,同时在该状态下,沟道中有较大的电流并且存在大量的可自由移动的电子空穴对,在强电场的作用下,存在碰撞电离、热载流子注入的风险.同时,通过仿真模拟缓冲层内产生缺陷对导通电阻退化的影响,可定量分析动态栅应力下缺陷产生数量以及缺陷分布情况[15].具体做法是在缓冲层中加入陷阱模型,通过改变缺陷浓度观察其对导通电阻退化的影响.图10(a)和(b)阐明了缓冲层中缺陷浓度对导通电阻退化的影响,其中导通电阻读取输出曲线上漏压为2 V的对应值.当缺陷浓度达到6×1011cm-2,导通电阻退化率为9.7%,而本次测试中导通电阻的退化率最高为10.82%,说明本次动态栅应力下缺陷浓度的量级大约在6×1011cm-2以下.

(a) 器件剖面图

(a) 缓冲层缺陷

3.3 讨论

导通持续阶段漏压为零,只承受栅压应力;关断持续阶段器件无电流,承受漏压应力.在这2个阶段的应力下,随着时间增加,器件导通电阻没有明显退化,说明器件在动态栅应力下导通电阻的退化不是由于电流崩塌现象引起.由于本次测试施加的漏压较低,表面陷阱捕获的作用不大,且器件应力后阈值电压基本没有变化,说明器件退化也不是由势垒层陷阱捕获电子引起,这与文献[16]的研究结果一致.

结合图9器件电学特性仿真结果,在开关应力下,栅极靠近漏极一侧存在强电场和大电流,由于碰撞电离,在缓冲层会产生热载流子(电子空穴对).在电场的作用下热载流子(空穴)注入到沟道层,与沟道层的二维电子气2DEG复合,使输出电流减小,从而导致导通电阻增大,且相同频率下应力时间越长、相同应力时间下频率越高,导通电阻的退化越明显,说明开关次数越多导通电阻退化越大.并且根据图10的仿真结果,可知动态栅应力下缓冲层中缺陷量级大约在6×1011cm-2以下.为提高器件的可靠性,减少性能退化,应减小器件在动态栅应力下的电场峰值.从器件设计的角度应考虑T型栅、改进源极场板或栅极场板结构,均可减小栅极下方靠近漏极一侧产生的强电场[17].从应用的角度,应考虑用于软开关电路,避免电压电流交叠,采用较小的栅电阻,减小栅开启、关断时间,以及降级使用等均可提高器件的可靠性.

4 结论

1) 设计了一种快速测试电路,通过上管调控下管的应力状态,可实现器件应力后300 ns内精确测量器件的导通电阻、阈值电压.

2) 基于本文提出的测试电路进行实验,对一款商用650 V p-GaN HMET在动态栅应力下的性能退化现象进行了研究.发现在施加不同频率的动态栅应力后器件导通电阻发生明显的退化,阈值电压基本没有退化;并且随着有效应力时间的增加以及频率的增加,导通电阻退化率也随之增大,300 s有效应力时间后导通电阻退化率最高达到10.82%.

3) 结合TCAD仿真分析手段,导通电阻的退化是由于开启、关断阶段缓冲层中碰撞电离产生的热载流子(空穴)注入到沟道层引起的,且通过仿真定量分析出动态栅应力下缓冲层缺陷浓度量级大约在6×1011cm-2以下.可从减小栅极下方靠近漏极一侧电场峰值角度来进行器件结构优化设计,并在应用中考虑软开关电路来提高器件的可靠性.