某型装备准备与检查组件门限产生单元仿真研究

2022-12-21邓孝元方涛关伟贺中武国营长虹机械厂957部队

■ 邓孝元 方涛 关伟 贺中武/ 国营长虹机械厂 957 部队

0 引言

某型装备在完成装配后和工作前都需要进行准备和检查组件的检测,该组件通过对其部件顺序发送控制信号,启动相关设备,检测各部件反馈回来的信号,以确定这些部件是否正常。

门限产生单元是组件12 个单元中极为关键的一部分,主要承担时序逻辑时钟的产生和门限的触发。由于此单元电路中几乎全部为数字电路,测试对象复杂,既有组合逻辑电路也有时序逻辑电路,一旦出现故障极难排除和修复,造成排故工作费时费力,故需要对此单元的机理进行深入研究分析。Multisim电路仿真软件具有强大的电路仿真功能,可将数模混合电路结合起来,通过此电路仿真软件模拟门限产生单元各模块电路,能够有效地进行器件级别的仿真研究。

1 门限产生单元各模块关键器件及工作原理分析

门限产生单元主要承担时序逻辑时钟的产生和门限的触发,其内部主要为由К134TB1 数据锁定J-K 触发器组成时序组合逻辑电路,四2 输入与非门相互配合使用组成门限产生电路,四2 输入与非门和К134TB1 双J-K 触发器(带清除端)组成清零端电路。

1.1 К134TB1 数据锁定J-K 触发器

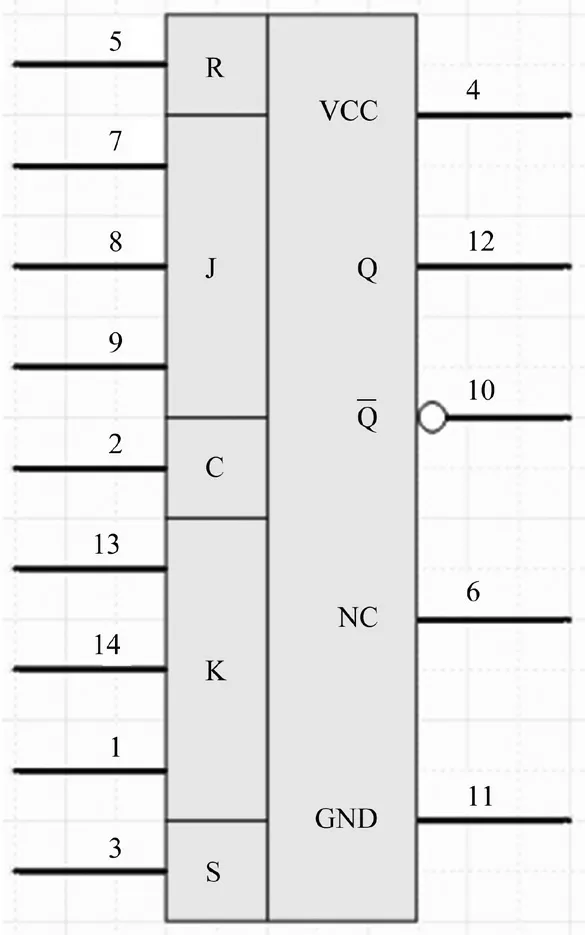

К134TB1 触发器为单片TTL 小规模半导体集成电路,功能为待预置端和清除端的数据锁定(与门输入)主从J-K触发器,属于下降沿触发,其逻辑图和外引线排列图如图1 所示,其输入K 端和J 端符合以下方程:

图1 К134TB1触发器逻辑图和外引线排列图

设输入J 端第7 号、8 号、9 号管脚分别为J11、J12、J13,K 端第1 号、13 号、14号管脚分别为K21、K22、K23,代入式(1)可得:

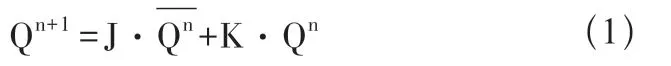

1.2 К133ЛА3 四2 输入与非门

К133ЛА3 四2 输入与非门为单片TTL 小规模半导体集成电路,由4 个独立而又完全相同的2 输入端与非门组成,其逻辑图和外引线排列图如图2 所示,图中未标出的7 引脚为GND,14 引脚为VCC。

图2 К133ЛА3四2输入与非门逻辑图和外引线排列图

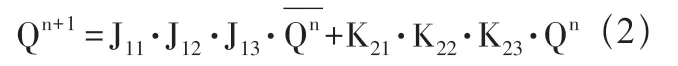

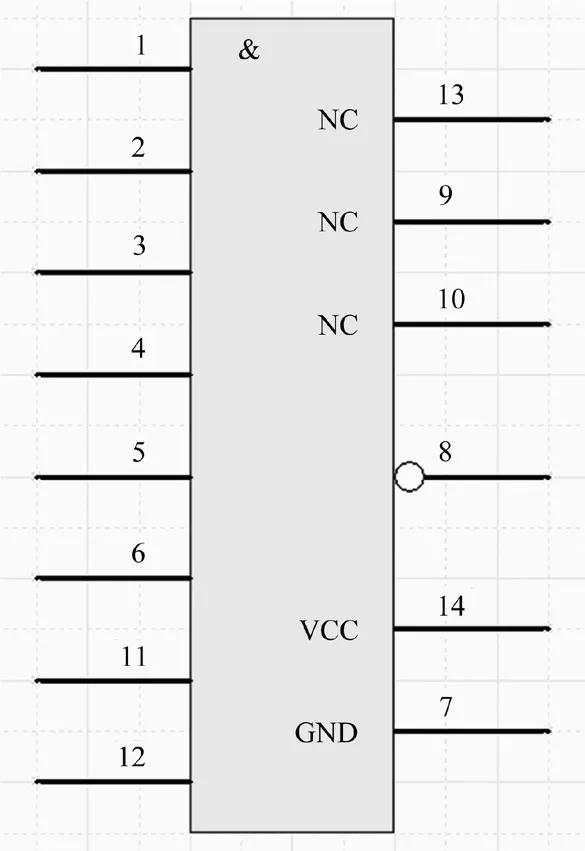

1.3 К133ЛА2 八输入与非门

К133ЛА2 八输入与非门为单片TTL 小规模半导体集成电路,功能为8个输入端与非门组成,其逻辑图和外引线排列图如图3 所示。

图3 К133ЛА2八输入与非门逻辑图和外引线排列图

以上主要对门限产生单元各模块关键器件的工作原理、逻辑图和外引线排列图以及相关功能进行了分析,为下一步研究此单元提供相关的理论基础。

2 门限产生单元各模块仿真分析

2.1 门限产生模块仿真

2.1.1 S 门限产生模块

1)S 门限产生模块工作原理

S 门限产生电路主要由К133ЛА3四2 输入与非门组成,如图4 所示。

图4 S门限产生电路

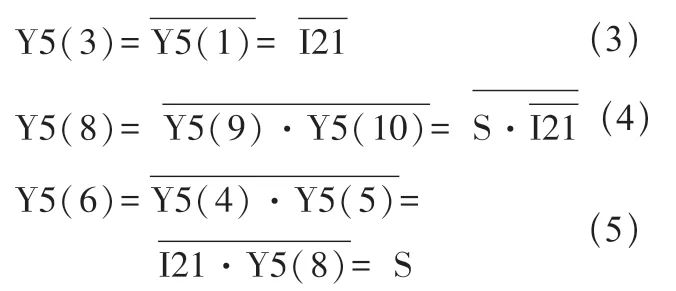

根据Y5 四2 与非门组成的电路,可得出逻辑表达式如下:

其中,Y5(6)表示Y5器件6号管脚,I21 表示插针21。

通过以上各式,可得:

当I21 端输入0 时,Y5(3)输出1,Y5(8)输 出0,Y5(6)输 出1;当I21 端输入1 时,Y5(3)输出0,Y5(8)输出0,Y5(6)输出0。

由此可以得到结论:Y5(6)(即门限S)与非门的输出由插针I21 输入控制。当I21 无输入时,+5V 端强制使I21 置1。

2)S 门限产生模块仿真

S 门限产生模块主要由三个2 输入与非门、两个1kΩ电阻和输入端等组成。通过Multisim 仿真软件搭建此模块仿真电路,如图5 所示。

图5 中,信号发生器XFG1 模拟插针I21 输入控制,示波器XSC1 采集输出端信号(即门限S)。根据插针I21输入的不同信号,产生不同的门限S,将其分为两种信号,即无输入时和输入高低电平(即脉冲信号)时。

图5 S门限产生模块仿真电路

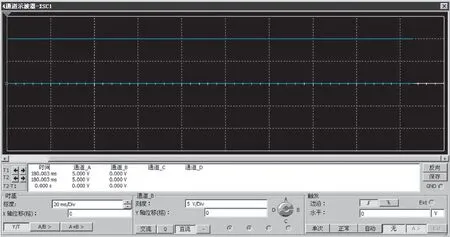

当插针I21 无输入时,+5V 端强制使I21 置1,其仿真结果如图6 所示。

由图6 仿真结果可知,示波器XSC1 通道A 采集到的信号为高电平,通道B 采集到的信号为低电平,产生的门限S 为低电平。

图6 I21无输入的仿真结果

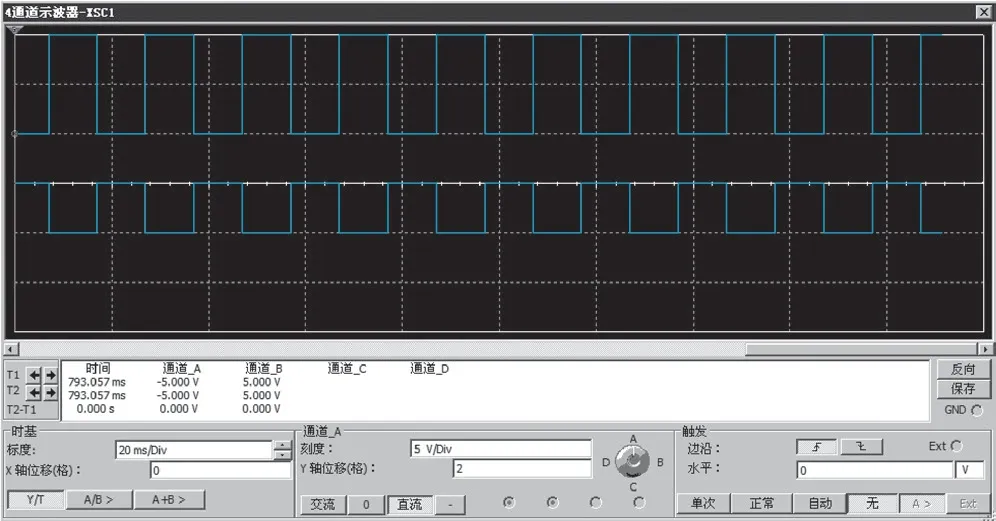

当插针I21 输入频率为50Hz、占空比为50%、振幅为5V 的脉冲信号时,仿真结果如图7 所示。

由图7 仿真结果可知,示波器XSC1 通道A 采集到的信号为插针I21输入的脉冲信号,通道B 采集到频率为50Hz、占空比为50%、振幅为2.5V 的脉冲信号,即此时的门限S。

图7 I21输入脉冲信号的仿真结果

2.1.2 S1 门限产生模块

1)S1 门限产生模块工作原理

S1 门限产生电路主要由К133-ЛА3四2输入与非门和二极管等组成,D2 二极管和D1 二极管为保护二极管,如图8 所示。

图8 S1门限产生电路

根据Y3 四2 与非门组成的电路,可得出逻辑表达式如下:

当I15 输入1,插针I17 输入0 时,Y3(6)输 出0,Y3(3)输 出1;当I15 输入0,插针I17 输入1 时,Y3(6)输出1,Y3(3)输出0;当I15 输入0,插针I17 输入0 时,Y3(6)输出1,Y3(3)输出1;当I15 输入1,插针I17 输入1 时,Y3(6)输出和Y3(3)输出任意。

由此得到结论:Y3(3)(即门限S1)的输出由插针I15、I17 输入共同控制。

2)S1 门限产生模块仿真

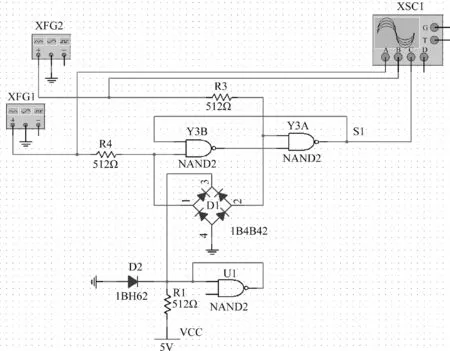

S1 门限产生模块主要由三个2 输入与非门和两个512Ω 电阻、一个1kΩ电阻、二极管以及输入端等组成,通过Multisim 仿真软件搭建此模块仿真电路,如图9 所示。

图9 S1门限产生模块仿真电路

图9 中,信号发生器XFG1 模拟插针I15 输入控制,信号发生器XFG2 模拟插针I17 输入控制,示波器XSC1 分别采集输入端和输出端(即门限S1)信号。根据插针I15、I17 输入的不同信号,将其分为两种信号,即插针I15 分别输入高电平、低电平且插针I17 输入脉冲信号时产生不同的门限S1。

当插针I15 输入低电平且插针I17 输入频率为50Hz、占空比为50%、振幅为5V 的脉冲信号时,其仿真结果如图10所示。

由图10 仿真结果可知,示波器XSC1 通道B 采集到的信号为插针I17 输入的脉冲信号,通道C 采集到频率为50Hz、占空比为50%、幅度为2.5V 的脉冲信号,即当插针I17 输入为高电平时,门限S1 输出为低电平;当插针I17 输入为低电平时,门限S1 输出为高电平。

图10 插针I15输入低电平的仿真结果

当插针I15 输入高电平且插针I17 输入为高电平时,仿真结果如图11 所示。

由图11 仿真结果可知,当插针I15 和I17 输入都为高电平时,示波器XSC1 通道A、通道B 采集到的信号均为高电平信号,通道C 采集到的门限S1 信号在0 ~+5V 范围内不断变化。

图11 插针I15、I17都输入高电平的仿真结果

当插针I15 输入高电平且插针I17 输入为低电平时,其仿真结果如图12 所示。

由图12 仿真结果可知,当插针I15 输入高电平、插针I17 输入低电平时,示波器XSC1 通道A 采集到的信号为高电平信号,通道B 采集到的信号为低电平信号,通道C 采集到的门限S1 信号为高电平信号。

图12 I15输入高电平、I17输入低电平的仿真结果

2.2 时序产生模块仿真

2.2.1 时序CP1 产生模块

1)时序CP1 产生模块工作原理

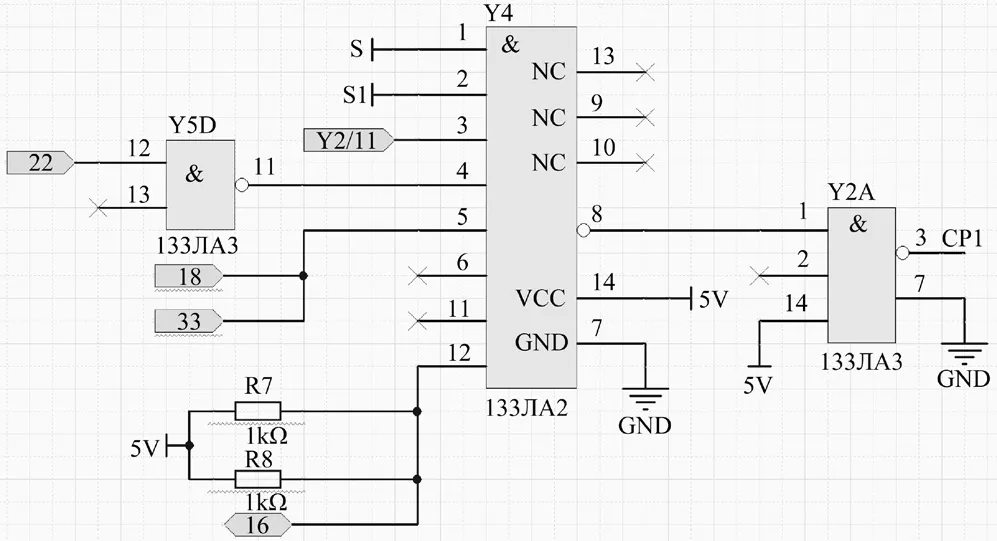

时序CP1 产生模块主要由К133ЛА2 八输入与非门、К133ЛА3 四2 输入与非门、1kΩ 电阻和输入端(S、S1)等组成,如图13 所示。

图13 时序CP1产生模块电路

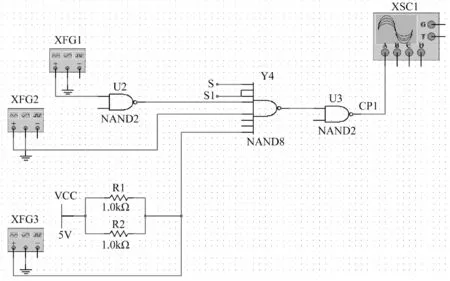

由Y4 八输入与非门组成的电路分析:

由电路可知,Y3(3)=Y2(11),故将式(3)~(6)代入式(7)可得:

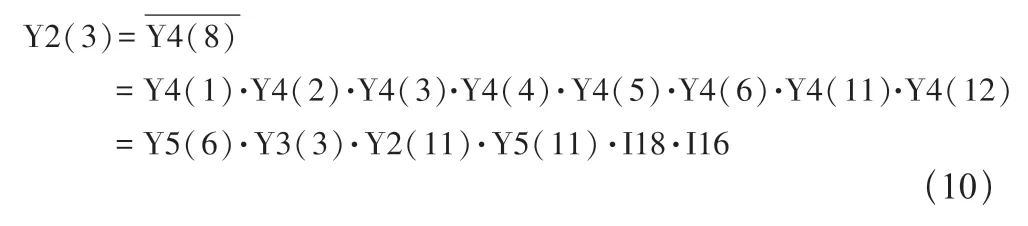

2)时序CP1 产生模块仿真

时序CP1 产生模块主要由К133ЛА2 八输入与非门和输入端(S、S1)等组成,通过Multisim 仿真软件搭建此模块仿真电路,如图14 所示。

图14 中,信号发生器XFG1、XFG2、XFG3 分别模拟插针I22、I18(I33)、I16 输入控制,NAND8 模拟八输入与非门,示波器XSC1 采集输出端时钟CP1 信号。

图14 S1门限产生模块仿真电路

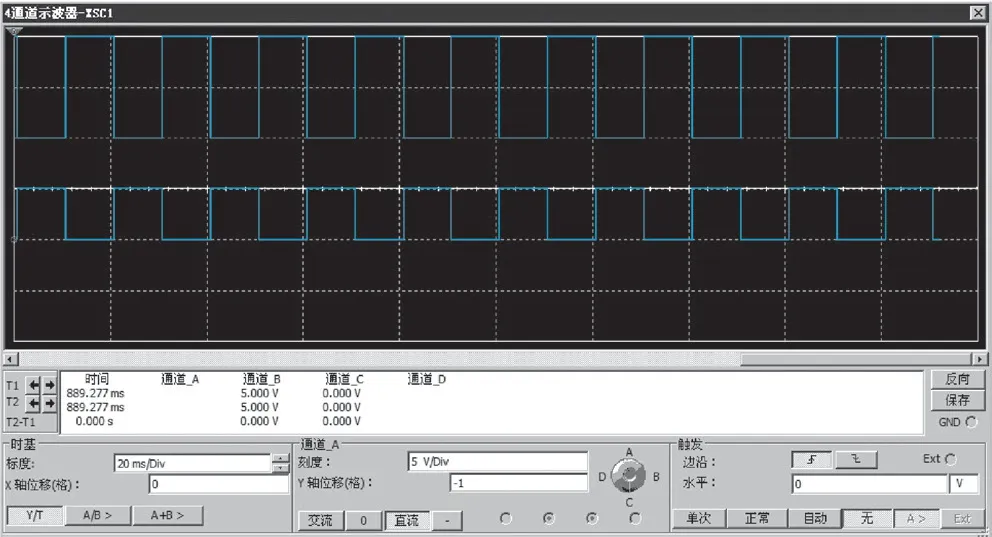

因为CP1 时钟信号由多个输入端共同控制,且输入К133ЛА2 八输入与非门,若有一个输入为低电平,输出都为高电平,故模拟各输入端都输入频率为50Hz、占空比为50%、振幅为5V 的脉冲信号时产生的CP1 信号,仿真结果如图15 所示。

由图15 仿真结果可知,当门限S、门限S1,插针I22、I18、I16 输入一致时,示波器XSC1 通道A 采集到的信号即产生的CP1 时钟信号,为频率50Hz、占空比50%、振幅2.5V的脉冲信号。

图15 门限(S、S1)、插针(I22、I18、I16)输入一致时的仿真结果

2.2.2 时序CP2 产生模块仿真

1)时序CP2 产生模块工作原理

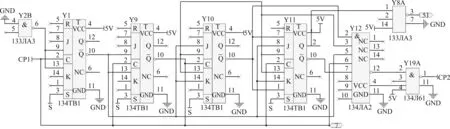

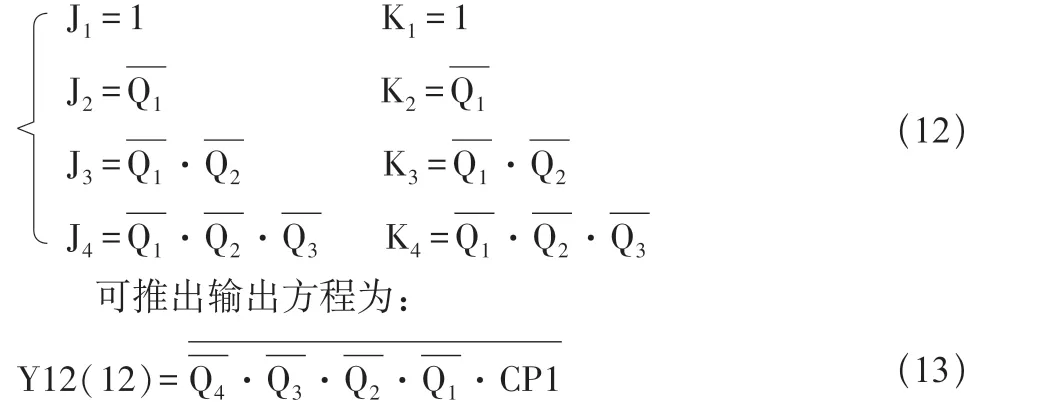

时序CP2 产生模块主要由К134TB1 触发器、К133ЛА2 八输入与非门、К133ЛА3 四2 输入与非门和输入端(S、S1、CP1)等组成,如图16 所示。

通过图16 可知,该电路主要由Y1、Y9、Y10、Y11 四触发器组成,设由Y1、Y9、Y10、Y11 触发器组成的计数器输出现态分别为,次态分别为;输入分别为J1、J2、J3、J4;K1、K2、K3、K4。根据该型触发器的方程式(2),将各式代入得:

图16 CP2产生模块电路

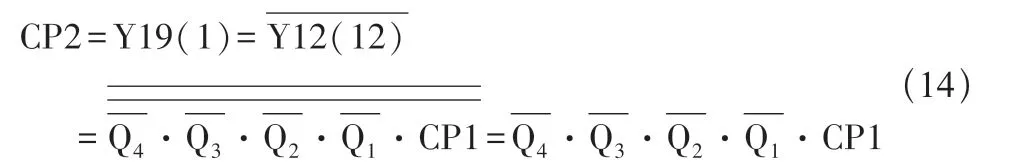

则得出CP2 的逻辑表达式为:

根据式(14)可知,仅当Q1Q2Q3Q4= 0000,且CP1=1 时,Y19(1)=1。

2)时序CP2 产生模块仿真

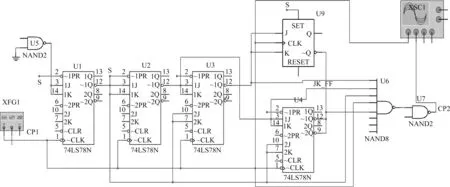

时序CP2 产生模块主要由К134TB1 触发器和输入端(S、S1、CP1)等组成,通过Multisim 仿真软件搭建此模块仿真电路,如图17 所示。

图17 S1门限产生模块仿真电路

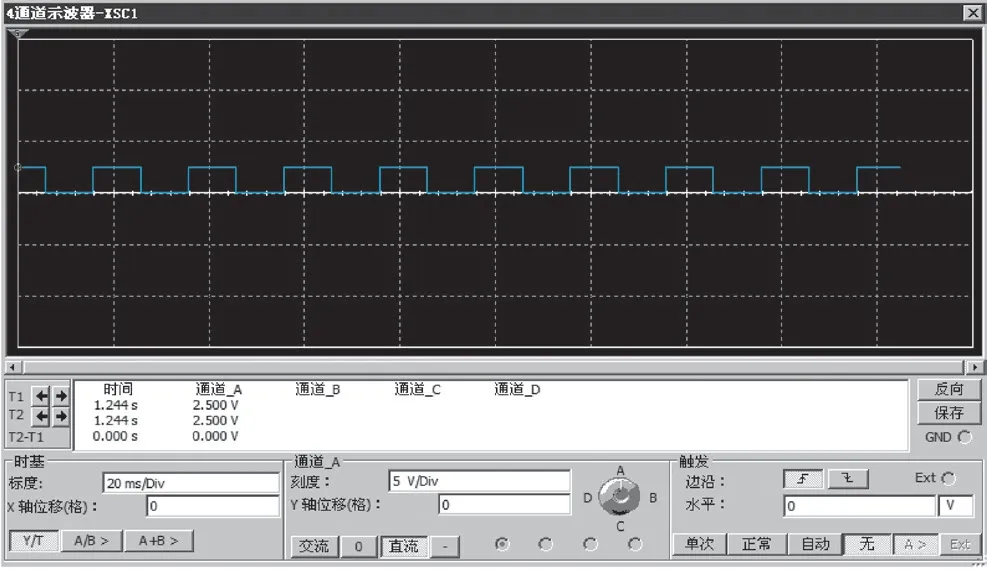

图17 中,信号发生器XFG1 模拟时钟信号CP1 输入,NAND8 模拟八输入与非门,示波器XSC1 的通道A 和通道B 分别采集输入端时钟CP1 信号和输出端时钟CP2 信号。

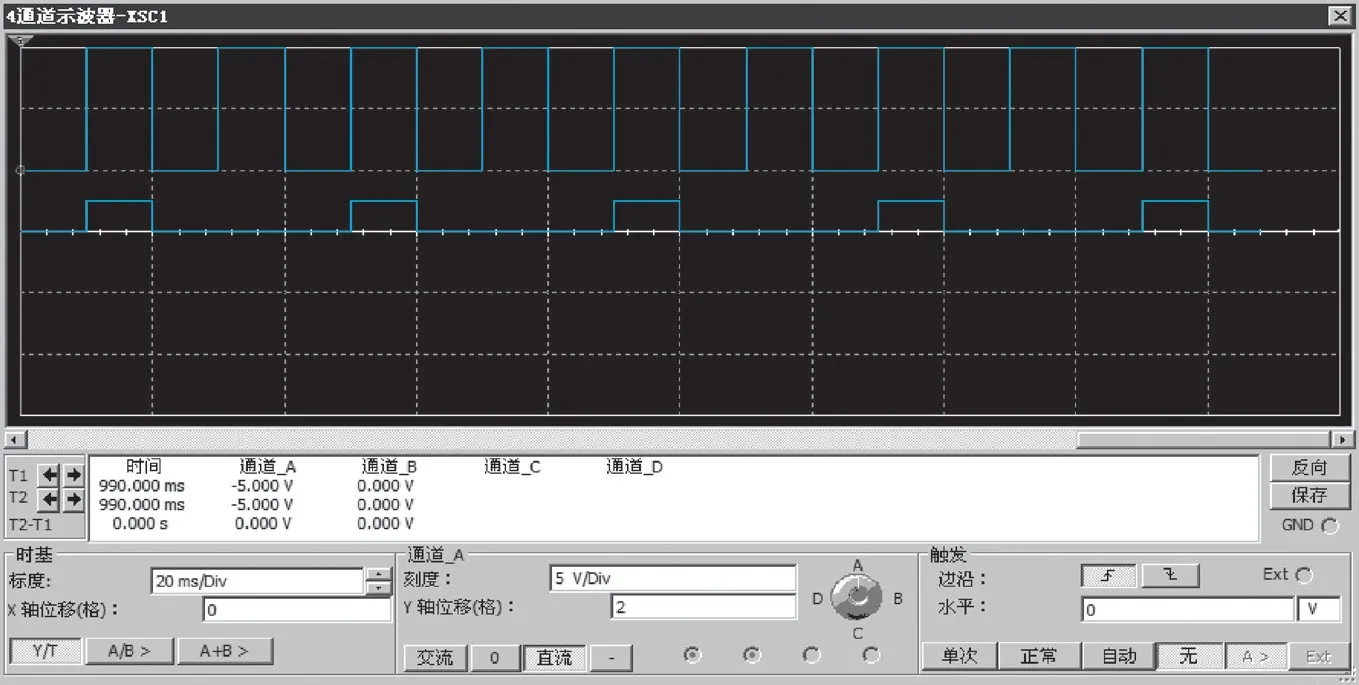

当输入频率为50Hz、占空比为50%、振幅为5V 的CP1 脉冲信号,门限S 输入高电平信号时,仿真结果如图18 所示。

由图18 仿真结果可知,示波器XSC1 通道A 采集到的信号即为输入的CP1 时钟信号,通道B 采集到频率为25Hz、占空比为25%、振幅为2.5V 的脉冲信号,即为产生的CP2 信号,且仅当CP1 信号在第二个周期为高电平时,触发时钟CP2 信号。

图18 时序CP2产生模块仿真结果

以上主要对门限产生单元的门限产生模块、时序产生模块进行了电路原理分析,通过Multisim 电路仿真软件搭建各模块的仿真电路,并进行了模拟仿真,得出了各模块在输入端不同状态下的输出波形。

3 总结

针对某型装备准备和检查组件难以修复的问题,对其门限产生单元的关键器件工作原理及电路原理进行分析,推导出各模块电路的逻辑表达式,得出输入端与输出端的关系。通过Multisim 电路仿真软件对门限产生单元的S、S1 门限产生模块,对CP1、CP2 时序产生模块进行了模拟电路的搭建及仿真,得出在输入端不同状态下各输出端的输出信号。通过对门限产生单元电路的仿真研究,为后续此类问题的修理排故提供一定的理论基础,以提高深修精修能力和修理效率。