基于FPGA 的TDC 测量中占用资源的研究

2022-12-20张雄林王文俊柏森洋

张雄林, 王文俊, 柏森洋

(中国兵器装备集团 自动化研究所有限公司, 四川 绵阳 621000)

0 引言

所谓时间间隔就是一个事物持续的时间, 而时间是一个不可逆的物理量, 所以在时间频率测量领域通常将时间信息转换为可以观测的物理量, 通过比对两者之间的关系来实现对时间间隔的精密测量。 最常见的转换方式就是将时间信号转换为电信号, 再将携带时间信息的模拟信号转换为数字信号,这也就是我们常说的时间-数字转换(Time Interval Convert,TDC)过程。

随着电子技术的蓬勃发展, 对时间间隔进行精确测量的技术方法在导航、通信、光学测量、微电子等领域愈发成熟,基于FPGA 的TDC 设计也得到广泛应用。 然而目前对于基于FPGA 的TDC 技术研究,国内外研究人员大多对TDC 的某一方面进行研究。 普遍存在对于影响系统稳定性的因素没有得到解决导致TDC 精度较差以及TDC 系统占用FPGA 的逻辑资源过多以至于设计的TDC实用价值过低两个问题。

本文针对项目过程中遇到以上问题提出利用改变进位链中部分信号传递方式从而减少TDC 在FPGA 中占用过多资源的问题。

1 测量方法

时间间隔测量的基本原理是利用小时间间隔来测量大时间。 其方法根据适用的场合不同也分为多种:以直接计数法为代表的测量范围大但无法达到理想分辨率的测量方法, 以及以内插法为代表的测量分辨率能够达到一个较高值但测量范围受到限制的方法。

为了实现工程需要, 项目中通常采用将这两种测量方法相结合的方式进行设计。 将整个系统分为“粗”测量模块和“细”测量模块两部分。

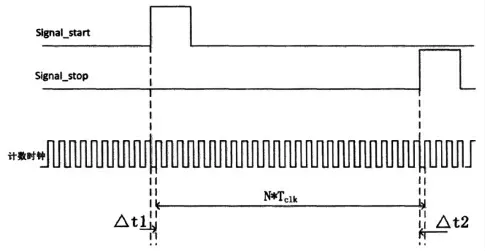

1.1 “粗”测量方法

“粗”测量是通过直接计数法来完成的,即测量出待测的两个信号上升沿之间的时间间隔T 内包含的计数器时钟CLK 的时钟周期数目N。 待测的时间间隔是由起始信号和终止信号两部分组成的,当时钟周期为TCLK 时,起始信号的上升沿和终止信号的上升沿之前的时间间隔T 可以表示为:

其主要用于提高TDC 的测量周期。其原理图见图1。

图1 “粗”测量原理

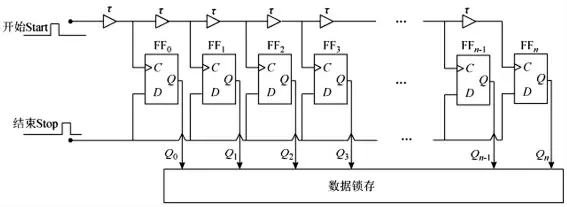

1.2 “细”测量方法

“细”测量采用以延迟为基础的内插法。 由于直接计数法无法对起始信号的上升沿与紧随其后的计数器上升沿之间很小的时间间隔信号△t1,起始信号的上升沿与紧随其后的计数器上升沿之间很小的时间间隔信号△t2,为提高精度,需要将这一小段时间进行量化。以延迟为基础的内插法就时将数个延迟单元用特定技术将其级联起来,再将待测时间间隔引入到该延迟链中,在接收到被测信号的起始信号时启动延迟链, 信号依次通过延迟单元进行传递,在接收到终止信号时关闭延迟链。此时信号会停留在延迟链上的某一延迟单元, 通过记录此延迟单元的位置以及走过的延迟单

元数目即可知道被测信号时间间隔的长度。 其测量原理见图2。

图2 “细”测量原理

2 基于FPGA 的进位链实现TDC

现场可编程门阵列(FPGA)是现阶段数字设计应用最广的硬件平台,它具有开发成本低,可以重复擦除和重写,编写软件方便快捷等特点。 FPGA 内部是由7 部分组成:可编程输入输出单元IOB、基本可编程逻辑单元CLB、丰富的布线、 时钟数字管理模块DCM、 嵌入块式RAM/ROM 等。以Xilinx 公司的FPGA 为例,其基本的逻辑单元为CLB,每一个CLB 包含一个或两个切片(Slice),每个切片提供8 个6 输入的查找表(LUT)、16 个触发器以及一个进位链,切片中的查找表按列排列,见图3。

图3 FPGA 进位链结构

FPGA 内部有许多底层逻辑单元,如LCELL 缓冲单元,非门逻辑单元等,可以串联起来构建延时链,但由于编译器在执行编译过程中对逻辑单元所使用的布局布线资源的分配是自动完成的,不收人为干预,所以往往得到的结果不收设计者所期望的。 如果逻辑单元数目较少,那么可以通过手动更改布局布线方式来完成,但面对数百个单元需要更改位置,需要的工作量非常大,而且很容易出错,解决这一问题的方法就是利用级联链、进位链和寄存器阵列等部件构建延时链。

延迟单元模块由FPGA 内部的加法进位链来实现,信号经过加法进位链中的进位单元时会产生皮秒级别的延迟。 然后利用D 触发器对延时不同的信号进行锁存,进而可以得知被测信号到时钟上升沿之间延迟单元的数目。 信号经过D 触发器时可能会产生亚稳态现象,因此本系统采用两级D 触发器来避免亚稳态的影响。

信号在经过D 触发器后的表示形式是延迟单元数目的温度计码形式,为了方便数据的处理,需要利用编码电路将温度计码转换为二进制码。 由于超前进位链的存在,该温度计码不是严格的温度计码。采用二分法进行计数会漏掉一部分数据, 直接对1 的数目进行计数占用资源又过多。 因此本文的编码电路采用二分法和直接计数法相结合的方法对温度计码进行转换。 具体做法是二进制码的最后2 位由直接计数法得到,其余位由二分法来得到。

3 系统测试与改进

3.1 设计优化

基于项目应用需要, 实际设计过程中FPGA 中能够给TDC 调用的资源有限,同时项目对时间间隔分辨率的要求也不高。 项目所用到的 “粗” 测量时钟的频率为400MHZ,即一个时钟周期为2.5ns,为了实现“粗”“细”相结合的测量方法, 需要设计的 “细” 测量周期需满足╭2.5ns。 然而经过信号在FPGA 内部经过一个逻辑单元所用的时间大概为50ps,达到需求需要调用逻辑单元数N1为:

N1=2.5ns÷50ps≈50

占用资源过大。此外,项目所用FPGA 的CLB 一列逻辑单元数为20 个, 这就意味着如果想要调用全部50 个逻辑单元,需要进行换列操作,而信号经过不同列之间的逻辑单元的时间间隔和同列间的时间间隔是不一致的,这势必会对TDC 的测量精度产生影响。

为了能够减少误差并且降低FPGA 实现TDC 功能时所调用的资源, 需要增加信号在FPGA 进位链中每一逻辑模块的留存时间。 在进位链第一个全加器处的进位信号不直接进入下一级,而是通过C0 输出,经过外部的延时电路再从下一级的S1 口输入,这样会使整个过程多出一段输入信息在进位链外的时间。 通过这种方式可以将TDC 模块的分辨率缩小, 达到分辨率要求所需的级数也相应的减少, 从而降低了FPGA 实现TDC 功能时所占用的系统资源总量。

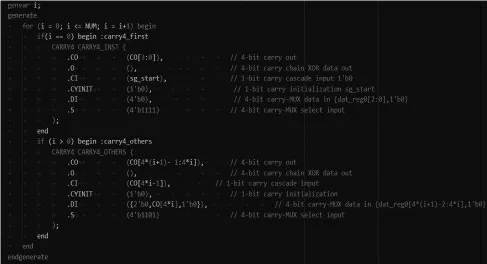

根据上述分析所设计的进位链部分软件程序,见图4。

3.2 测试仿真

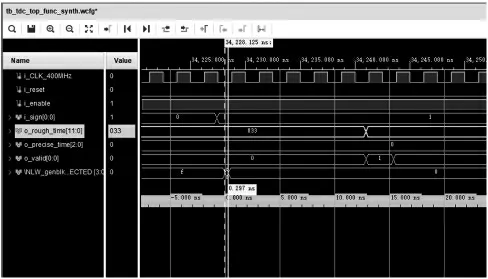

根据图4所设计的软件利用Vivado 软件进行仿真可以得到, 经过处理后的逻辑模块中一段信号的通过时间为297ps。根据之前的分析修改后需要的Slice 逻辑单元数目N2为:

图4 进位链关键部分软件

N2=2.5ns÷297ps≈9

可见实现TDC 实际功能所需的逻辑模块数目大幅减少, 且此数目小于CLB 一列所包含的逻辑单元数目,不需要再考虑换列对时间间隔测量精度的影响。 设计仿真结果见图5、图6。 通过Xilinx 公司系列FPGA 进行所提设计方法的实验验证,取得的结果与仿真结果相仿,说明本文所提设计思路有效解决了在分辨率要求不高时TDC 在FPGA 中所占用资源过大的问题。

图5 软件设计仿真

图6 时间间隔仿真结果

4 结论

本文设计了基于FPGA 的TDC,并利用进位链内外信号转换有效解决了进位链过于占用系统资源导致实际应用过程中使用效果不佳的问题。 并基于Xilinx 公司系列FPGA 利用Vivado 软件进行数据仿真, 实际测得经过优化后的进位链在资源占用方面得到明显优化,为FPGA其他功能的实现节省出足够的资源。