一种新型的抗PAA攻击的双轨预充电电路逻辑

2022-12-05姚茂群薛紫微

姚茂群,薛紫微

(杭州师范大学信息科学与技术学院,浙江 杭州 311121)

0 引言

功耗分析攻击(power analysis attack, PAA)[1]是威胁硬件安全的一种强有力的攻击手段,其利用硬件电路工作过程中必然产生的功耗与其所处理数据的相关性建立信息泄露模型,通过对示波器所采样的能量曲线进行统计学分析,提取出数字电路存储或计算的重要信息,如智能卡的密钥、密码芯片的S盒运算等.

基于PAA的改进攻击方法近年来层出不穷,因此,对PAA的预防措施已经成为工业界和学术界研究的重要方向.功耗攻击防护措施可以分为算法级、系统级和电路级3个方面[2],其中电路级防护措施旨在从底层逻辑电路上根本性地消除由功耗变化所带来的信息泄露.电路级抗PAA方案一般是设计出功耗恒定的逻辑电路,已有学者利用联合的门电路实现了逻辑电路的功耗平衡[3],同时提出新型的门电路设计[4],但考虑到提前传播效应的影响和芯片面积的优化,更多的基于双轨预充电的门电路设计方案被提出[5].通过对现有方案的调研,本文基于双轨预充电逻辑结合行波流水方法设计出一种新的门电路,该电路能平衡功耗且减少芯片中晶体管数量.

1 双轨预充电逻辑

双轨预充电逻辑(dual-rail precharge logic, DRPL)[4]是Tiri等提出的实现功耗平衡的一个重要方法,它基于动态差分逻辑设计[6],因此双轨的输出是一对差分信号,再结合预充电逻辑可以实现每个时钟周期固定不变的功率消耗.

1.1 动态差分逻辑

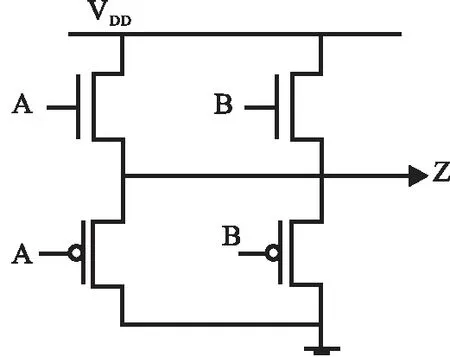

差分逻辑电路的输出端为一对差分信号,图1是由上拉网络和下拉网络实现的差分逻辑,可以看到输出了逻辑上互“反”的一对信号.所以差分电路在任何时刻都有一个“1”和一个“0”的输出,这为电路的功耗恒定提供了一个逻辑上的思路和基础.

图1 差分逻辑Fig.1 Differential logic图2 动态逻辑Fig.2 Dynamic logic

图2 动态逻辑Fig.2 Dynamic logic

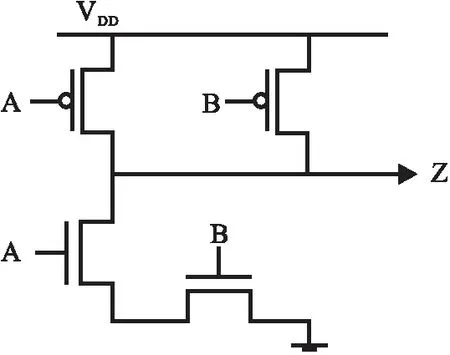

动态逻辑将电路运算分为预充电阶段和求值阶段,如图2所示,在预充电阶段,负载电容将被充电,而在求值阶段,负载电容将会放电.电容放电产生的功耗是PAA的基础,因此如果求值阶段的放电功耗平衡在一个固定的值,将从物理基础上预防PAA攻击.将差分逻辑和动态逻辑结合可以实现平衡功耗的目的.

1.2 双轨预充电实现功耗平衡

将动态逻辑和差分逻辑结合,同时每个输入信号和输出信号均为一对差分信号,这便是本文采用的双轨预充电逻辑[4].由于寄生电容和负载电容效应的影响,数字电路的输出信号在由“1”跳变为“0”或“0”跳变为“1”时会产生功耗,这是功耗与电路中信息的相关性存在的基础.因此,为产生恒定的功耗,就要使电路无论输入信号是什么,在输出端都只出现相同的信号跳变.采用双轨预充电逻辑正是为了实现这一特性.

图3 DRPL实现与门Fig.3 DRPL AND gate

在双轨预充电逻辑中,如图3所示的二输入与门(AND gate),每个输入信号为一对差分信号,即以(1,0)代替传统逻辑电路的逻辑“1”,以(0,1)代替逻辑“0”.每个时钟周期的前半周期为预充电阶段,这一阶段电路的输出端为(0,0);每个时钟周期的后半周期为求值阶段,这一阶段电路进行正常的逻辑运算,因此输出端为一对差分信号(0,1)或(1,0).这种设计保证了在每个时钟周期内电路的输出端要么产生(0,0)到(1,0)的跳变,要么产生(0,0)到(0,1)的跳变,无论哪种跳变,一个周期内均只有一个端子产生“0”到“1”的跳变,而另一个端子不发生跳变,不会有功耗泄露,因此,每个时钟周期内的功耗产生将是恒定的.

而在两个时钟周期之间,输出信号将产生一个由求值阶段的输出到下一周期预充电阶段的输出跳变,即由(0,1)或(1,0)跳变到(0,0),同样只有一个端子产生了由“1”到“0”的信号跳变,因此用DRPL实现的门电路在每个时钟周期中及各时钟周期之间分别产生的功耗是恒定不变的,这样针对功耗的信息泄露分析将无法展开.

2 基于上下拉网络的功耗恒定方案

本文提出一种新型的功耗恒定的门电路设计方案,以与门为例,基于上下拉网络使单轨与门和与非门(NAND gate)实现双轨差分与门逻辑.

2.1 单轨与门和与非门

双轨逻辑的输出端为一对差分信号,因此为实现双轨与门,需要将单轨的与门和与非门结合在一起.基于上下拉网络的单轨与门和与非门设计如图4,其实现结构简单,每个门电路均只采用4个晶体管,这使得基于此的芯片的面积成本大大降低.

与门

与非门

由于本文双轨电路方案采用的输入和输出信号均为差分信号,所以需要将图4单轨门电路的两个输入信号变换为两对差分信号,这也是实现行波流水预充电方法的基础.

2.2 行波流水预充电的双轨与门

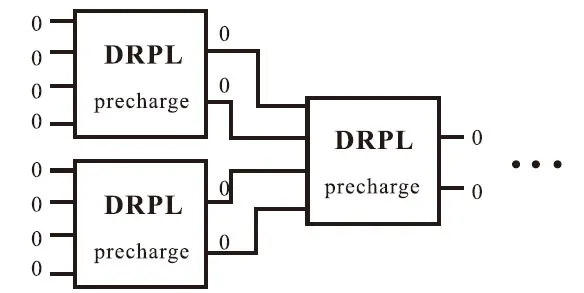

行波流水预充电是指在预充电阶段,预充电信号逐级传递的一种预充电方法.如果采用一个时钟信号控制所有门电路,会对电路的布线带来巨大的挑战.为避免这种时钟信号的“大扇出”问题,同时简化电路结构,拟采用行波流水的预充电方法.从图3可以看出,预充电阶段输出信号为(0,0),可以用时钟来控制实现;但要采用行波流水的预充电逻辑,就需要保证上一级预充电阶段的输出作为下一级的输入,同时实现下一级的预充电.因此在本文的设计中,电路在预充电时,是由输入信号的全“0”实现输出信号的全“0”的.图5展示了预充电阶段前一级的门电路将全“0”的预充电信号传递到下一级,进而实现电路统一预充电的过程.

图5 行波流水预充电Fig.5 Wave precharge

图6 双轨与门Fig.6 Dual-rail AND gate

要实现行波流水预充电,输入信号和输出信号必须都为差分信号,且在预充电时,这些差分信号对不是互补的一对信号,而是均为“0”信号.因此对图4的单轨门电路进行了改进,使其输入也为差分信号,并组合成双轨与门,如图6所示.这里以高电平代表逻辑“1”,低电平代表逻辑“0”,可以看出,在该电路中,当输入信号均为逻辑“0”时,输出信号也均跳变到逻辑“0”,这样就实现了预充电阶段“0”信号的传递,使得预充电之后所有输出信号被置零.

此电路可以完成行波流水预充电,再结合其双轨特性,可以较好地实现功耗恒定.在预充电阶段,输入信号全“0”,输出信号全“0”;在求值阶段,输入信号恢复为差分信号,输出信号也因此变为正常的逻辑值,且是互为相反的信号.因此,在每个时钟周期中,电路只发生了预充电阶段到求值阶段的一次“0”—“1”信号跳变,这使得电路的周期功耗变化是恒定的,消除了功耗分析所依赖的信号与功耗的相关性.

3 实验仿真与验证

3.1 实验结果

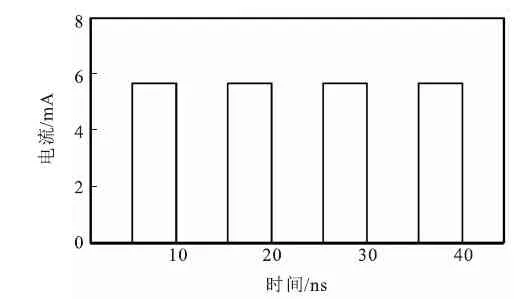

用电路仿真软件Multisim对按照上述思路所设计的电路进行模拟测试,实验结果如下:以时钟信号控制预充电阶段与求值阶段的跳变,当输入信号(A,B)由(0,0)跳变为(1,1)时,输出信号由(0,1)跳变为(1,0),电路的功耗变化情况如图7所示.

图7 输出信号由双轨“0”跳变为“1”时的功耗变化Fig.7 Power consumption of 0-1 switch

图8 输出信号由双轨“1”跳变为“0”时的功耗变化FigFig.8 Power consumption of 1-0 switch

图9 输出信号保持“0”不变时的功耗变化Fig.9 Power consumption of 0-0 switch

当输入信号由(1,1)跳变为(1,0)时,输出信号由(1,0)跳变为(0,1),电路的功耗变化如图8所示.

当输入信号由(0,1)跳变为(1,0)时,输出信号由(0,1)跳变为(0,1),电路的功耗变化如图9所示.

其他信号跳变情况不再一一展示.从实验结果可以看出,无论输入信号如何跳变、输出信号是否保持原值,电路都只会产生一样的功耗变化,由此测量出来的电路功耗波形是周期性变化的,攻击者将无法从中分析出信息泄露.

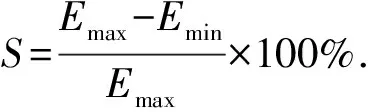

3.2 功耗恒定性分析

为验证本方案的功耗恒定特性,选取输入信号由(1,1)跳变为(1,0)时电源电流的变化情况进行统计分析,得到了本方案在最差情况下的NED值(8.24).WDDL逻辑是Kris等提出的一种抗功耗攻击电路,其NED值为11.50[9-10],可以看出本方案实现的门电路具有更小的功耗偏差.当然,从图8、图9中发现,电路在各周期功耗变化仍存在微小的差异,这是由于晶体管类型的不同及毛刺信号干扰造成的,下一步研究将就这些问题对方案进行再次优化.