基于FPGA的分布式发电系统混合步长实时仿真算法

2022-12-01郑荣波郝正航陈卓

郑荣波,郝正航,陈卓

(贵州大学电气工程学院,贵阳550025)

0 引言

随着越来越多的分布式电源接入配电网,其对配电网系统产生的影响也越来越大[1 - 3]。在电力系统仿真领域,采用基于CPU的仿真技术具有操作简单、成熟度高[4]、低复杂度等优点,被广泛应用于大规模电网及传统输配电系统的实时仿真中。而近年大规模的电力电子设备被应用于新能源并网、分布式电源及电能质量优化等领域[5 - 6],这给传统基于CPU的仿真系统带来了挑战,因此研究含有大量电力电子设备的电力系统实时仿真技术是必要的。

在电力电子技术的快速发展下,电力电子开关频率趋于高频化[7],从几千赫兹到几万赫兹甚至更高,暂态过程更加短暂,因此需要仿真系统能够达到足够小的仿真步长才能保证仿真结果的可靠性(通常在1 μs量级)。然而由于电力电子设备的存在会造成计算矩阵时变[8]、步长间开关动作、数值震荡等问题,想要精确求解的话需要较大的仿真步长,且系统中的逻辑判断众多,计算复杂,加之电力电子设备带来的强非线性导致系统规模庞大,这些原因都导致了小步长实时仿真难以实现。传统的基于CPU的实时仿真器一般只能实现20 μs以上步长的仿真[9],已经满足不了当前普遍的高频电力电子系统实时仿真的要求,因此本文引入FPGA进行联立仿真。

目前,以RTDS和RT-LAB为代表的商业化实时仿真器已经在电力行业获得了广泛应用[10 - 11],且已经开始采用FPGA作为小步长仿真的底层硬件。FPGA由于其强大的完全可配置固有硬件并行结构和深度流水线架构[12],并且可以从底层硬件上实现灵活的布局布线[13],加之其丰富的可配置逻辑资源以及大量嵌入式随机存取存储器(random access memory, RAM)和只读存储器(read-only memory, ROM),使得FPGA具有很强的并行计算能力和数据处理效率,并具备高速仿真的能力,其仿真步长能够达到几百甚至几十纳秒[14 - 15],满足暂态实时仿真的要求。文献[16 - 17]分析了开关状态的变化对电力系统仿真的影响,并计算出所有开关状态的组合进行预存储,但这种方法随着开关元件的增多导致需要预存的节点导纳矩阵数量急剧上升,势必会占用大量硬件资源。文献[18]采用了基于伴随离散电路开关模型(associated discrete circuit, ADC)的电磁暂态实时仿真方法,在FPGA中实现了光伏发电系统的暂态实时仿真,提出了电力电子开关和控制系统建模方法,并对仿真结果进行了精度分析。这种方法可以实现较高的计算精度,但将整个电力系统用FPGA进行小步长仿真无疑会占用大量的硬件资源,限制了仿真系统的规模,且在FPGA上进行复杂控制系统的建模和实时仿真具有一定难度。

针对上述问题,本文提出了一种基于FPGA与CPU的混合步长暂态实时仿真方法。该方法解决了传统方法在电力系统建模时FPGA的资源消耗较大的问题。采用模型分割方法将电力系统分割为大步长仿真部分与小步长仿真部分,CPU负责大步长计算,FPGA负责小步长计算,并采用以太网进行数据交互。其次,为将逆变器交流侧输出电压在不经滤波的情况下发送至CPU侧,提出了一种等效算法,对交流侧输出电压求均值后再进行发送,以此解决数据交互中产生的误差问题,同时该方法能够进一步降低FPGA硬件资源占用率。最后,利用ADC开关模型搭建了光伏发电系统,将系统的实时仿真结果与Simulink离线仿真结果进行对比,验证了实时仿真方法的可行性和准确性。

1 基于FPGA的电磁暂态实时仿真算法

传统的离线电磁暂态仿真软件,如Simulink、PSCAD等,一般是运行在基于计算机CPU的仿真环境中,由于CPU主要工作在串行模式下且无需考虑底层硬件的特点[19],所以其很难满足小步长实时仿真的要求。FPGA虽然可以实现小步长计算,但对于大规模电力网络,由于FPGA硬件资源有限,整个网络都采用微秒级小步长仿真在一定程度上限制了仿真的规模[20]。传统的解决方法是将变流器控制系统与电气系统进行解耦计算[21],这种方法虽然在一定程度上降低了FPGA的资源占用率,但电气系统中的分布式电源和滤波器等非高频器件并不需要小步长计算,将这些器件放入CPU中计算,能够在不影响仿真精度的情况下进一步节省FPGA的硬件资源,降低硬件成本。

1.1 模型分割接口的脉冲信号问题分析

针对上述问题,在传统系统解耦方法的基础上进一步将电气系统进行模型分割。以光伏发电系统为例,在光伏电源和DC/DC变换器之间,以及逆变器与滤波器之间进行模型分割,最终运行在FPGA中的只有DC/DC变换器和逆变器,更加节省FPGA硬件资源。分割后的具体模型结构如图1所示(下文将作具体说明),高频率网络从低频率网络中采集接口信号,经小步长运算后输出三相电压uabc,需要注意的是,在下一个大步长ΔT到来之前,uabc处于一个不断更新的状态,直到下一个大步长ΔT到来时,低频率网络才从高频率网络采集当前时刻的uabc。由于uabc是一个脉冲信号,并且是以小步长Δt在实时更新,因此当低频率网络在每一个大步长ΔT开始时刻采集uabc时,会出现采集数据不准确的情况,导致仿真结果存在误差。

图1 基于CPU-FPGA的联合仿真平台示意图Fig.1 Schematic diagram of co-simulation platform based on CPU-FPGA

下文主要介绍为降低CPU与FPGA之间数据交互误差所提出的脉冲信号等效平均化方法以及改进的FPGA仿真计算流程。

1.2 脉冲信号等效平均化方法

针对上述问题,通常使用的解决方案是将uabc滤波后再进行数据采集,但该方法需要将滤波电路放入高频率网络中进行小步长计算,导致FPGA的硬件资源占用率和节点导纳矩阵阶数升高,同时增加了FPGA的实时计算压力。并且该方法对解耦处无滤波器的电力系统不具有一般性。

为此,本文提出将脉冲信号等效平均化后再发送给CPU侧的方法。设t为某一时刻,ΔT为大步长,Δt为小步长,步长倍率δ=ΔT/Δt,流程如下:

1)高频率网络接收t-ΔT到t时刻低频率网络的计算结果:直流侧电压udc(t-ΔT)和交流侧三相电流iabc(t-ΔT);

2)高频率网络根据t时刻的接口信号计算t到t+Δt区间的三相输出电压uabc(t);

3)将uabc(t)的值存入FPGA的RAM中;

4)同理,计算t+Δt到t+2Δt区间的高频率网络三相输出电压uabc(t+Δt);

5)将uabc(t+Δt)与RAM中的uabc(t)作加法计算,其结果作为新的数据更新RAM中的值;

6)重复以上循环,直至t+ΔT时刻将RAM中的值取出并除以步长倍率δ,所得结果作为接口信号发送至低频率网络端,同时RAM清零等待下一轮循环。

该方法不仅降低了导纳矩阵阶数和FPGA资源占用率,同时由于此时滤波电路运行在CPU中,控制模块不需要再从FPGA端采集滤波后的三相电压u0abc和三相电流i0abc,因此以太网TCP/IP的单包数据变得更小,打包发送时间更短,从而可以降低CPU-FPGA异步通信延时。例如,若数据精度采用single型,单包数据发送时间可减少192 ns。

在小步长侧进行脉冲等效平均化计算的时序如图2所示。

t为仿真中某一时刻,在t-Δt到t时间段内,小步长侧先进行最后一次计算,然后从RAM中读取当前时刻的数值,更新并求出其平均值以后在t时刻发送至大步长侧作为大步长侧的接口信号,并将RAM清零。同时,在t时刻,小步长侧接收大步长侧的接口信号,继续下一个ΔT内的计算。在一个ΔT内需要更新δ次RAM,每次更新均在一个小步长内完成,保证仿真的实时性。

图2 脉冲等效平均化时序图Fig.2 Pulse equivalent averaging time sequence diagram

1.3 基于FPGA的改进仿真计算流程

本节主要介绍电力系统中高频率部分在FPGA中的计算方法。FPGA运算模型中含有大量状态高频变换的开关元件,考虑到开关元件在不同开关状态下引起导纳矩阵变化带来的巨大运算负担[22 - 23],本文采用基于ADC开关模型[24 - 25]的电磁暂态实时仿真方法。该方法在开关状态改变时节点导纳矩阵不变,能够缓解因节点导纳矩阵改变给FPGA带来的计算压力。

当电路拓扑确定以后,其导纳矩阵也就确定不变,因此可以在仿真开始前将导纳矩阵及其逆矩阵提前计算出来,并在仿真初始化过程中将导纳矩阵及其逆矩阵提前存储。当仿真开始时,CPU向FPGA发送上一步长计算得到的控制信号和接口信号,同时开始运算控制模块和低频率网络模块求取当前步长的控制信号和接口信号,待下一大步长到来时发送。与此同时,FPGA开始进行计算。改进的FPGA仿真计算流程如下。

1)FPGA进行初始化,按行分块预存储导纳矩阵及其逆矩阵。

2)采集上一大步长低频率网络和控制模块计算出的接口信号和控制信号。

3)判断当前步长t时刻的电力电子开关状态。

(1)

4)根据开关状态计算各支路历史电流Ihis,计算公式与电感、电容、开关支路类型有关。

Ihis(t)=αGsub(t-Δt)+βib(t-Δt)

(2)

式中:Ihis(t)为当前步长支路历史电流;Δt为小步长;Gs为支路等效电导;ub(t-Δt)和ib(t-Δt)分别为上一步长的支路电压和支路电流;对于电阻、电感和电容等支路,α和β为固定常数[26],对于开关支路,α和β的值取决于当前步长的开关状态[27]。

5)计算并更新各节点电压和部分支路电流的值。

x=Y-1b

(3)

式中:x为待求的节点电压和部分支路电流组成的状态变量列向量;Y-1为节点导纳矩阵的逆矩阵;b为各支路历史电流源和电源电流组成的历史电流列向量。

6)将x中的脉冲信号进行脉冲等效平均化。

(4)

式中:xpul(t)为x向量中的脉冲信号;xpul,s(t)为待发送至大步长端的信号;Δt为小步长;δ为步长倍率。

7)返回1),重复执行下一循环,直至仿真结束。

其中5)中的矩阵计算采用并行计算方式,在FPGA中的实现方法如图3所示。

图3 线性方程组并行求解示意图Fig.3 Schematic diagram of parallel solution of linear equations

2 联合仿真平台及其交互方法

2.1 联合仿真平台的实现

本文以光伏发电系统的暂态实时仿真为例介绍该联合实时仿真平台。对于光伏发电系统,逆变器、DC/DC变换器等开关频率高,逻辑简单且并行度高的拓扑电路需要FPGA小步长高速运算,而逆变器控制电路等规模较大、逻辑复杂,且对计算速率要求不高,可以利用CPU进行大步长仿真计算。通过以太网完成CPU-FPGA混合步长之间的数据交互,实现基于CPU-FPGA的混合步长实时仿真平台。

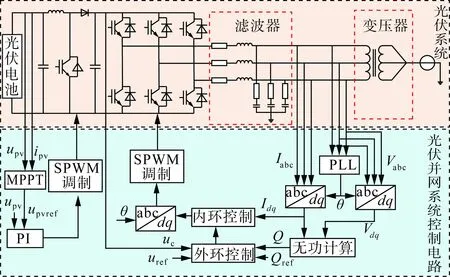

图1中控制模块采集分布式发电系统中光伏电池输出电压upv和电流ipv作为控制输入,经PI调节后输出DC/DC电路所需调制波。控制模块同时采集低频率网络中大电网系统滤波后的三相电压u0abc和三相电流i0abc作为控制输入,经dq坐标系解耦、无功功率计算和内外环控制,输出逆变器所需的PWM调制波,这一系列任务是在CPU中进行的。需要注意的是,PWM信号的生成需要在高频率网络中完成,这样才能保证仿真结果的准确性。

在本平台中,基于CPU的上位机采用本文研发的通用实时仿真器(universal real-time experimental platform, UREP),该仿真器完美兼容Simulink软件,拥有很好的灵活性和可扩展性。FPGA型号为XILINX的Kintex- 7系列,芯片型号为XC7K325T。基于UREP平台、FPGA板卡和相关外设硬件,搭建适用于分布式发电系统的联合仿真平台,平台结构如图1所示。

UREP中的CPU运行控制模块和低频率网络部分,同时还需兼顾与上位机和FPGA间的数据交互,仿真步长设为ΔT;FPGA运行高频率网络部分,仿真步长设为Δt,Δt需要满足电力电子开关高频特性和仿真实时性要求。FPGA与CPU之间通过以太网(TCP/IP)进行数据交互,上位机人机交互界面与UREP仿真器之间通过以太网进行控制指令交互,在上位机界面可以实时观测仿真结果,也可通过FPGA的其他数据接口输出仿真数据用以观察。

2.2 仿真平台接口交互方法

控制系统和低频率网络在与高频率网络分割后以混合步长进行仿真,二者之间采用多速率交互方法,交互时序如图4所示。

图4 混合步长仿真时序示意图Fig.4 Simulation sequence diagram of mixed step length

在图4中,t为仿真中某一时刻,CPU大步长仿真侧在t-ΔT到t时间段内计算得到小步长仿真侧所需的控制信号和接口信号,并在t时刻发送至FPGA小步长仿真侧;与此同时,小步长侧在t-Δt到t时间段内计算得到大步长侧所需的接口信号,并在t时刻发送至大步长侧,从而实现大步长与小步长的并行计算。小步长侧在一个ΔT内计算δ次,均使用t-ΔT时刻的端口信号作为计算输入,大步长侧在一个ΔT内使用t-ΔT时刻的端口信号进行一次计算。规定数据在一个ΔT内进行一次交互,且在每一个ΔT开始时刻进行交互。

3 算例分析

3.1 仿真算例验证

基于上述方法,本文搭建了典型光伏发电系统如图5所示。

图5 光伏系统拓扑结构示意图Fig.5 Schematic diagram of photovoltaic system topology

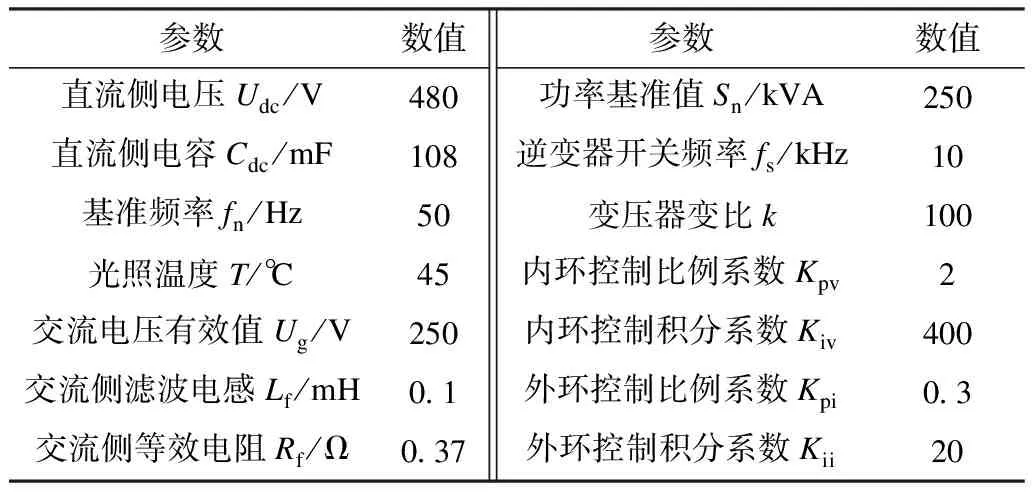

CPU端仿真步长ΔT设为50 μs,FPGA端仿真步长Δt设为1 μs,仿真算例具体参数如表1 所示。算例中的光伏电池采用由光生电流源、二极管、串联电阻和分流电阻组成的单二极管等效电路模拟,DC/DC变换器采用最大功率点跟踪(maximum power point tracking, MPPT)策略进行控制,DC/AC逆变器采用恒直流电压恒无功功率策略进行控制,无功参考值Qref设为0。

表1 仿真算例参数设置Tab.1 Parameter settings of simulation example

为了验证本文仿真方法的有效性,在Simulink中搭建了电路拓扑和控制参数完全相同的算例模型,仿真步长设为1 μs。其离线仿真结果作为本文所提联合仿真平台仿真结果的参照,并在以下3个场景中进行对比。

场景A:光照强度在t=0.4 s时由1 000 W/m2下降为500 W/m2,在t=0.6 s时由500 W/m2上升为1 000 W/m2,仿真结果如图6所示。

场景B:在系统稳定运行情况下,在t=0.7 s时交流侧A相发生单相接地短路故障,0.1 s后故障消除,仿真结果如图7所示。

场景C:系统运行在某地24 h内的实际光照下,在t=12 s时交流侧A相发生单相接地短路故障,0.05 s后故障消除,仿真结果如图8所示。

图6—8分别反映了系统在光照强度突变、发生单相接地短路故障和实际光照波动时发生短路故障的情况下,本文所提的实时仿真方法与Simulink离线仿真结果的对比。图中Ia、Udc和Pdc分别为交流侧变压器一次侧电流,光伏电池输出直流电压和光伏阵列提取最大功率值。观察图6可知,当系统中光照强度突变后,变压器一次侧电流减小,光伏电池输出直流电压有微小波动,光伏阵列提取的最大功率由240 V跌落至119.7 V后保持平稳;图7中,当系统发生单相接地短路时变压器一次侧电流发生突变,持续0.1 s后恢复正常运行状态,光伏电池输出直流电压发生振荡,光伏阵列提取的最大功率有短暂的小幅下降;图8中,将24 h实际光照强度以每小时为单位分为24个时段,在仿真中每秒更新一次光照强度,总仿真时间为24 s,Ia随光照强度升高而变大,在短路故障时其幅值由4.7 V突变至181.6 V,故障消除后能快速恢复稳态运行。结果证明,实时仿真和Simulink离线仿真结果基本一致,并且在暂态过程中能较好地跟随离线仿真曲线的变化,验证了所提实时仿真方法的有效性和准确性。

图6 场景A的仿真波形对比Fig.6 Comparison of simulation waveforms in scenario A

图7 场景B的仿真波形对比Fig.7 Comparison of simulation waveforms in scenario B

图8 场景C的仿真波形对比Fig.8 Comparison of simulation waveforms in scenario C

图9为场景C中交流侧变压器一次侧电流相对误差曲线,从误差曲线可以看出,系统在暂态仿真时存在一定误差,但总体误差范围在0.4%以内,具有较高的仿真精度。其误差主要来源于2个方面:1)Simulink离线仿真模型中IGBT采用了理想开关建模,而FPGA中的开关器件采用了ADC伴随离散电路方法进行建模;2)联合仿真平台对光伏发电系统进行了模型分割和混合步长并行计算,而Simulink离线仿真模型是整个系统在同一仿真步长下进行计算的。

图9 场景C一次侧电流相对误差曲线Fig.9 Relative error curve of primary side current in scenario C

3.2 硬件资源消耗对比

仿真算例中基本无源元件电阻、电感和电容与电力电子开关的增加会导致导纳矩阵阶数升高和计算并行度增加,高并行度的计算将会占用更多的硬件资源,同时导纳矩阵阶数升高势必会带来更多的乘法运算,乘法器将占用大量硬件资源。

表2为脉冲信号等效平均化前后FPGA硬件资源占用情况对比。

表2 FPGA硬件资源消耗对比Tab.2 Comparison of FPGA hardware resource consumption

在优化之前,导纳矩阵为16阶,高阶的矩阵直接导致硬件资源占用增加,同时也给FPGA的实时计算带来压力。通过脉冲信号等效平均化,仿真算例中的滤波器由原来在FPGA中仿真改为在CPU中仿真,导纳矩阵的阶数从16阶降至10阶,有效地降低了FPGA硬件资源占用率,仿真计算时间减少,更有利于实现实时仿真。

从表2中可以看出,与优化前的仿真方法相比,本文所提等效方法在保证仿真精度的前提下,降低了FPGA硬件资源占用率,验证了该方法的有效性。

4 结论

本文基于CPU-FPGA联合仿真平台设计了一种混合步长电磁暂态实时仿真方法,提出了一种脉冲信号等效平均化方法对数据传输中的误差进行补偿,该方法同时降低了FPGA硬件资源占用率。

搭建光伏发电系统仿真模型进行暂态过程仿真,将FPGA高频部分和CPU低频部分仿真步长分别设为1 μs和50 μs。仿真结果表明,在光照强度突变和电路发生短路故障情况下,混合步长实时仿真结果与Simulink离线仿真结果基本一致,验证了本文所提实时仿真方法的有效性。

对脉冲信号等效平均化前后的模型进行建模并分析了硬件资源消耗,结果证明优化后的模型减少了FPGA的硬件资源消耗。