基于SPI 的信号完整性案例分析

2022-12-01李菁刘培文

李菁,刘 澎,刘培文

(北京航天发射技术研究所,北京 100071)

信号完整性问题一般出现在高频领域,高频信号的时钟频率高,信号上升沿和下降沿陡峭,当信号上升时间和下降时间达到了1 ns 以下时,信号容易发生抖动、延迟、地电位弹跳、反射、串扰、脉冲展宽、时序混乱等信号完整性问题。这里论述的信号完整性案例发生在工作频率仅为1 MHz 的串行外设接口(Serial Peripheral Interface,SPI)信号上,SPI 信号未考虑信号完整性设计,导致SPI 时序混乱,无法稳定传输数据。通过该低频案例的分析,得出信号完整性问题在低频通信领域也应该引起重视,并总结得出一些低频领域的信号完整性设计要点。

1 信号完整性案例

1.1 问题概述

某型号显控器进入批产调试阶段,首次批产300台产品,有19 台产品在初测时发现产品上电显示字符残缺拖影(正常单机应循环显示laolian running),如图1 所示,其他产品显示正常。

图1 故障产品显示情况

1.2 问题分析

显控器由主板和显示模块组成,主板与显示模块之间使用SPI 通信,通信频率为1 MHz。

显示模块有单独的测试工装,将显示模块放在单独的测试工装上,显示模块显示正常。主板主要实现了英飞凌单片机的最小系统,测试单片机的电源、晶振、复位等信号时,均无异常点。示波器测试SPI 信号,未发现异常情况,SPI 时序如图2 所示。

图2 SPI时序

使用示波器在测试SPI 信号中发现,示波器表笔接触SPI 任何一根信号时,显控器由残缺拖影显示变为正常显示。

测试主板输出的SPI 时钟波形的上升沿时间,如图3 所示,上升沿时间为4 ns,且有明显的反射干扰。

图3 显控器主板输出的波形上升沿时间

测试显示模块的测试工装输出的波形上升沿时间,如图4 所示,测试工装使用ARM 系列单片机作为主处理器输出SPI 信号,在同一个示波器测试下输出时间为7 ns 左右,波形反射现象不明显。

图4 测试工装输出的波形上升沿时间

对比图3 和图4 的测试情况得出,显控器显示字符残缺拖影的原因在于主板输出的波形上升沿时间太短,影响了SPI 信号的完整性。

1.3 问题定位

显控器主板输出波形上升沿时间太短,示波器测试为4 ns 左右(实际更短),SPI 信号反射严重,显示模块的噪声容限较小,信号无法保持较好的完整性,造成显控器显示字符出现残缺拖影现象。

1.4 问题解决

显控器主板使用的是英飞凌公司的单片机XC2287 系列,该单片机可通过修改POCON 寄存器更改IO 上升沿。修改寄存器方法如图5 所示。

图5 寄存器修改方法

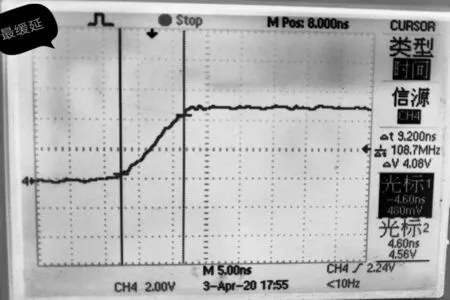

通过程序将输出波形的上升沿改为最缓输出方式,修改命令为P3_POCON=0x0020,修改后示波器测试波形如图6 所示,从图6 可知,波形平滑无反射干扰异常现象。将更改完成的程序加载至显控器中,此时显控器显示正常;将输出波形的上升沿再改回最快输出方式,加载到显控器中,此时显控器仍然显示字符残缺拖影,故障复现。

图6 主板更改成最缓上升沿

将所有批次的显控器产品波形的上升沿都更改为最缓输出方式,此时300 台显控器均工作正常,未再出现类似问题。

2 案例分析

信号完整性问题是一个复杂的问题,常见的噪声、电磁干扰等问题的根源都是信号完整性问题。案例中仅由信号波形测试并不能定位到信号上升沿问题上,因为数字信号波形不可能完全平整,尖峰和毛刺是工程中常见的现象,许多运行稳定的通信信号都有不可避免的尖峰和毛刺,进而形成反射干扰,原因在于使用的显控模块,显控模块为一个两层的PCB 板,没有单独的GND 层,所有高频信号的走线都在TOP 层和BOTTOM 层,GND 信号和POWER 信号也只是用导线连接在一起,这样的PCB 板噪声容限很小,极易发生电磁干扰问题。

所以案例中的信号完整性问题是由两方面造成的:一是显控器主板输出的波形上升时间短,干扰了显示模块的正常工作;二是显示模块的噪声容限小,极易受干扰。

3 信号的反射干扰原理

电路板上的线条常常要通过过孔区域、元件密级区域与跨板连接,传输线线宽在这过程中会发生变化,由此造成传输线上的阻抗特性突变,进而引起信号来回振荡,从而形成了发射噪声。

决定传输线影响的三个特性是突变引起的时延(TD)、突变处的特性阻抗(Z)以及信号的上升时间(RT)。

反射系数与阻抗变化的关系如式(1)所示:

假设线条的颈状造成阻抗从50 Ω变化到75 Ω,则根据式(1)可计算出反射系数为0.2。

如果阻抗突变的长度很短,则来自两端的反射可以相互抵消,因为Z1、Z2值互换后,反射系数正负相抵,此时不会对信号完整性产生影响。

如果时延TD 大于上升时间,则阻抗突变较长,如果突变处的时延TD 小于信号生产时间的20%,则不会造成影响,可得出所允许的阻抗突变处的最大长度为:

其中,lenmax的单位为in(英尺)。RT 表示信号上升时间,单位为ns。

如果信号上升时间为4 ns,则长度不小于4 in 的颈状不会产生信号完整性问题。反之,在PCB 布局布线已经固定的情况下,信号长度、宽度已经固定,改变信号的上升时间是解决信号完整性问题的唯一途径。

在工程应用中,传输线不可能做到从源端到接收端的线宽一致,也无法控制突变引起的时延,所以解决信号完整性问题还是要降低传输信号的上升时间,增加阻抗匹配。

案例中信号完整性问题的解决方法是直接增加传输信号的上升时间,减小信号的反射干扰,从而改善SPI信号的质量,保证后续电路的正常工作。

4 信号完整性在低频领域的设计要点

通过案例分析,结合信号反射干扰原理,得出在低频电路中,信号完整性需要关注的设计要点:

1)信号传输线上应增加阻抗匹配设计,如串联电阻或者并联电容,两种做法的根本都是改变了信号的上升时间;

2)SPI 用作板间传输时,传输线变长,过孔变多,所以更需要考虑信号完整性问题;

3)印制板布局布线时,需增大地平面、电源平面的铺设,增大噪声设计容限;

4)在工程中,信号完整性问题不容易被测量到,因为测量设备的接入本身就会改变电路的分布参数,仅从测试结果无法判断异常情况;

5)对于涉足信号完整性问题的工程师而言,SPICE 仿真器或行为仿真器是不可缺少的,价格低廉的仿真器都可以对由于阻抗突变而产生的多次反射进行仿真,仿真结果可以指导工程设计,并及时进行优化。

5 结论

文中分享了一种低频领域内的信号完整性案例,通过对案例的问题现象、问题分析及问题定位,找出影响信号完整性的因素,即信号的上升时间。改变信号的上升时间,上升时间变长时,显控器显示正常;上升时间变短时,显控器显示字符残缺拖影。该案例直观地反映出了信号的上升时间长短给产品带来的影响。

信号完整性问题是一门高深的基础理论课程,该问题带来的后果也较为复杂,振铃、反射、近端串扰、衰减、地弹、电源反弹等噪声问题和电磁干扰问题都属于信号完整性问题的范畴,有些信号完整性问题不会给产品或系统带来直接后果,有些则会给产品或系统带来灾难性问题,不同的信号完整性问题需要不同的处理手段,文中以案例为基础,在工程领域内从产品设计角度提出一系列信号完整性的设计要点,在低频领域内也需要考虑信号完整性问题。