多发连续冲击波超压智能存储测试系统

2022-11-28王毛凯王文廉王玉

王毛凯,王文廉,王玉

(中北大学 仪器科学与动态测试教育部重点试验室,山西 太原 030051)

0 引言

作战试验是指在可控、可测的虚拟作战环境中运用作战模拟原理研究作战问题的一种军事实践活动,连发作战试验是一种特殊的作战试验[1],需要在试验过程长且环境复杂的背景下,从多个角度精确地记录下每次爆炸所产生的冲击波信号[2],并对其进行处理。然而常规的存储测试系统通常是针对一次爆炸进行冲击波信号记录[3-4],需要频繁地对测试系统进行指令操控以及数据读取,才能实现有效信号的多次记录,效率较低;不仅如此,常规的存储测试系统并没有基线调节功能,测试环境以及传感器灵敏度会影响测试系统基线,不仅导致测试系统误触发或者不触发,而且不利于对信号的处理分析[5]。

针对连发作战试验的需求,本文设计了一种基于SRAM 和Flash 的多发连续冲击波智能存储测试系统[6-8]。该系统具备自动调节基线功能,保证了系统的灵活性与适用性,能够适用各种复杂环境;利用FPGA 模块化、多线程的工作模式[9-10],对存储进行分区管理[11],利用负延时技术结合信号触发识别技术实现多发连续冲击波的多通道智能存储[12]。

1 系统总体设计

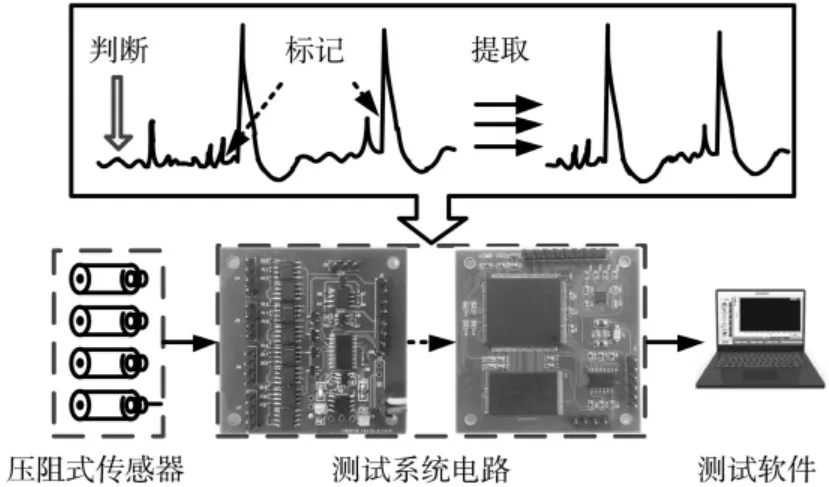

测试系统在存储测试原理的基础上针对冲击波信号上升沿陡峭、持续时间短的特点,对信号进行触发识别,将缓存数据与阈值进行多次比较,判断是否为有效数据,从而进行缓存地址标记和有效数据提取,实现多发连续冲击波的智能存储。系统原理结构图如图1 所示,主要由压阻式压力传感器、测试系统电路以及测试软件组成。

图1 存储测试系统原理图

为了将冲击波信号调理在合适的范围,测试系统会在基线调节之后再进入采集状态。模拟信号经过调理后转化为数字信号按顺序进入缓存器,同时系统会对其进行跟踪检测,将数据与设定阈值进行比较,以初次大于阈值的信号为起点,若在设定的时间内检测到多次、多个连续超出阈值的脉宽突变信号或者超出阈值脉宽突变较大的信号,将其视为有效信号,并对其缓存地址进行标记。缓存结束后,按照标记地址,将有效信号提取到存储器,进而实现连续冲击波的智能存储。

1.1 信号调理电路

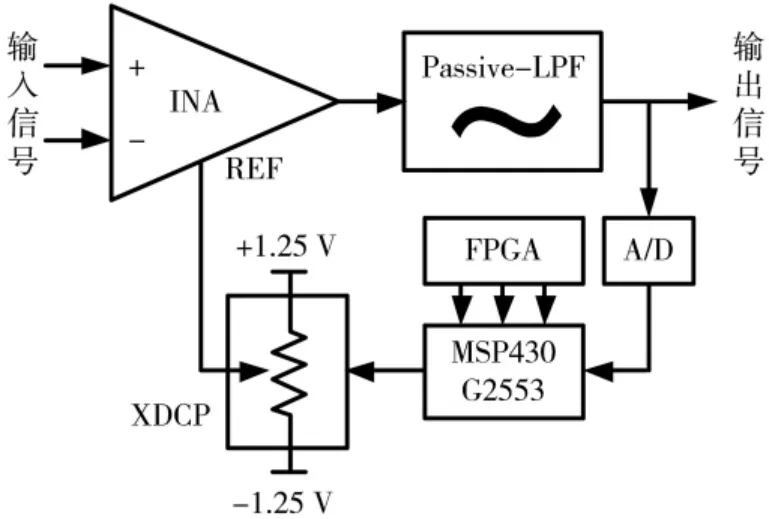

信号调理电路主要负责对传感器的输出信号进行调理,将各通道的基线调整至同一水平线,使有效信号调整至合理的范围,主要由仪表放大器、低通滤波器以及数字电位器组成,组成框图如图2 所示。

图2 信号调理电路框图

信号调理电路选用仪表放大器对传感器输出的差分信号进行放大,利用数字电位器对滤波降噪后的信号进行补偿,不仅抑制传感器的时漂和温漂,而且实现基线调节,使有效信号调理在0~2.5 V 范围内,输出至采集存储电路。

1.2 采集存储电路

采集存储电路主要负责对调理后的模拟信号进行检测、标记、提取,是实现多次连续冲击波存储的关键;主要由时钟晶振、A/D 变换器、FPGA、存储芯片和Wi-Fi模块等部分组成,组成框图如图3 所示。

图3 采集存储电路框图

采集存储电路选用20 MHz 的有源晶振作为系统时钟;选用采样频率为4 MS/s,转换精度为12 bit 的逐次逼近型四通道A/D 变换器进行模数转换;采用Xilinx Spartan-6 系列FPGA 芯片作为主控芯片,利用其模块化多线程的工作模式,完成信号的转换、负延时控制、触发判断以及存储器读写等各项功能。

2 功能设计与实现

2.1 基线自动补偿

为了统一各通道的基线,提高测试系统的适用性,测试系统选择非易失性数字电位器X9C130(调节范围为-1.25 V~1.25 V,精度为0.025 V)对滤波降噪后的信号进行补偿,进而实现基线的调节,具体流程如如图4所示。

图4 自动调节流程图

微控制单元(Microcontroller Unit,MCU)接收到调节基线的指令后,启动四路A/D 对传感器的输出进行采样,将每一路A/D 输出均值分别与预设基线进行比较,进而确定每一路所需补偿电压的大小以及方向,再发送对应数量的脉冲给数字电位器,进而实现基线的调节。

MCU 会对调节后的基线重新采样,若与预设值之间的差值小于0.025 V,则认为调节成功,进行相应的反馈;若调节失败,并且仍处于定时中,则进行重新调节,反之则进行反馈,并回到监听初态。

2.2 多通道多次自动存储

为了保证采集存储测试系统能够从多个角度精确地记录下连发试验过程中的每次冲击波信号,测试系统以FPGA 为核心控制器,对存储进行分区管理,利用负延时技术结合信号触发识别技术,对有效信号进行标记、提取实现有效信号的多通道多次自动存储。

2.2.1 数据多通道缓存

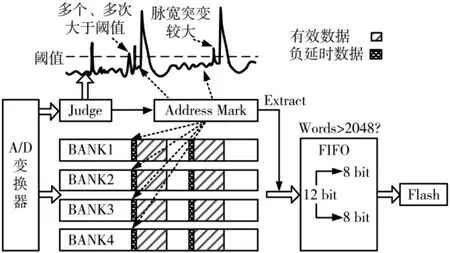

数据多通道缓存的本质是对信号进行触发识别的同时对存储器地址进行划分与控制,其原理如图5 所示。

图5 多通道存储控制示意图

测试系统选择使用CYPRESS 的MT7C 系列的SRAM芯片作为单次信号缓存单元,按照地址将其划分为4 个BANK。调理后的信号经过A/D 变换器转化后在FPGA的控制下依次进入预先划分好的区域,并在指定区域内循环往复。

数据缓存的过程中,控制器会对信号进行触发识别,将信号与触发阈值进行比较,以初次大于阈值的信号为起点,记录下设定时间内信号大于阈值的次数以及大于阈值的点数。若出现一定数量、多次大于阈值的连续脉宽突变信号或者超出阈值脉宽突变较大的信号将其视为有效信号,并开始进行正向数据记录以及缓存地址标记,若并未出现有效信号,则根据比较结果重新确定起点。当有效数据写满预设存储长度后,系统自动将负延时数据以及有效数据依次移至Flash 存储单元,然后再次进入信号采集状态检测下次有效信号,直至试验结束。

2.2.2 数据快速提取

测试系统选择使用Micorn 的MT29 系列的NAND Flash芯片作为存储单元,利用FPGA 模块化、并行的工作特点,采用分时加载技术实现有效信号的快速提取。

由于该款芯片采用ONFI 协议标准,测试系统采用底层操作和顶层控制的方式对其进行操控。操作模块在控制模块的控制下执行复位、模式设置、读、写、块擦除等命令。

按照ONFI 协议规范,Flash 在执行页编程指令时,可分为命令、地址加载阶段、数据加载阶段以及自动编程阶段。其中自动编程阶段是由芯片内部自动控制,将相应寄存器内部的数据载入到存储单元的过程,通过查阅芯片手册,自动编程阶段所占用的时间(tBusy)大约为220 μs,远大于命令、地址(tAddr)和数据加载的时间(tData)。自动编程阶段是限制Flash 读、写速度的主要原因,由于此款芯片含有2 个LUN(Logical Unit),可视为两片芯片的列扩展,为了进一步提升Flash 页编程速度,系统从采用分时加载技术,设计一个二级流水线,并使用Modelsim软件进行仿真验证,其原理仿真图如图6 所示。

图6 二级流水线原理仿真图

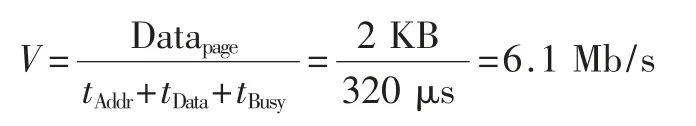

此款芯片的单页数据量为2 KB,整个读写过程所消耗的时间大约为320 μs,采用传统的单平面页读、写方式,在系统时钟20 MHz 的条件下,则Flash 的读、写速度最大为:

式中:V 为Flash 的页编程速度,单位为Mb/s;Datapage为Flash 的写单页数据容量,单位为MB;tAddr、tData、tBusy分别为Flash 的写地址、数据、编程的时间,单位为s。

采用二级流水线方式进行数据存储,则Flash 的最大读、写速度可提升至12.2 Mb/s。

Flash 上电之后,在FPGA 的控制下依次执行复位与模式设置指令,然后进入空闲态,每当有效信号缓存结束,上层控制模块都会发出相应的指令,Flash 都会按照ONFI 协议规范作出相应的操作,将有效信号提取到Flash 当中,实现有效信号的快速存储。

3 实验及数据分析

基线自动调节功能通过自主研发的硬件平台进行测试。采用LabVIEW 软件编写测试软件,将传感器接到信号调理电路。系统稳定之后,使用测试软件进行基线调节,调节成功之后进行基线读取。搭载好的测试环境如图7 所示。

图7 自主测试平台

使用测试软件对测试系统进行不同基线的设置,都获得有效数据,取4 次实验数据如表1 所示。

测试系统使用的数字电位器的最小调整值为0.025 V。由表1 可知,各个通道基线与设置基线之间的差值最大为0.012 V,小于数字电位器的最小调整值,基线调节功能达到预期目标。

表1 基线测试结果

为了对测试系统的整体功能进行验证,模拟连发作战试验。根据当量、到爆心距离以及传感器的灵敏度,对测试系统进行参数配置,将放大倍数设置为1.5倍,将基线设置为800 mV,触发阈值设置为1 000 mV,产生4发、16发、24发、32发连续冲击波。存储结束后,利用测试软件进行数据读取,数据如图8 所示。

从图8 中可知测试系统完整地记录下每发冲击波波形,每次采集到的冲击波次数与实际冲击波次数一致,证明了测试系统实现了多发连续爆炸冲击波智能存储。

图8 多发冲击波超压曲线

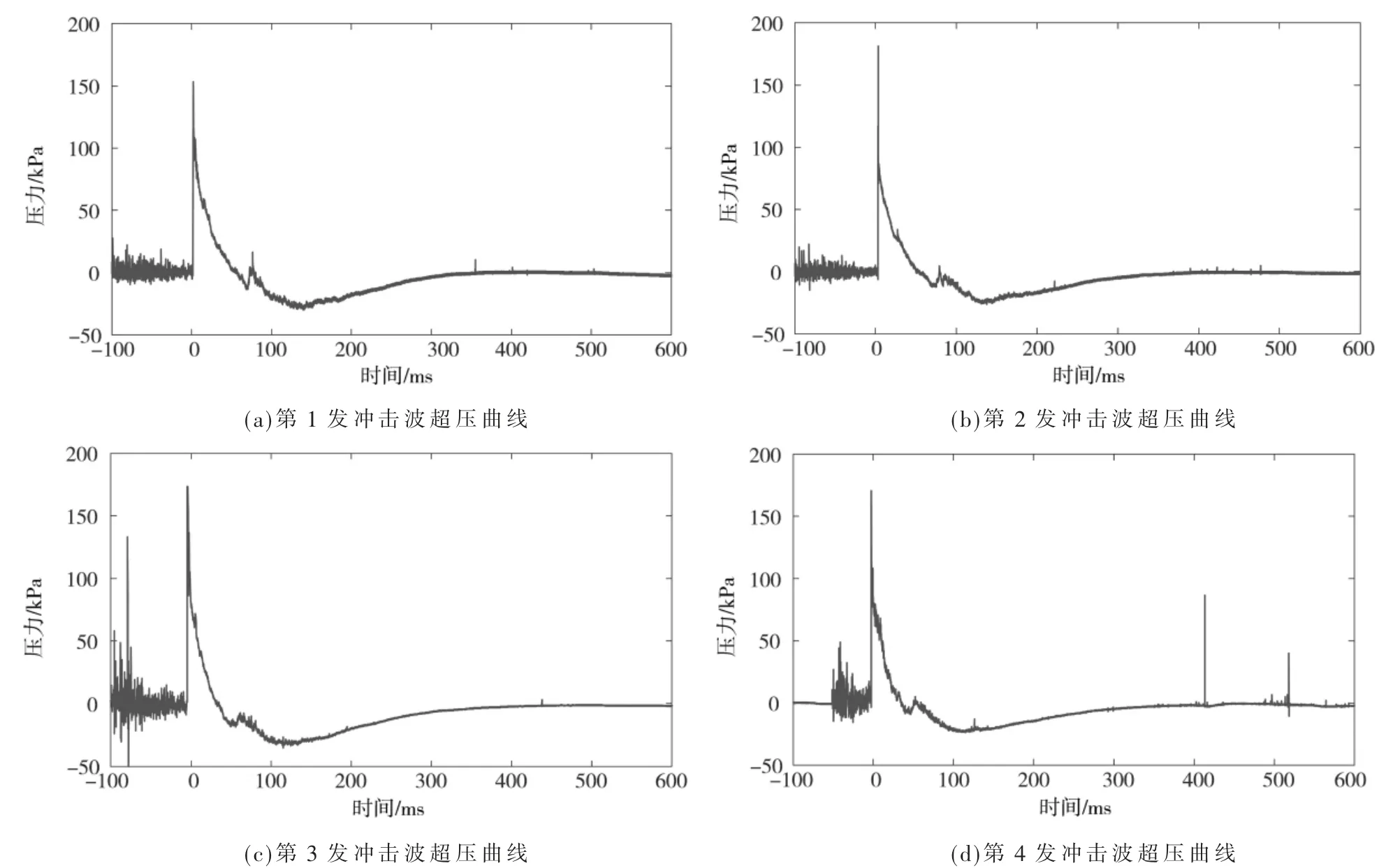

利用测试软件对4 发冲击波数据进行处理,4 发冲击波超压曲线如图9 所示,每发冲击波曲线的统计参数如表2 所示,处理结果为理论分析提供了数据基础。

图9 测试压力曲线

表2 冲击波统计数据

4 结论

针对连发作战试验环境的需求,设计并研制出基于SRAM 和Flash 的多发连续冲击波智能存储测试系统。测试系统具备自动调节基线功能,误差小于0.025 V,提高了系统的适用性,利用采集存储技术结合信号触发识别,实现了32 次连续冲击波的4 通道快速存储,并计算出超压、持续时间、冲量等特征值,弥补了多发连续冲击波测试方面的不足。