一种基于VBS脚本语言的Ku频段时延线设计方法

2022-11-16宋庆辉

宋庆辉

(中国电子科技集团公司第五十四研究所 河北省石家庄市 050081)

时延线是一种重要的微波无源器件,可以在电路中提供真实的物理时延[1‐6],使用场景广泛,可用于宽带收发组件、相控阵雷达、信道模拟器等多种重要的微波设备或系统。时延线有多种实现形式,包括同轴线、微波平面传输线、人工传输线、芯片、光纤、声表面波器件等。其中,光时延线[5‐6]的工作原理是将电磁信号通过光电转换器变换为光信号,然后经过低损耗光纤的构成的物理时延结构后,再转变为电信号,由于光电、电光损耗通常较大,而光纤损耗又非常小,因此这类时延线通常用于时延量较大的场景,实现ns 或us量级的时延。声表面波时延线则是利用谐振器将电磁信号转换为机械能,经过处理后再将机械能转换回电磁信号,声表时延线通常也用于大时延量场景。芯片时延线通过集成电路工艺在半导体材料上加工人工传输线或慢波结构实现基本的时延单元,当用量很大时具有非常低廉的成本,且易于与微波开关、放大器等电路单元集成,形成功能更为完整的器件,然而对于用量较少的场景,芯片时延器的研制成本无法摊薄,其经济性会变得很差。当需用数量较小,且时延量也较小时,同轴时延线具有相对低廉的成本和优异的射频性能,但其调试的成本较高,且难以实现小型化。人工传输线(集总电容电感构成的梯形网络)具有低廉的成本、紧凑的结构以及易于调试的特性,但因其寄生参数较高,无法在高频场景使用。微波传输线型时延线具有低廉的成本和较高的集成度,且便于调试,但传统微带线有较为明显的色散特性,高低频段的特性参数相差较大,因此宽带时延性能也较差。

微波多层印制技术[7‐10]是在传统印制电路工艺基础上发展处的一种重要的微波电路集成工艺。基于微波多层印制技术的内埋传输线,具有较低的色散水平,有利于实现超宽带时延线的设计。同时,内埋传输线具有自屏蔽特性,通过在相邻传输线间增加接地通孔,可在较短线间距的情况下保持较低水平的线间耦合,从而得到较高的布线密度。由于内埋传输线的调试成本相对较高,在设计阶段若能得到更精确的设计值,对时延线的工程化非常有利。VBS 是以一种基于Visual Basic 的脚本语言,具有丰富的系统接口函数,同时也与Word、Excel、ANSYS EM、Altium Designer 等应用程序有良好的互通性,适于完成批量重复性工作。本文利用VBS 脚本技术,实现基于微波多层印制技术的内埋时延线的自动建模和仿真分析,为宽频带时延线设计提供了新思路。

1 时延线组成单元

1.1 内埋传输线

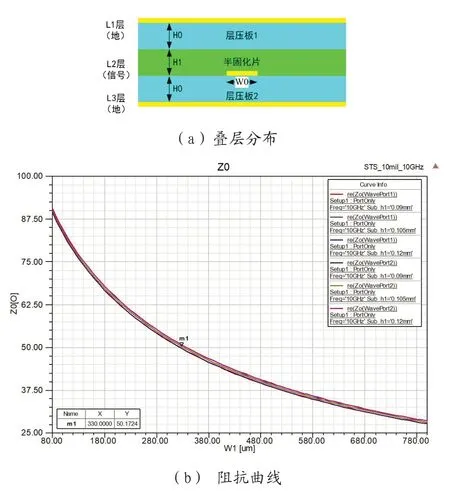

本文拟使用的内埋传输线采用下图1(a)中的叠层分布。该叠层采用两块层压板和一块半固化片压合而成。在本文中,层压板选用10 mil 厚的RELONG RS300 板材,半固化片选用4.4 mil 的RELONG RLP30 半固化片。层压板1 的上表面L1 和层压板2 的下表面L3 均为地平面,层压板1 的下表面空置,层压板2 的上表面设为信号层。图1(a)中,两块层压板的厚度均为H0,半固化片的厚度为H1,内埋传输线的宽度为W0。按照以上叠层分布和板材信息进行三维电磁场建模,并以W0 为主参数,H1 为第二参数进行扫描,特性阻抗曲线的仿真结果分别如图1(b)所示。可以看出,对于所讨论模型,半固化片的厚度在±15um的范围内波动时,对传输线特性影响不大,对特性阻抗的影响不大于3%,对有效介电常数的影响不大于1‰。对应于50Ω 阻抗内埋传输线的线宽约为0.33mm,其相应有效介电常数约为2.96。

图1:内埋传输线叠层及仿真结果

1.2 内埋弯角结构

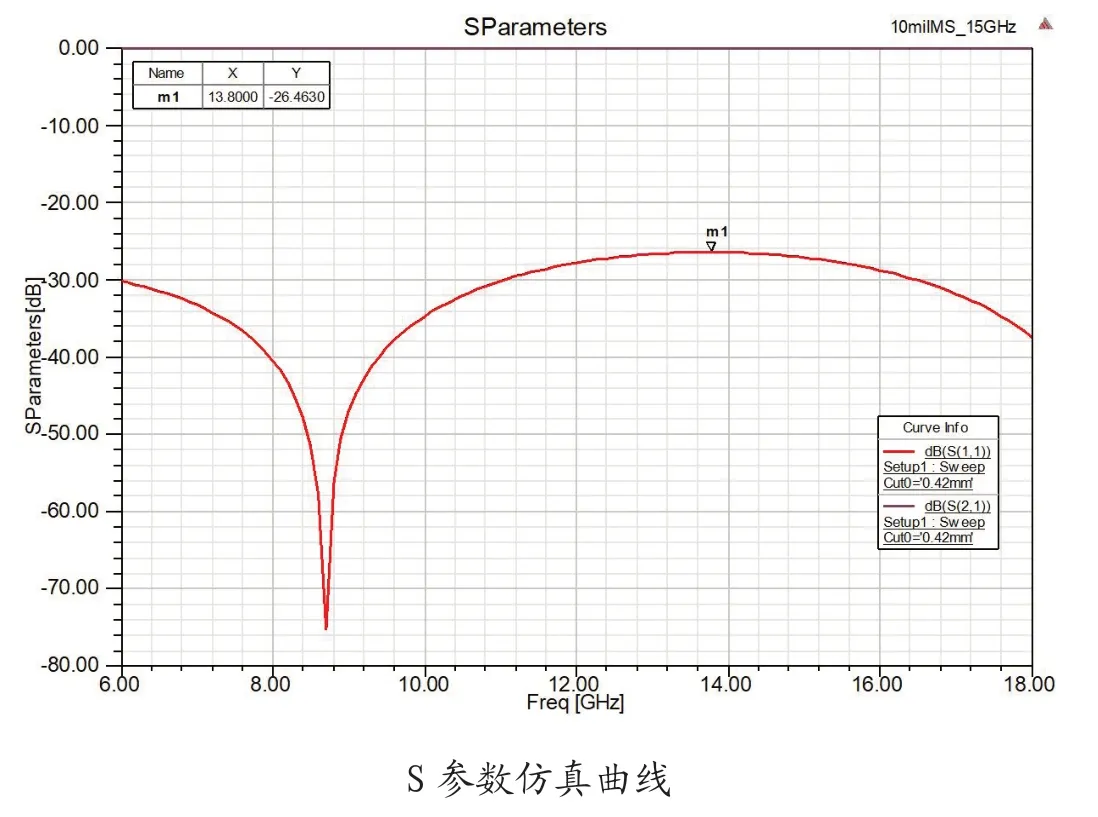

实现内埋时延线的基本单元是内埋传输短截线和内埋弯角结构。在Ku 频段,弯角传输线带来的寄生参数对射频指标影响较大,当多个弯角结构级联后,这一影响会进一步加大。大延时量的时延线往往采用蜿蜒线结构,其中可能包含数十个甚至更多弯角结构,因此需针对这一结构进行特别的优化,以得到较为优良的宽带射频性能。最常见的弯角结构是90°斜切弯角结构,斜切的部分可有效降低弯角处的寄生电容。针对0.33mm 宽的线条,使用三维全波仿真软件ANSYS EM 进行参数扫描,得到W1 为0.42mm 时整个通带内回波损耗最优,仿真结果如图2 所示。

图2:弯角结构模型及仿真结果

1.3 微波过孔结构

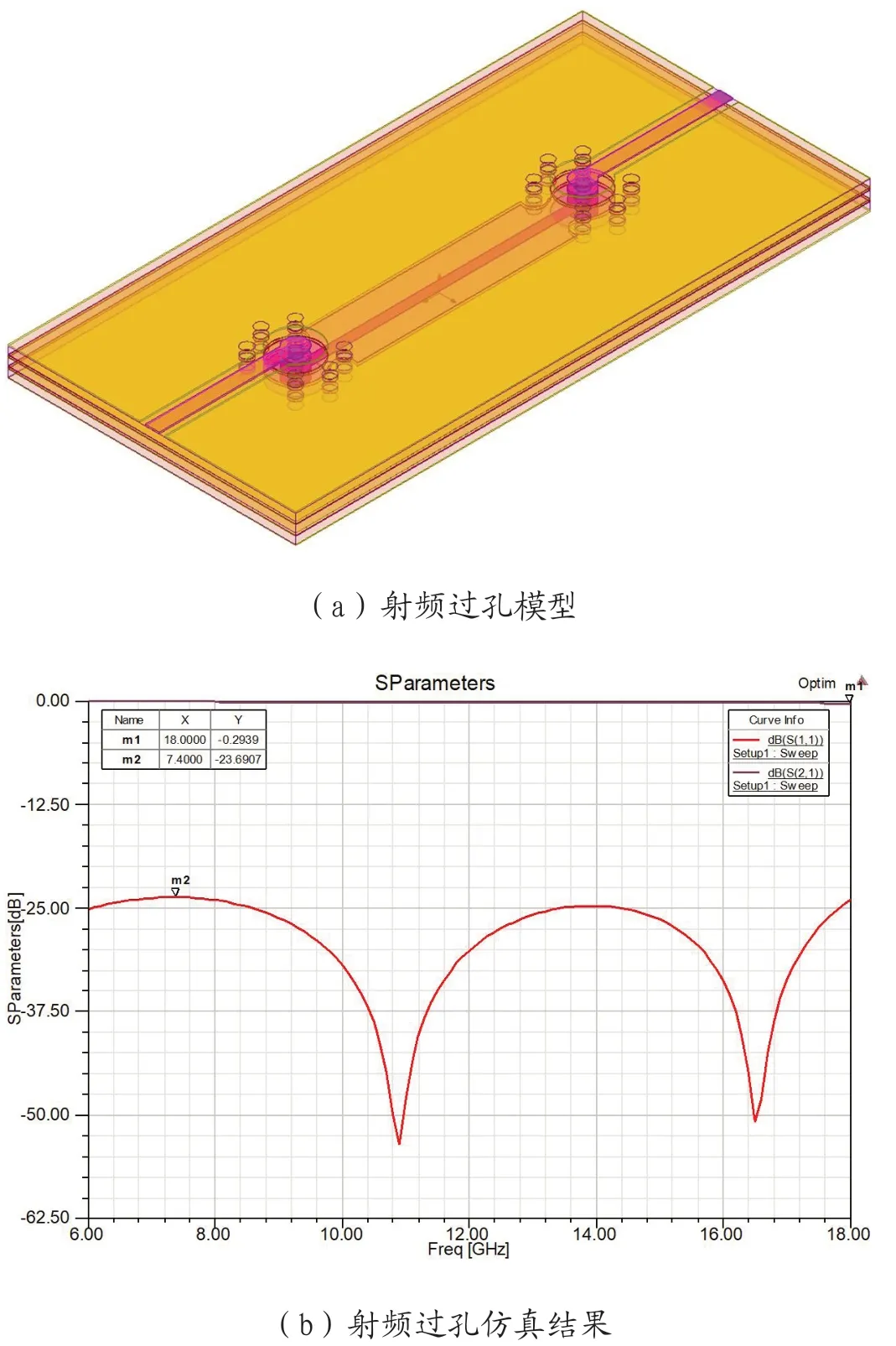

如前所述,内埋传输线具有较好的射频特性,包括低色散、自屏蔽等,但这一形式的传输线仍需使用微波过孔等引出结构连接至表层传输线,以与其他电路元器件相集成,或引出射频测试点。基于6 层印制板的微波多层过孔背靠背模型如图3(a)所示,该结构的内埋传输线位于印制板的第3‐6 层,1‐2 层使用金属背敷共面波导(Coplanar Waveguide with Ground Backed,CPWG)。相比于微带线,CPWG 同样具有低色散的特性,因此在测试或与其他元器件集成时,CPWG 这一引出形式对宽带性能指标影响更小。该结构的三维仿真结果如图3(b)所示。

图3:射频过孔背靠背模型及仿真结果

2 基于VBS脚本的时延线设计方法

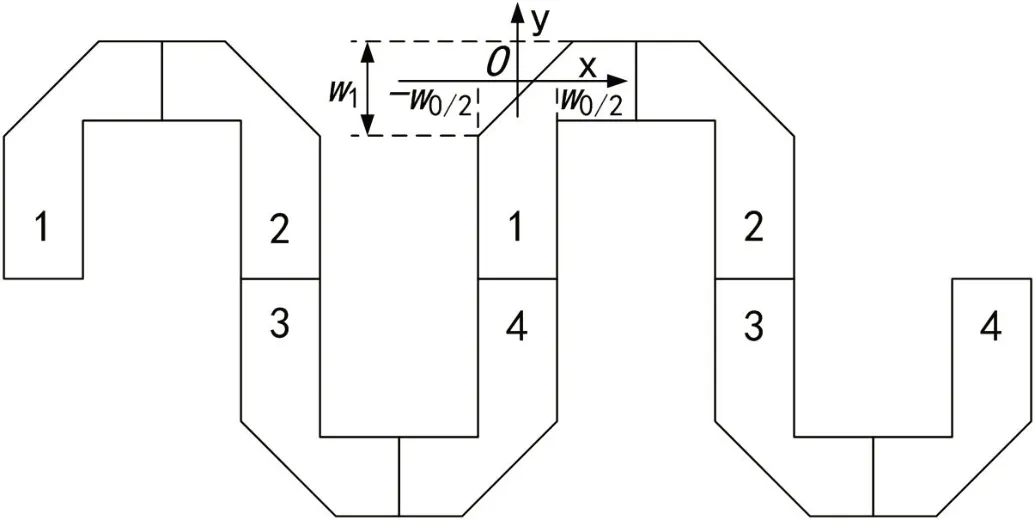

VBS 是一种基于Visual Basic 语法的脚本语言,可直接调用大量Windows 的库函数,独立完成对文本文件的批量操作,也可利用软件内嵌的函数接口实现批量化建模、仿真、设计工作。ANSYS EM 是一种代表行业标准的三维电磁仿真软件,Altium Designer 是一种成熟的PCB 设计软件,两者都提供较为完善的VBS 接口。为适应以上两种软件的函数特点,将时延线中的蜿蜒结构分解为直通传输线和图4 中的四种基本单元,单元的相对坐标和主要参数如图4 所示。

图4:内埋时延线形状分解示意图

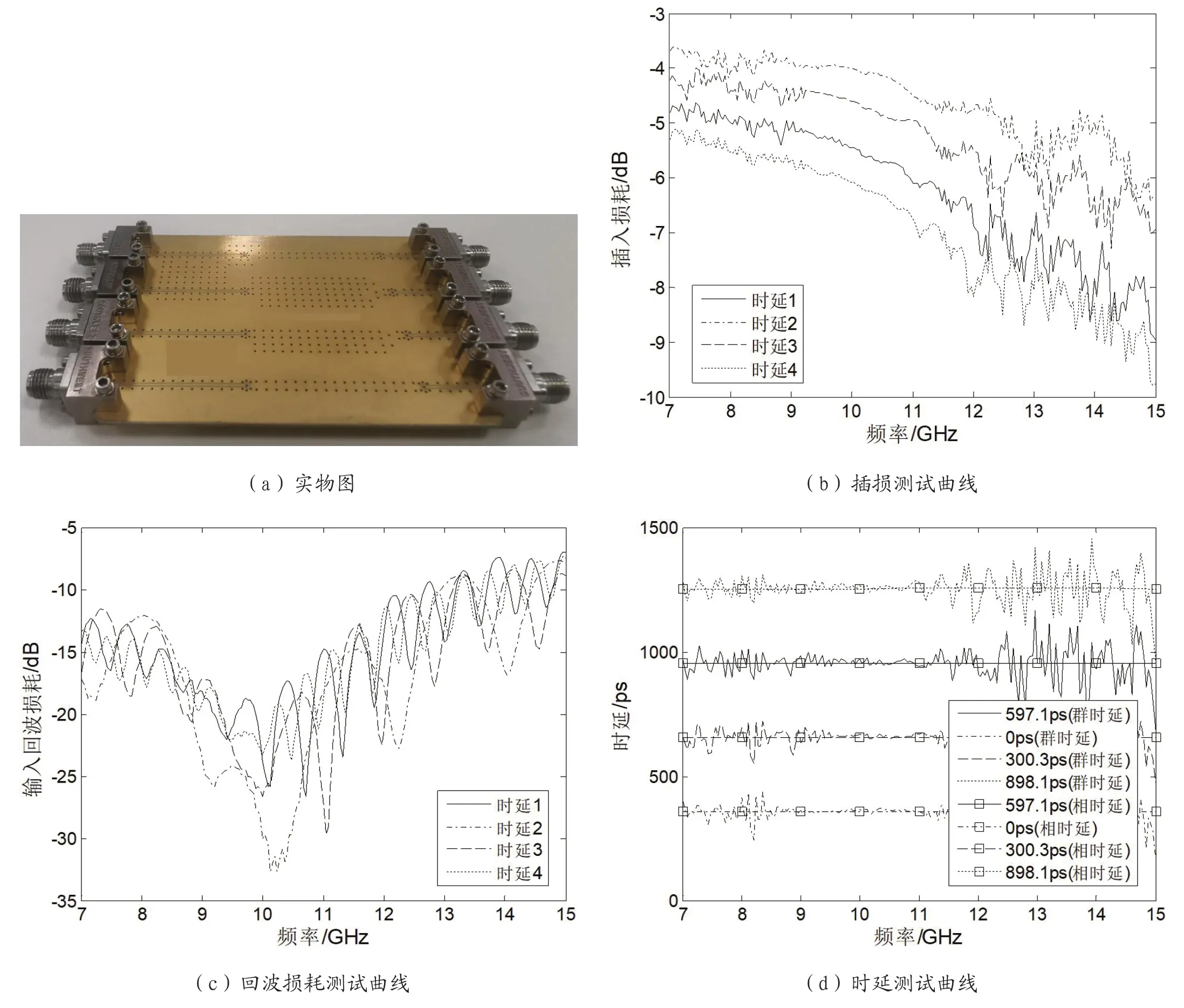

使用这一基本单元可构成图4 所示的0ps、300ps、600ps、900ps 4 态时延线。可以看出,除用于增加路间隔离的通孔外,整个时延线模型均可以分解为直通传输线和图5中的四种基本单元,而给定坐标和孔径后,通孔本身也可以使用VBS 脚本方便的进行批量建模。

图5:4 态时延线模型示意图

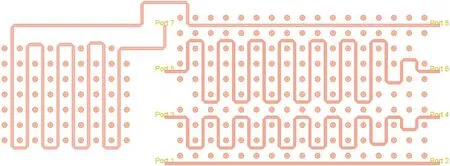

以上模型的S 参数仿真结果如图6 所示。

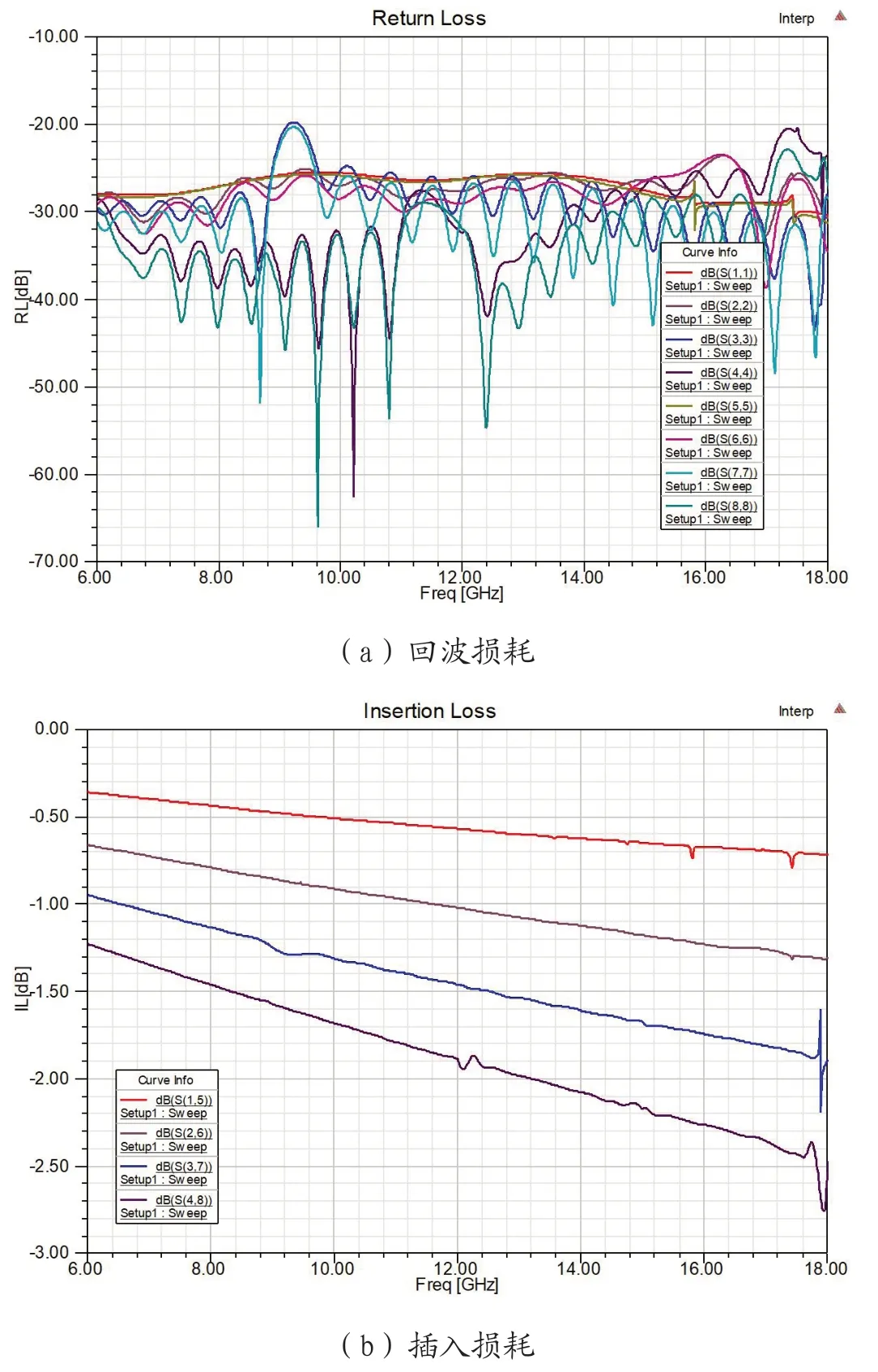

图6 中,图6(a)为全部8 个端口的回波损耗曲线,包括输入回波和输出回波曲线,而图6(b)为所有4 个时延态的插入损耗曲线。可以看出,所有回波损耗曲线在关注频带内优于20dB,而插入损耗曲线随频率线性增加,其中,900ps 位的传输线在带内的最大损耗约3dB。上述模型的群时延仿真结果如图7 所示,图7 中可见明显的毛刺,这是因为有限元数值仿真计算中存在相位计算误差,而每个频点的运算相对独立,因此其误差项也存在相对的独立,这样在频率间隔较小的情况下做进一步查分运算时,就可能出现尖峰或突变。

图6:三维全波仿真结果

图7:时延线群时延仿真曲线

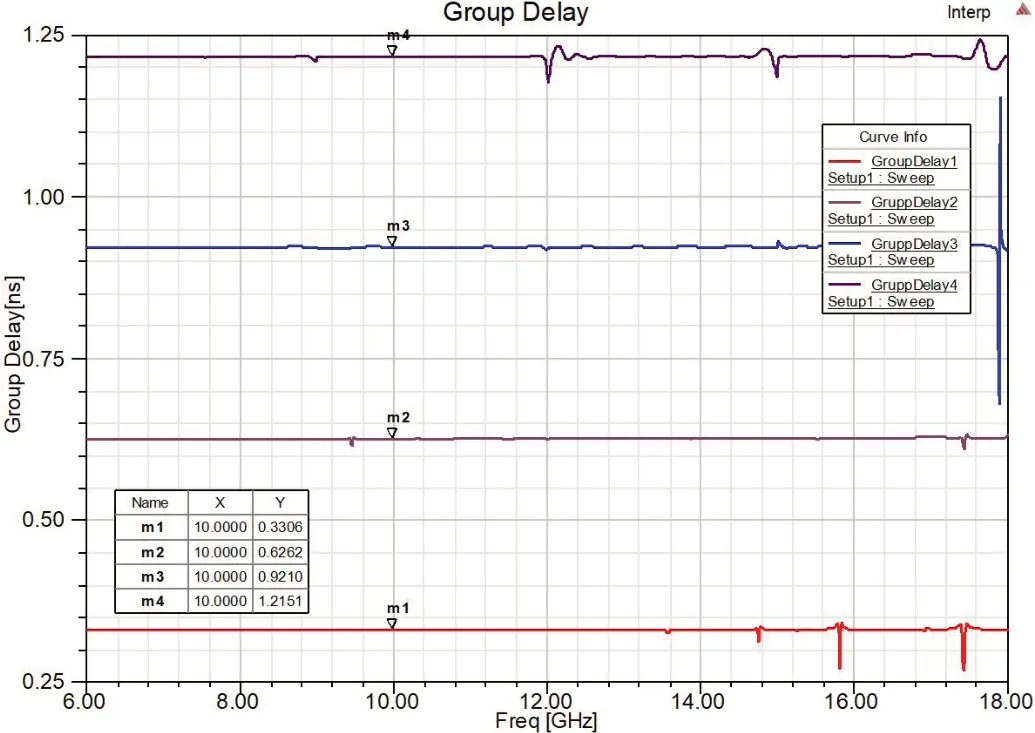

3 实物加工及测试验证

对前述4 态时延线进行了加工,实物如图8(a)所示。所实现的时延线尺寸不大于80mm×60mm×1mm。为降低焊锡对测试结果的影响,选用Southwest 公司出品的EndLaunch 连接器进行转接,并使用Agilent 公司的N5242A型矢量网络分析仪进行测试,测试结果如图8(b)‐(d)所示。

图8(b)为时延器的插入损耗测试曲线,测试频段为7GHz‐15GHz。可以看出,随着频率的增加,曲线的斜率也明显增加,这一方面是因为图5 中的仿真结果未计入导体损耗,而导体损耗因去肤效应,会随频率升高显著提升;另一方面,也是因为高频端的回波损耗较仿真结果相比有一定恶化,如图8(c)所示。这种恶化,一方面是由于材料及加工工艺的不理想特性造成的;另一方面也有测试夹具引入的测试误差;此外,相比于仿真模型,加工样品中还增加了额外的一组微波过孔,以及微波过孔与测试端口间的传输线,这也会造成性能恶化。图8(d)为时延线的时延测试曲线,其中,单纯线条的一组曲线为群时延曲线,增加方块符号的一组曲线为相时延曲线。可见,由于回波损耗的恶化以及矢网相位测量的偏差,群时延的测试结果波动较大,但通过延展相位计算得到的相时延曲线则非常平坦,且其时延量较设计值非常接近,相差最大的时延态为600ps 状态,时延量不超过3ps。

图8:4 位时延线实物及测试结果

4 结论

本文介绍了一种基于VBS 脚本语言的宽带微波多层印制时延线设计方法,利用VBS 脚本与仿真、设计软件间的便利接口,实现蜿蜒时延线的批量自动建模、仿真和设计,并利用这一方法研制了一款工作于Ku 频段的宽带4 态时延器。所研制的时延器工作带宽达到8GHz,最高工作频率达到15GHz,可覆盖X 频段上、下行,Ku 频段上、下行的卫星通信系统。所研制的时延线在设计频段内具有较好的插入损耗和回波损耗特性,且时延量的测试值和设计值差值仅有不到3ps。所研制的4 态时延器可以在80mm×60mm×1mm的电路板上实现0ps、300ps、600ps、900ps 共4 种独立的时延电路,辅以四选一电子开关,即可实现2 位高指标数控时延线,具有较高的应用价值。此外,所研制的4 态时延线,验证了所提出设计方法的有效性和便利性,对此类时延线的设计有较强的指导意义。