基于DSP的UUV目标探测通用系统设计与实现

2022-10-27宋家平朱衍明刘一博王天昊

宋家平,朱衍明,刘一博,王天昊

(中国船舶集团有限公司 系统工程研究院,北京 100036)

0 引言

随着目前集成电路的工艺和技术的高速发展,电子信息技术也在高速发展中,DSP(digital signal processor)已经成为数字信号处理技术应用中必不可少的重要器件之一。DSP已经广泛应用到航天航空、军事领域等相关领[1]。在一些对信号处理数据量大、实时性高、高速计算的应用中,单单依靠DSP芯片的信号处理能力往往不能满足需求,高度集成的多处理器系统逐步成为高速信号处理平台的主流方案[2]。FPGA(field programmable gate array)是一种可编程逻辑器件,拥有丰富的高速接口,能通过使用预建的逻辑块可重新编程布线资源来实现特定的电路结构[3]。

当前DSP和FPGA的协同数字信号处理系统主要应用于雷达信号处理[4]、语音信号处理[5]、图像处理[6]等领域。在[7]中,实现了一种能够对以太网、CAN等不同协议数据进行解析、过滤及转发的多协议网关,该网关采用DSP+FPGA的控制器架构DSP作为控制核心,调用FPGA实现的驱动函数实现以太网和CAN数据收发,并根据特定的转发策略对接收数据进行解析、过滤和转发,试验结果表明,该多协议网关单元具有通信接口种类多、数量多,数据转发实时性强、可靠性高,数据解析、转发规则可编程设定、灵活性高等特点,能够适应不同系统的应用需求。在文献[8]中提出运用DSP与FPGA相配合的方式控制CAN总线实现数据传输,提高高速条件下数据传输的稳定性和可靠性,实验结果表明,系统数据传输过程稳定可靠,可以基本满足高速信号的处理与传输要求。

水下无人航行器(UUV,unmanned underwater vehicle)作为一种复杂的水下机器人,其探测系统主要通过声、光、电、磁等多种物理场信息的采集和处理,实现对水下目标的搜索、探测等任务。因此,利用DSP的数据高速处理能力和FPGA的高速接口数据交互能力,基于DSP和FPGA协同处理架构,在高速数据通信、高实时性声、光、电、磁等数字信号处理的UUV水下目标探测应用场景中,实现同时具备两者优势,发挥各自特点优势。实现了通用的目标探测处理系统平台。通过FPGA扩展DSP,不仅解决了DSP通信资源不足的问题,而且通过FPGA实现一些通信接口的逻辑设计,降低了电路设计的复杂度。并通过以太网完成上位机到目标探测系统的指令或数据映射,以设备地址定义不同RS232设备等,通过对不同地址进行读写地址数据操作,从而实现了对不同探测系统外围设备在目标探测前和处理后的控制。

1 系统总体设计

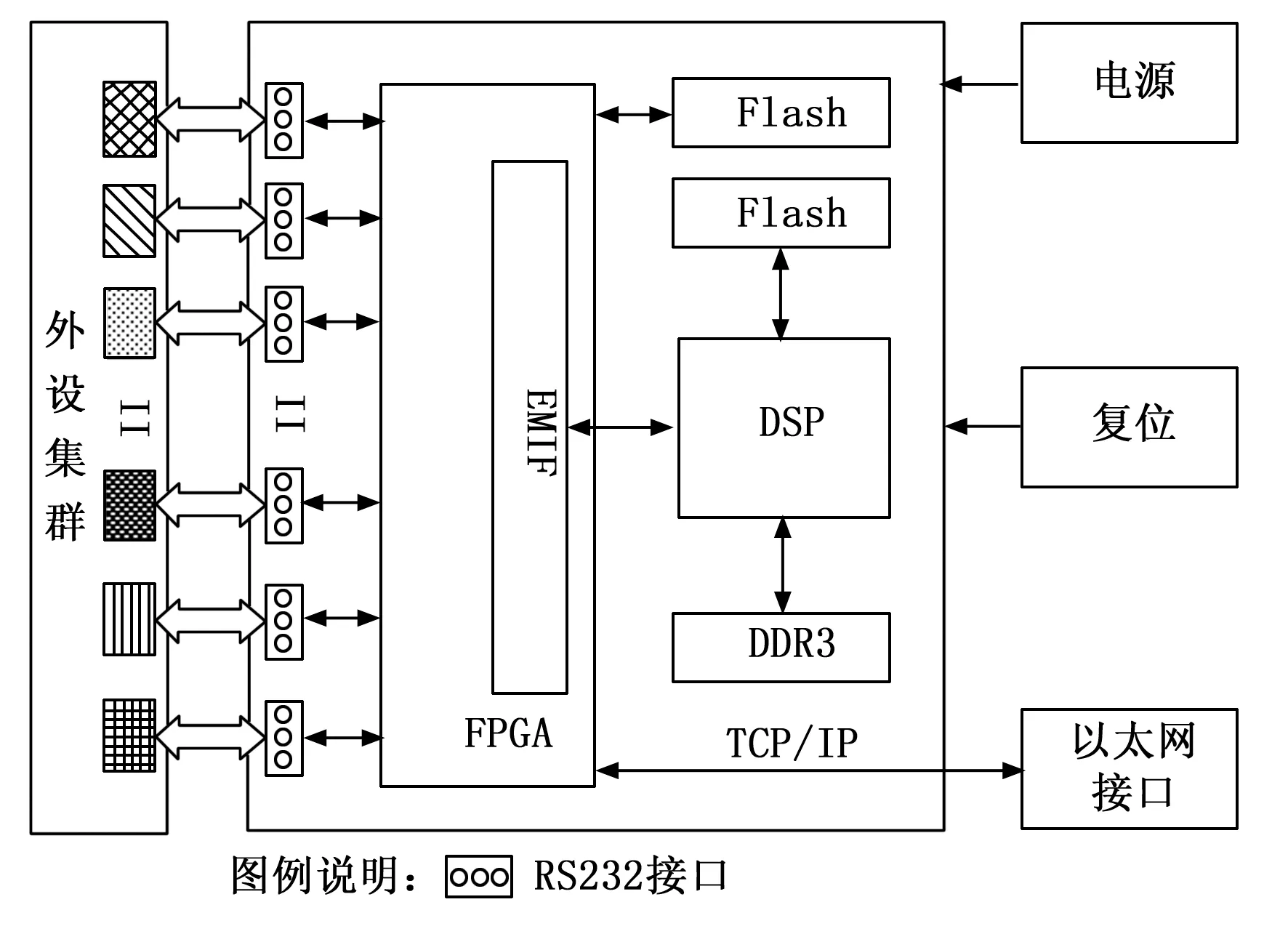

基于DSP的UUV目标探测系统总体设计的核心思想是构造一个具有可扩展性、标准化、模块化的硬件平台,再结合模块化软件设计,使平台具有很高的灵活和通用性。该系统主要实现了16路RS232串口数据的发送及接收,根据不同的需求后期可扩展 CAN通信以及RS485通信等,实现对不同接口的外围设备的控制,从而更快地获得更多、更全面的目标信息,便于目标的处理和识别,总体设计如图1所示。

图1 系统总体设计框图

由于DSP的接口资源有限,以及FPGA具备多个工作单元并行处理和实时数据传输的能力[9],为降低外围硬件电路的设计难度和提高该系统的灵活性、通用性、扩展性[10],该系统采用了FPGA来对DSP进行功能的扩展。

图1中,通过TCP/IP协议栈的网络通信实现以太网到目标探测系统的指令或数据映射,以设备地址定义不同RS232外围设备,通过对不同地址进行读地址数据操作,并将这些数据信息发送到FPGA,在FPGA内部做FIFO缓存、串并转化等;再通过EMIF接口将处理后的数据传输给DSP端,充分使用DSP强大的数据处理能力和灵活的配置能力[11],实现目标探测信号处理和识别的各种复杂的算法;DSP端先将数据存储到DDR3中,再根据需要将数据读出内存进行相应的处理,处理后通过EMIF接口传输给FPGA端;最后,再由网络通信实现对不同RS232外围设备的写操作,从而将最终处理的数据映射到不同的外围设备,经行目标识别后的操作,如:显示目标的特征信息、具体方位信息等。至此便实现了目标探测信号处理和识别的整个过程。FPGA Flash控制模块和DSP Flash控制模块,分别实现FPGA和DSP各自程序的在线加载和更新。

2 硬件设计

2.1 FPGA芯片选择

本系统设计的主控单元使用Xilinx 公司Zynq7000系列的XC7Z045T芯片。该芯片集成了ARMCortex-A9双核处理器的处理系统(PS)和基于Xilinx 可编程逻辑资源的可编程逻辑系统(PL)。可对该芯片的PS端和PL端进行独立开发,并根据控制需求进行系统的软件和硬件划分,从而将PS和PL各自的优势发挥出来,让整个系统呈现出最佳性能,该芯片还具有丰富的外部接口、内外部存储以及灵活的配置[12]。

2.2 DSP芯片选择

DSP采用美国TI公司的8核C66x CorePac芯片TMS320C6678,其核心工作频率为1.25 GHz,运算速度最高可达320 GMACS/160 GFLOPS。该芯片采用了同构多核架构,具有4 MB供8个核心访问的共享内存,以及具有SRIO、PCIe等多种接口,每个核均有512 KB的私有内存,可独立地执行特定的计算任务。可满足各种不同数据传输的应用需求,完全向后兼容所有现有的C6000系列定点和浮点DSP[13]。配合外围DDR3、Flash等,为整个模块提供数字处理平台。

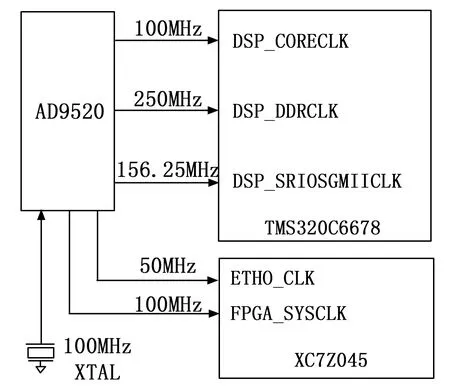

2.3 时钟分配方案

多模块集成设计需要具备相应的时钟分配方案,如图2所示。在本设计中使用1片ADI公司的AD9520时钟产生芯片为所有的工作模块提供低抖动、稳定的参考时钟。该芯片是一款极低噪声PLL时钟频率合成器,集成VCO、时钟分频器和12路1.6 GHz LVPECL/CMOS输出,具有自动保持和灵活的参考输入电路,支持非常平稳的参考时钟切换,该系列还可以提供用于外部VCXO的必要配置[14]。

图2 时钟分配方案

通过配置SPI总线对其进行编程设计,产生250 MHz、156.25 MHz、100 MHz和50 MHz 的时钟分别提供给DDR3工作时钟、SRIO模块时钟、FPGA的系统时钟及多核DSP内核和以太网模块时钟等。

2.4 电源部分

在整个系统的设计中电源设计作为平台设计的基本环节,为了达到给多核DSP、FPGA以及其他的芯片提供正确、安全、稳定供电的目的,电源部分设计也是最为复杂和繁琐的一个环节。本系统采用了3片ADI公司的LTM4644降压型μModule(电源模块)稳压器为总体系统提供所需要的各种电压值。

LTM4644可在一个4~14 V或2.375~14 V(采用一个外部偏置电源)的输入电压范围内运作,LTM4644/LTM4644-1支持一个0.6~5.5 V的输出电压范围。该器件的高效率设计使每个通道能够提供4 A连续(5 A峰值)输出电流,仅需大容量的输入和输出电容器[15]。

2.5 以太网接口

以太网接口采用TI公司DP83848以太网PHY,DP83848C是美国国家半导体公司生产的一款鲁棒性好、功能全、功耗低的10/100 Mbps单路物理层(PHY)器件。支持10 Base-T和100 Base-TX以太网外设,对其他标准以太网解决方案有良好的兼容性和通用性,其电路结构如图3所示。

图3 百兆以太网接口

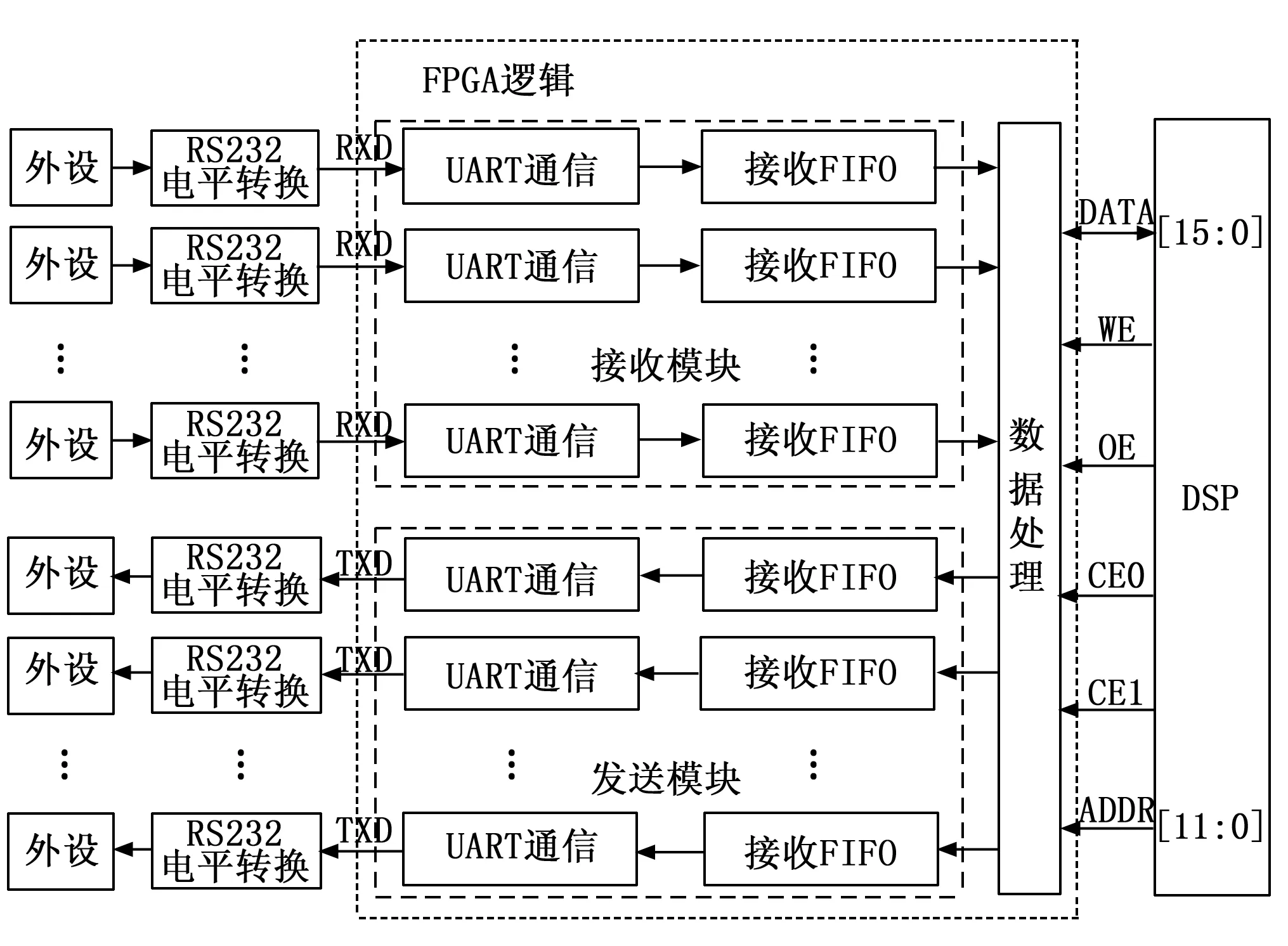

2.6 多路串口逻辑设计

该系统的RS232串口部分采用了模块化的电路设计。FPGA的功能逻辑如图4所示,它包括发送模块、接收模块和数据处理模块[10]。由于不同的外围设备有不同的串口通信需求,因此,该系统每一路串口通道均采用了独立的设计,而且,DSP可根据各自的需求对每一路串口动态设置波特率、起始位、数据位、奇偶校验位及停止位等工作参数,以提高其灵活性和通用性。

图4 串口逻辑设计

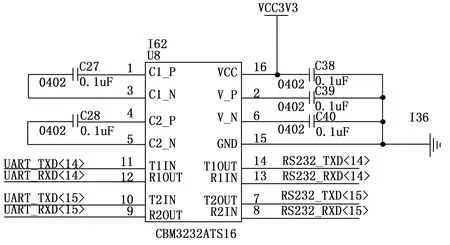

2.6.1 RS232接口设计

RS232接口电平转换芯片采用芯佰微公司的CBM3232。它是一种基于EIA/TIA-232标准和V.28/V.24标准的通讯接口,其供电电压为3.3 V、具有低功耗需求,高数据传输率能力,其电路结构如图5所示。

图5 RS232接口电路图

CBM3232有两个接收器和一个驱动器,该设备可以确保以RS-232标准输出电平水平的情况下以120 kbps数据传输率运行。典型应用包括笔记本计算机、轻型便携掌上电脑、电池供电的设备、手持式设备、电子周边设备和打印机[16]。

2.6.2 UART通信

通用异步接收器或发送器(UART,universal asynchronous receiver/transmitter)是一种全双工传输模式[17],主要用于串行传递数据。它的基本原理是:一方面,在接收数据时,将接收到的串行数据转换成并行数据;另一方面,在发送数据时,将并行数据转换成串行数据来进行传输,实现将信息在串行通信与并行通信之间传输和转换。

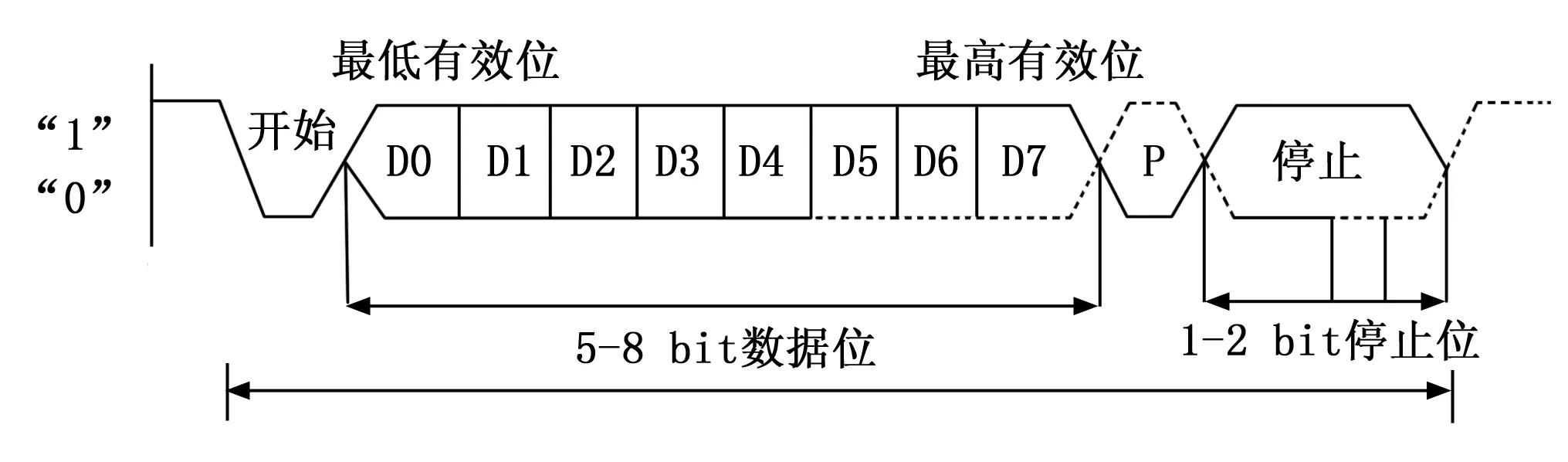

UART的传输链路时以数据帧为基本单元进行传输的,如图6所示。其一帧数据长度一般是5~8 bit,包括起始位、数据位、校验位与停止位;可根据需要选择是否采用校验位,校验模式包括奇校验和偶校验,停止位长度包括1 bit、1.5 bit、2 bit,一般根据当前UART链路传输要求选用合适的数据格式[18]。

图6 UART串行异步通信数据格式

2.6.3 收发FIFO缓存数据

FPGA使用的FIFO一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存,或者高速异步数据的交互也即所谓的跨时钟域信号传递[19]。FIFO 可以将连续的数据流在进栈和存储之前集中缓存起来,不仅可以防止数据丢失,还可以使若干个数据一起进行处理避免频繁的总线操作。收发FIFO采用8×256的容量,数据位宽度为8位,存储深度为256 byte,FIFO_empty作为FIFO是否有数据的标志信号。

2.6.4 数据处理及与DSP的通信

FPGA芯片对不同的串口通道分配了不同的片选地址,DSP在每个串口通道进行参数初始化设置和收发数据设置时,首先,根据设置的片选地址找到相应的寄存器,其次,通过总线的形式收发存放在不同地址中的数据,最后,根据需求对所有通道的数据进行相应处理。根据图4中的串口逻辑设计,当接收到其中某一路串口通道数据时,DSP读取该通道对应的FIFO_empty值,若有数,则DSP从该通道对应的寄存器地址获取已完成串并转换的数据。类似地,在发送指令或数据至串口通道时,DSP通过总线把带有帧头、帧尾的完整数据包发送到对应的FPGA寄存器,然后,FPGA将该数据存入对应串口通道的发送FIFO中,最后,完成并串转换后把该FIFO中的数据转成串行形式逐位传送至外部设备。

3 软件架构

3.1 UART通信

通过采用VIVADO开发平台和VHDL 硬件描述语言,UART通信在逻辑电路层面开展了模块化的设计和开发。包括波特率发生器;UART接收器;UART发送器三个功能设计模块。

首先,波特率发生器的设计本质就是对分频器的设计。而分频器的设计最重要的步骤就是确定分频数,即波特率的分频因子。本系统的UART通信分频因子通过给定的UART时钟频率和外围设备要求的波特率计算得出。根据UUV目标探测系统不同传感器设备的通信协议可对波特率分频因子更改。

UART接收器设计的目的是接收串行通信数据。当 UART 接收使能变量置1时,开始接收RXD数据信号,直至信号FIFO_empty变为 1,此时 FIFO已满。串行通信数据接收的帧格式如图6所示,UART接收器的设计通过状态机来实现,其状态转移过程如图7所示。

图7 UART接收器状态转移过程图

S0表示空闲等待状态,具体表现是RXD数据线为低电平,此时UART接收器模块一直在等待状态。当UART接收的数据被检测到低电平后,便进入到S1状态。S1状态的目的是消除电磁干扰所产生的低电压毛刺对UART接收数据的干扰,若是干扰,返回到S0状态,否则进入数据接收状态S2状态。在S2状态下通过9位的寄存器完成包含8位数据和1位奇偶校验位的数据接收和存储,然后进入S3状态。S3状态是对接收到的数据进行奇偶校验的状态,若校验有误,提示相关错误信息;反之,提示完成数据接收,并进入下一次接收等待的S0状态。

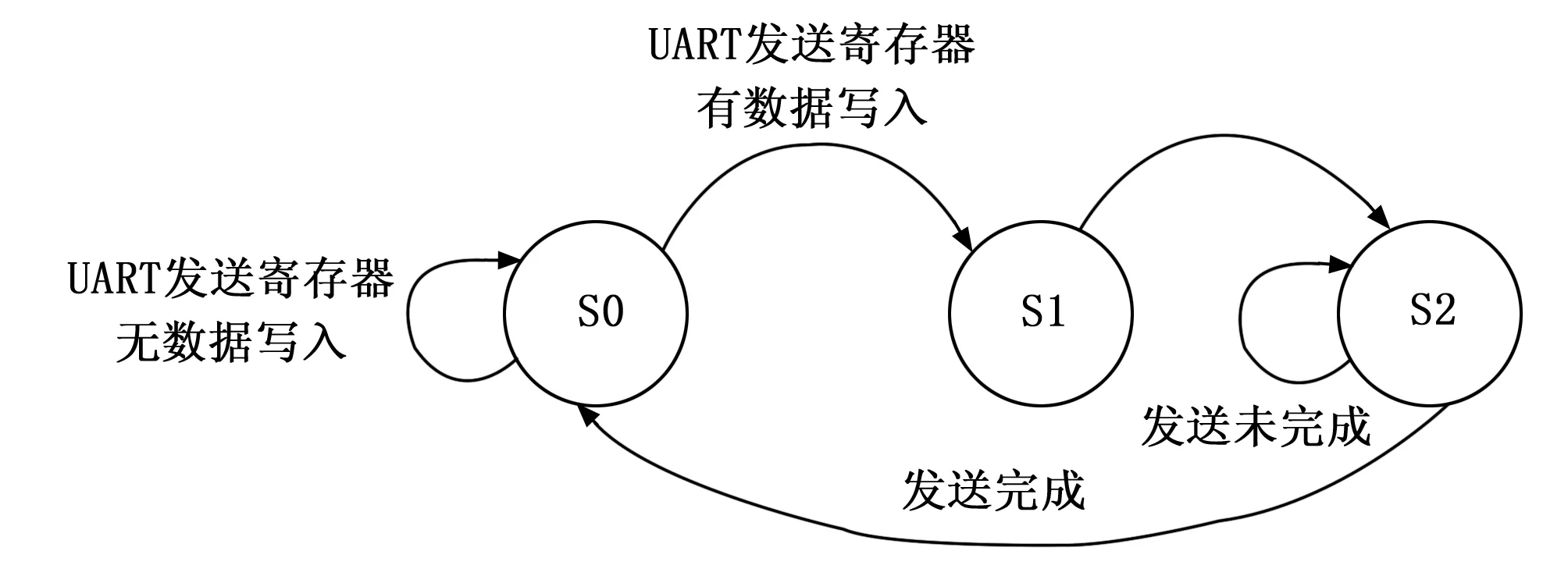

UART发送器模块设计的目的是串行发送数据,在发送使能变量和发送 FIFO均不为0时,读取该FIFO中的并行数据,经过并串转换后,在首位加入数据起始位,末位加入奇偶校验位以及停止位,形成完整的串行数据帧;最后按照事先设定的波特率完成串行发送,UART发送器模块状态转移过程如图8所示。

图8 UART发送器状态转移过程图

S0表示空闲等待状态,在该状态下一直等待主控处理器发来数据。当发现有数据写入时,由S0状态转为S1状态。S1为奇偶校验位设置状态,通过开启校验电路,根据写入的数据和奇偶校验规则或算法设置并获取相应的校验结果,并将其添加到数据特定位后,完成相应的校验位生成,S1状态进入S2状态。S2状态为数据发送状态,将包含数据起始位、奇偶校验位以及停止位的完整数据帧向外发送,直至完成所有数据的发送,接着回到S0状态,进入下一次发送等待状态。

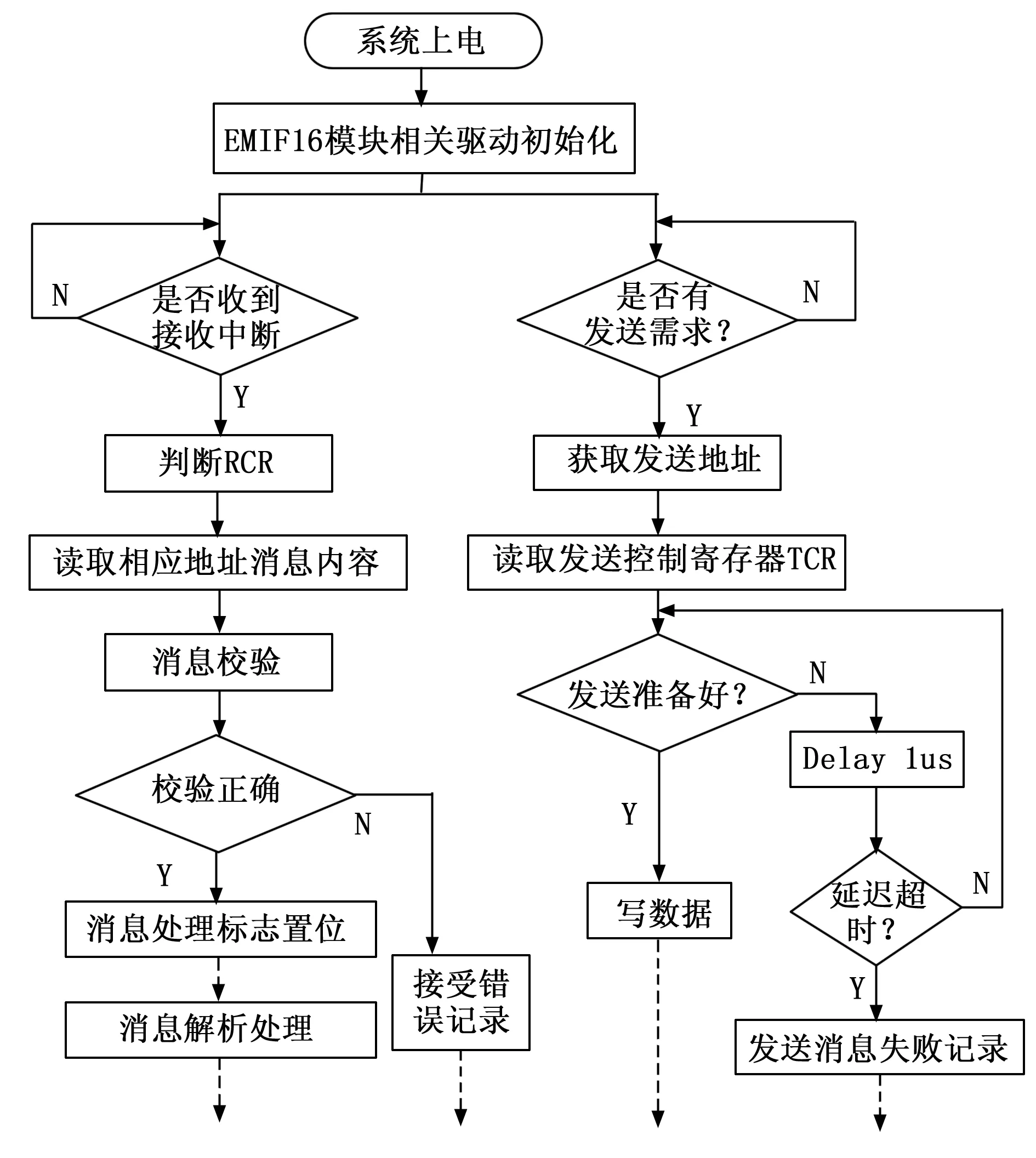

3.2 EMIF通信

由于TMS320C6678的外部存储器控制接口是EMIF16,因此,EMIF通信的软件设计就是对EMIF16模块的初始化参数配置进行设计。该EMIF16模块的寄存器地址配置范围是0x20C00000~20C000FF,它包括26组寄存器[20]共256字节。具体包括异步等待周期寄存器(AWCCR)、EMIF模块中断相关寄存器(IRR、IMR、IMSR、IMCP)、EMIF模块版本及状态寄存器(RCSR)、异步配置寄存器(ACR)等[21]。该系统通过对上述寄存器逐一进行相应的编程配置,完成了DSP对EMIF16模块的初始化编程。寄存器编程配置时根据其需求进行重点位域的编码,与本系统无关的寄存器选择默认值对其进行了配置。完成配置后开始设计和实现上层应用系统,本系统中DSP和FPGA基于EMIF16异步通信的软件流程如图9所示,主要实现数据的接收和发送功能。

图9 EMIF通信软件流程图

该系统上电后,EMIF模块接口完成初始化程序后开始和外接设备进行通信。对于需要依靠系统告知EMIF模块进行数据接收这种被动模式下,通过GPIO发送中断信号以实现辅助接收数据的功能;即FPGA端即将发送的数据在准备好之后,拉高GPIO管脚电平,DSP端收到该GPIO上升沿信号后触发中断信号Interrupt,开始执行中断函数,判断数据接收控制寄存器(RCR),并开始接收数据。对于DSP端直接读取EMIF模块完成数据发送这种主动模式,在每次发送数据时需要对FPGA端的数据准备状态进行查询,确保发送控制寄存器(TCR)对应的状态准备已完成才开始发送相应的数据,以保证发送数据的稳定性。

3.3 以太网通信

在该系统中,为实现基于TCP/IP以太网协议的上位机与UUV目标探测传感系统之间的通信,XC7Z045T芯片对硬件逻辑电路模块和IP核采用Verilog语言设计编程。传输控制协议/网际协议简称为TCP/IP协议,它包含多个不同层次的协议族组合[22],其中的TCP和IP 协议是两个重要的计算机通信协议。本系统以太网通信的设计使用应用层、传输层、网络层、链路层,以及一路物理层组成的五层网络协议,其设计流程如图10所示。

图10 以太网通信设计流程图

上位机应用程序在通过TCP/IP以太网协议栈发送数据时,要对数据进行逐级打包和封装,在该过程中,接收数据的首部或尾部将会被每个协议层添加相应的信息;在目标探测传感系统接收通过TCP/IP协议发送过来的数据时,首先将数据流由下往上逐层解析相应接收到的数据,然后去除对应的首部或尾部的信息,保留其发送的有效数据。

应用层通过提供各种协议目的是对接收的数据进行解释。TCP/IP的应用层协议包括文件传输协议(FTP 协议)、TELNET协议、超文本传输协议(HTTP 协议)和简单邮件协议(SMTP 协议),在使用过程中根据传输不同数据的需要选择不同的协议。本系统主要采用了文件传输协议(FTP协议)和超文本传输协议(HTTP 协议)。

传输层主要时负责两个端系统之间的可靠数据传输,为传输数据两端的系统提供建立、维护和断开连接等功能。在 TCP/IP 的传输层协议族中,一般使用可靠传输的传输控制协议(TCP)和不可靠传输的用户数据报协议(UDP)。UDP 协议是不面向连接的,其无法保证数据传输的可靠性;但 TCP 协议是面向连接的,可保证可靠的数据传输。若传输层接收的是 UDP 报文,则根据 UDP 协议中对应的端口,分别送给不同的应用程序;若接收的是 TCP 报文,则需要根据 TCP 的状态转换过程图进行处理。在本系统中采用 TCP 协议为传输层协议。

网络层在数据链路层传输功能上,进一步处理网络中发送方到目的地报文地址和路由信息等数据的通信,并且一般具备为传输层提供服务、组包和拆包、选择路由等功能,目的是实现两个数据传输端之间的数据透明传送及相关的协议封装。具体的过程是,网络层在接收到数据链路层发送的数据包后,根据 IP 数据帧中的协议种类,首先去掉 IP 首部数据,然后形成 TCP、UDP 或是 ICMP报文后再对数据进行相应的处理。网络层传送数据采用IP 协议机制,它是 TCP/IP协议栈的核心。因此,本系统的网络层们选用了IP协议和ARP 协议来实现 IP 地址到 MAC 物理地址的转换。

链路层一般包括系统的网络接口和设备驱动应用程序,目的是用于定义计算机如何连接网络。数据链路层要实现数据传输功能必须要连接网络,它主要负责接收和发送以太网数据帧,并将数据首部信息剥离,然后根据以太网数据帧的上层协议分别传输到上一层,完成将所传输的原始数据转换成上一层能够识别的逻辑帧。

物理层包括MII/GMII(介质独立接口)子层,PCS(物理编码子层),PMA(物理介质附加)子层,PMD(物理介质相关)子层以及MDI(媒介相关接口)子层。本系统的设计使用了MDI子层,即使用 RJ45 接口将设备接入网络。

4 系统测试

基于DSP的UUV目标探测通用系统设计完成后,需要对其进行功能性数据测试,测试的内容包括网口硬件测试、系统与上位机的连接测试,以及RS232设备的读写操作测试。其测试环境的搭建过程为:首先使用笔记本电脑作为以太网通信上位机,然后通过网线将上位机与被测板卡百兆网口相连,最后使用RS232调试串口观测每一路的调试结果。

4.1 网口硬件测试

使用JTAG将测试例程,加载到FPGA中,再使用SDK软件加载测试执行程序,通过调试串口观测结果如图11所示。

图11 程序加载后,串口的观测结果

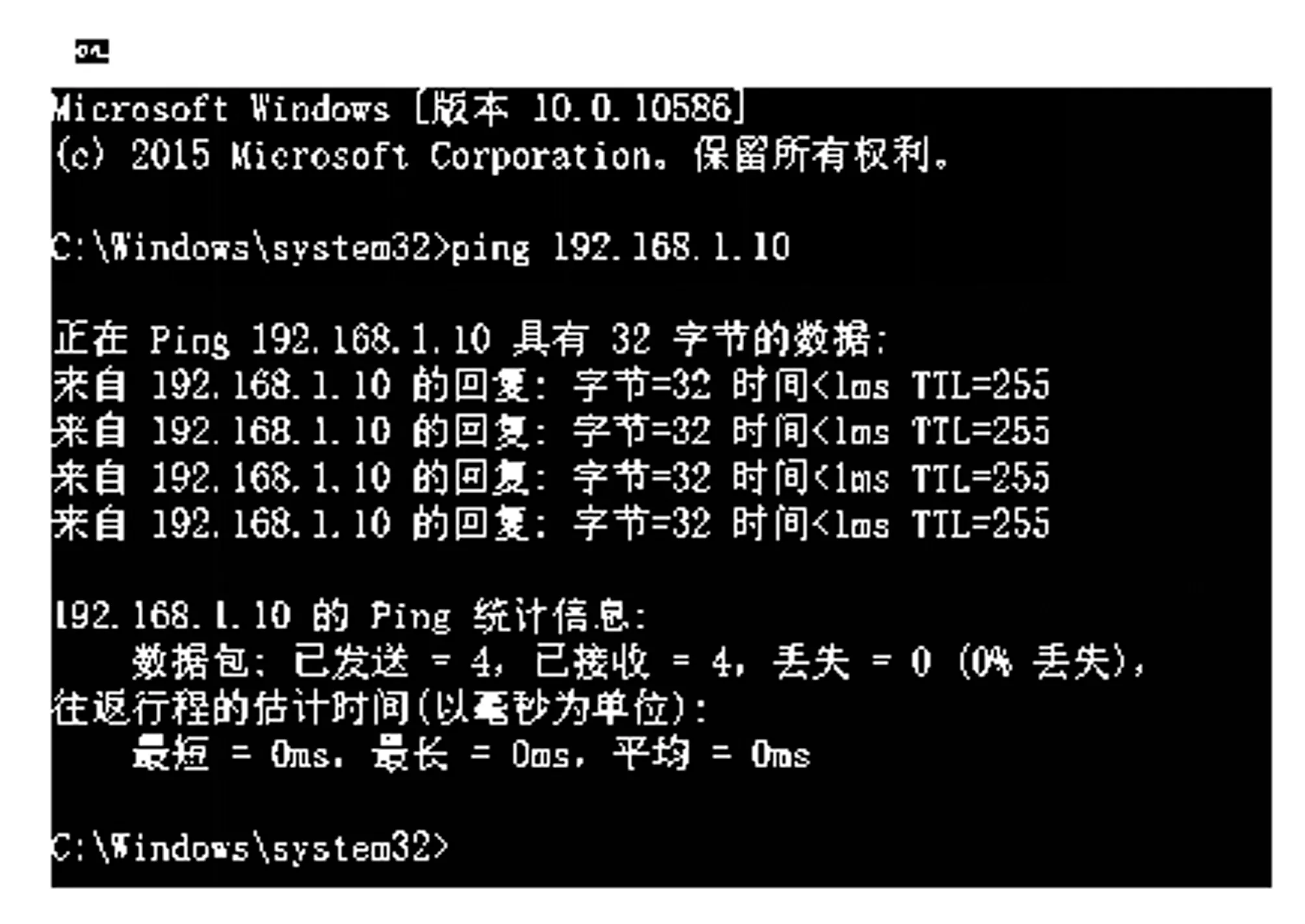

以上结果,显示百兆网PHY自协商正常,测试Server配置正常,目标端机IP:192.168.1.10,端口:7;再通过使用Ping命令,测试网络通信是否正常,其测试结果如图12所示。

图12 网络通信的测试结果

由图12可知,百兆网口通信正常,至此,硬件测试完毕,进行上下位机软件功能测试。

4.2 系统与上位机的连接测试

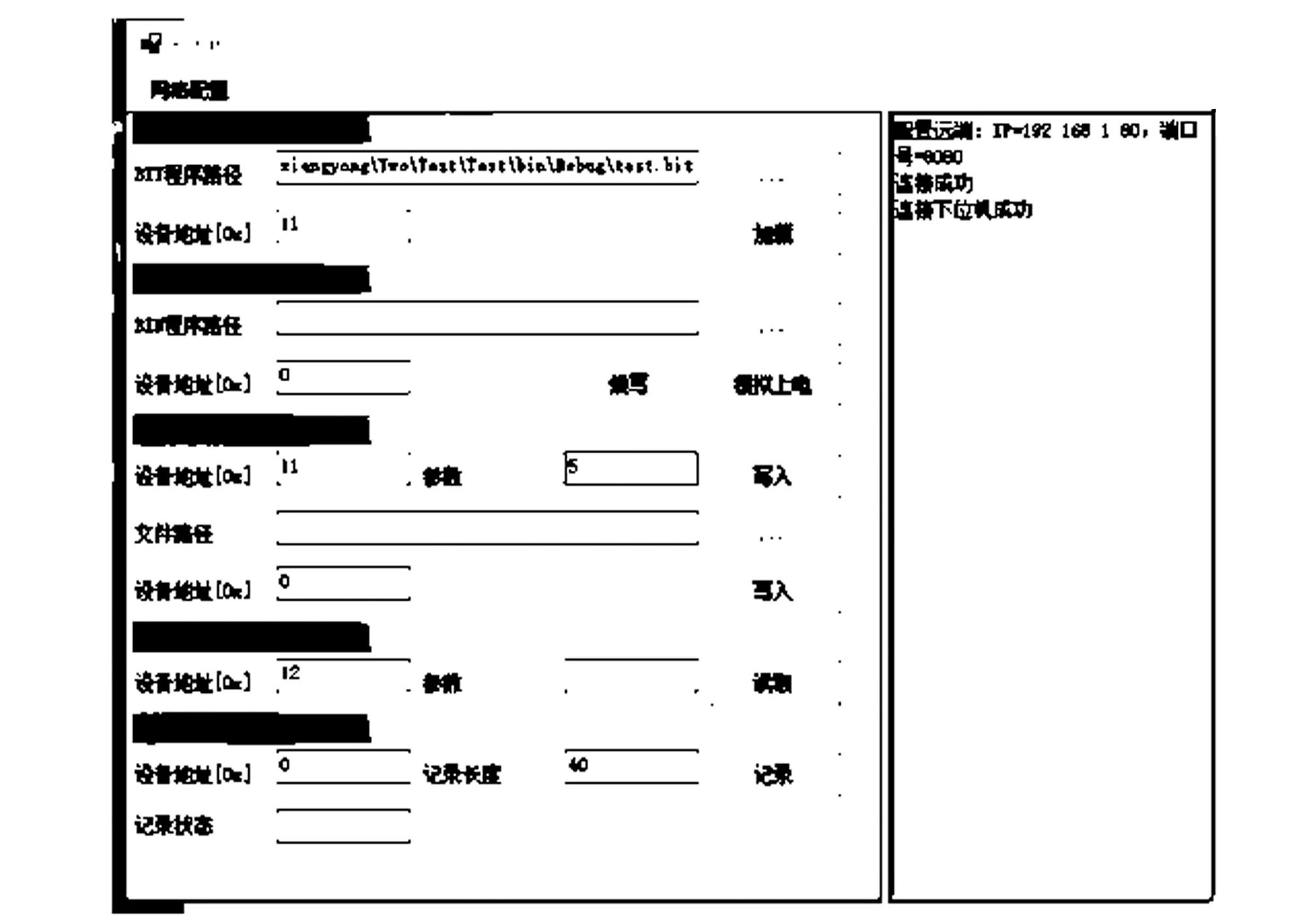

该上位机软件通过TCP/IP协议与下位机进行交互,上位机作为客户端,下位机作为服务端。下位机的IP和端口可在上位机可执行程序对应目录下的配置文件中配置,实现上位机软件启动时主动连接下位机的操作。也可以在上位机软件启动后连接下位机失败时,手动输入下位机IP和端口进行连接。手动连接:点击【网络配置】—>【下位机】,在弹出窗体中输入正确的IP和端口号,然后点击连接,完成系统与上位机的连接测试,其操作界面和测试结果如图13所示。

图13 上、下位机连接的操作界面和测试结果

4.3 RS232设备的读写操作测试

通过上位机,实现以太网到设备端的指令或数据映射,以设备地址定义不同RS232设备,通过对不同地址进行读写地址数据操作,实现对不同RS232设备的读写操作。

1)写操作测试:在图13中的“设备写访问”功能区中,向设备地址0x11写入十进制数据5,后侧显示数据下发成功,返回成功标识,测试结果如图14左侧所示。

2)读操作测试:在图13中的“设备读访问”功能区中,向设备地址0x12发起读请求,后侧显示数据下发成功,回读十进制数据4660,测试结果如图14右侧所示。

图14 写和读操作测试结果

5 结束语

本文设计和实现了基于DSP的UUV目标探测通用系统。首先考虑到DSP的高速数据处理能力,以及FPGA的高速接口数据交互能力,通过FPGA对其进行扩展。再结合FPGA自身的编程能力和模块化的设计,实现了每一路RS232通信接口逻辑独立化地设计。最后利用以太网完成上位机到探测系统指令或数据的映射,先给不同的RS232设备定义不同的地址,再通过对不同地址进行读写地址数据操作,从而实现了对UUV探测系统不同探测载荷及外围设备在目标探测前和识别后的处理和控制。经测试实验表明,该系统设计方案达到了对以太网传感设备和不同RS232外围传感器快速处理和控制的目的,实现了基于DSP的UUV目标探测通用系统设计。