微光探测成像系统电路设计与实现

2022-10-26陈伟男夏振涛胡继宝姜守望孙永雪李太平谢永权

姜 婷,陈伟男,夏振涛,胡继宝,姜守望,孙永雪,李太平,谢永权

〈系统与设计〉

微光探测成像系统电路设计与实现

姜 婷,陈伟男,夏振涛,胡继宝,姜守望,孙永雪,李太平,谢永权

(上海卫星装备研究所,上海 200240)

为满足微光遥感卫星领域对微光探测的需求,本文提出了一种基于微光CMOS图像传感器GSENSE2020的成像电路设计。该成像电路通过FPGA实现了对图像传感器的驱动控制以及高速图像数据的接收和传输,通过DC/DC和LDO(low dropout regulator)为图像传感器提供了低噪声供电电源,采用PMIC(power management IC)解决了FPGA上电时序问题,利用DDR3实现高速图像缓存与处理,采用eMMC达到图像数据存储速率与容量的需求,应用FPGA的IP核及原语代替CameraLink接口转换芯片实现CameraLink通信协议,从而完成图像数据直接在CameraLink接口的高速传输。实验结果表明,成像系统电路功能及性能都达到了预期设计目标,系统的输出数据率可达2.4Gbps,帧频高达25 fps,信噪比达到45.5dB。

微光探测;CMOS图像传感器;FPGA;LDO;PMIC;DDR3;eMMC;CameraLink

0 引言

CMOS图像传感器广泛应用于通信、医疗、工业、航空、航天等民用和军用领域的图像探测器中。随着其应用越来越广泛,近年来人们对CMOS图像传感器的性能要求也越来越高,尤其在晨昏、夜间等低照度条件下进行地物探测,而常规的CMOS图像传感器的性能不能满足这样的需求。因此微光CMOS传感器应运而生,开始应用于各类航天器中,可以有效扩展其工作照度条件和时段范围,在更宽的时段内对地进行观察、对地面突发事件进行快速预警,如城市监测、重大事件变革、自然灾害、生态环境评估以及社会经济参量估算等应用场景[1-3]。目前国外微光遥感卫星主要有美国军事气象卫星(defense meteorological satellite program, DMSP)搭载的可见光成像线性扫描业务系统(operational line-scan system, OLS)和美国极轨卫星(S-NPP)搭载的可见红外成像辐射仪(visible infrared imaging radiometer suite, VIIRS)[4];而国内长光卫星公司的“吉林一号”系列卫星具有夜光遥感功能,可以获取1m分辨率的彩色夜光影像,与此同时,由武汉大学与长光卫星技术有限公司联合研制的“珞珈一号”科学实验卫星是全球首颗专业夜光遥感卫星[5-6]。

本文根据某商业航天项目对晨昏和夜晚的微光观测需求,设计了一个微光探测成像系统电路[7-10],并满足高性能和高可靠性的要求。

1 系统总体方案设计概述

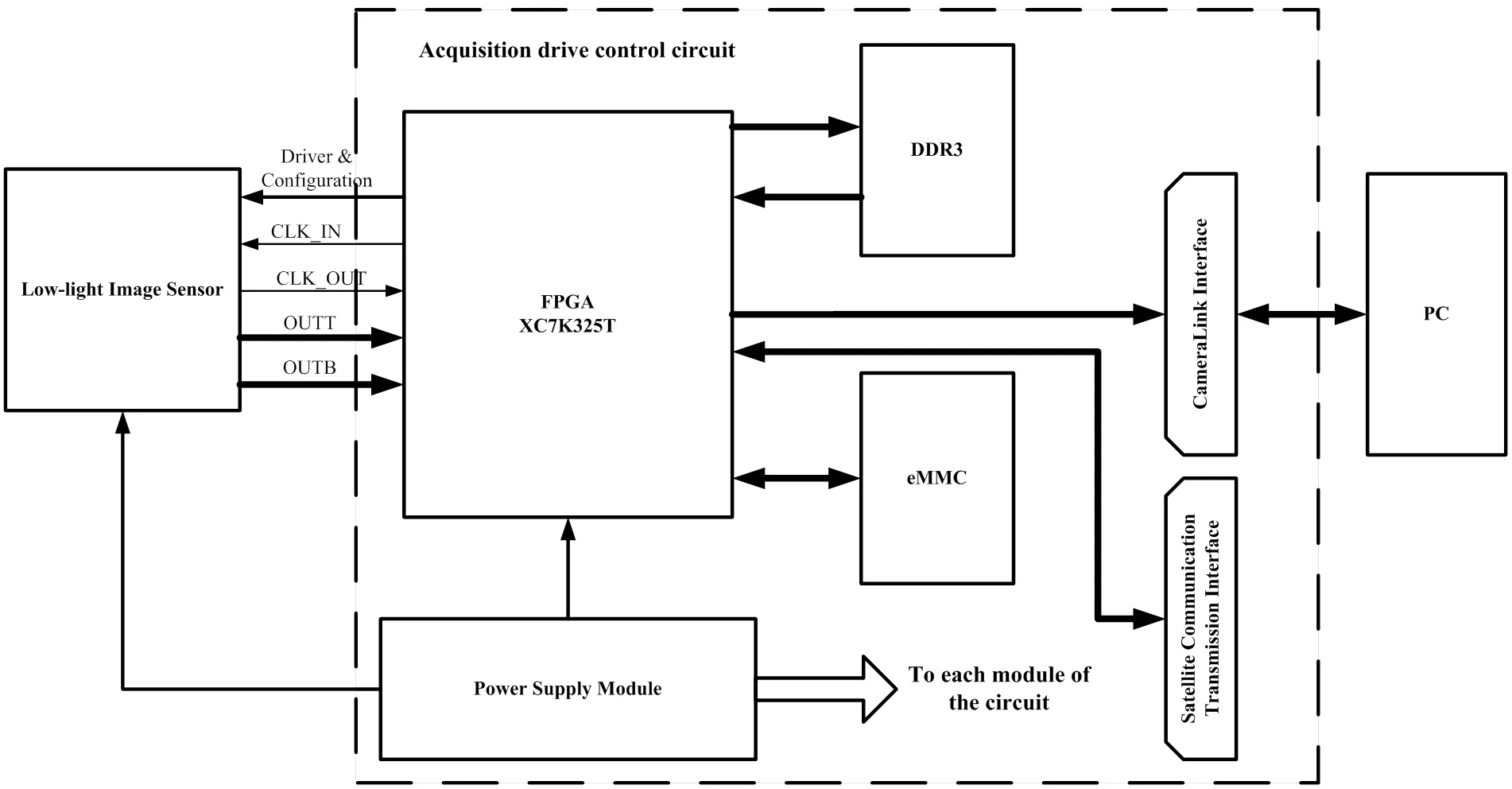

本设计的微光成像系统电路结构如图1所示,包括微光图像传感器、供电电源模块、主控处理单元FPGA、存储单元DDR3和eMMC、CameraLink传输接口及卫星通信传输接口模块等。其中微光图像传感器由电源模块提供所需的电源,在FPGA产生驱动控制脉冲控制下,通过光学系统耦合感知微光辐射并进行光电转换最终输出高速数字图像信号数据。该图像数据经由FPGA联合DDR3进行高速缓存与处理并存于eMMC,最后通过CameraLink接口上传至地面测试上位机进行显示。该系统电路实现了高帧频、高信噪比和微光探测的设计要求。

图1 成像系统电路结构

2 详细硬件电路设计

2.1 图像传感器GSENSE2020简介

本文设计中采用了GSENSE2020微光图像传感器,是由国内公司长光辰芯研制的一款背照式CMOS图像传感器,具有2048×2048的分辨率,像素尺寸为6.5mm,具有全局卷帘曝光模式。在量化位数为12bit模式下,帧频最高高达43frame/s,数据率可达4.8Gbps。当配置为低增益模式时,最大SNR可达47.39dB。

2.2 图像传感器驱动电路及电源电路设计

2.2.1 驱动电路设计

图像传感器GSENSE2020输出数字信号,具有16路LVDS输出数据通道和2对差分时钟,31个数字控制管脚以及5个配置管脚。本文采用FPGA作为控制处理单元,完成对图像传感器的驱动控制和数据采集。该FPGA选自Xilinx公司的K7系列的XC7K325T。设计中16路的数据线和2对差分时钟通过差分线与FPGA相连,36路控制线与FPGA单端相连。在PCB布局布线时,严格控制线路阻抗,16路差分数据线和2对差分时钟控制为100Ω,36路控制线设置为50Ω,并且16路差分数据线和2对差分时钟线走内部高速层,邻近上下层均为地层,形成屏蔽作用,同时做等长处理,从而保证信号质量,采集到低噪声图像数据。

2.2.2 电源电路设计

微光成像系统供电主要分为两大模块:图像传感器GSENSE2020供电电路和FPGA及其他模块供电电路。其中GSENSE2020需要4档供电电压,包括偏置电压,模拟电压及数字电压3类。图像传感器的供电电源对图像噪声有一定的影响,因此其电源设计应采用低噪声电源。同时考虑驱动能力和系统功耗,设计中采用DC/DC电源转换器和LDO(低压差线性稳压器)产生GSENSE2020所需的低噪声电压。其中DC/DC电源转换器采用了LINEAR公司的LTM4622A芯片,具有宽的输入电压范围,2A的双通道输出,将输入电压转换为4.0V、2.2V以及1.5V,再经过LDO产生图像传感器所需的电压:3.8V、3.5V、2.0V以及0.8V。LDO芯片采用了TI公司的TPS7A8300,具有2A电流和低噪声6mVrms输出,且支持软启动,便于控制上电顺序。图2为TPS7A8300的典型设计电路,其输入输出均采用去耦电容对其进行去耦,并通过磁珠对电源线路上的高频噪声和尖峰干扰进行抑制。

图2 TPS7A8300设计电路

另外,本设计采用了NXP公司的PMIC(电源管理集成电路)芯片MMPF0100,为FPGA提供电源电压。因为FPGA需要6档供电电压:1.0V、1.2V、1.8V、1.5V、2.5V和3.3V,种类比较多。同时FPGA的上电顺序有严格的要求,比如内核电压最先上电,GTX供电及其端接供电后上电,FPGA辅助供电、VCCO端口供电最后上电。MMPF0100芯片具有可配置和可编程的架构,拥有12路输出,上下电顺序灵活可控,可以满足FPGA的上电需求,保证FPGA的性能。

根据PMIC各通道输出支持的电压电流级别,以及FPGA的不同电源的需求,PMIC的硬件电路设计如图3所示。通过OTP Configuration功能对PMIC输出电压及上电顺序进行配置,并进行烧录,完成对PMIC的控制,同时将配置信息保存为可烧录的脚本文件,便于后续多块电路板的快速配置。

由于3.3V除了给FPGA供电,还需给其他模块供电,本电源电路还采用了TI公司的LDO芯片TPS7A8500。该芯片具有4A大电流和低噪声4.4mVrms输出,支持软启动,便于控制上电顺序控制。利用PMIC的LDO输出控制TPS7A8500的使能EN引脚,实现该路的电源的开关,从而保证FPGA的上电顺序要求。

2.3 DDR3 SDRAM电路设计

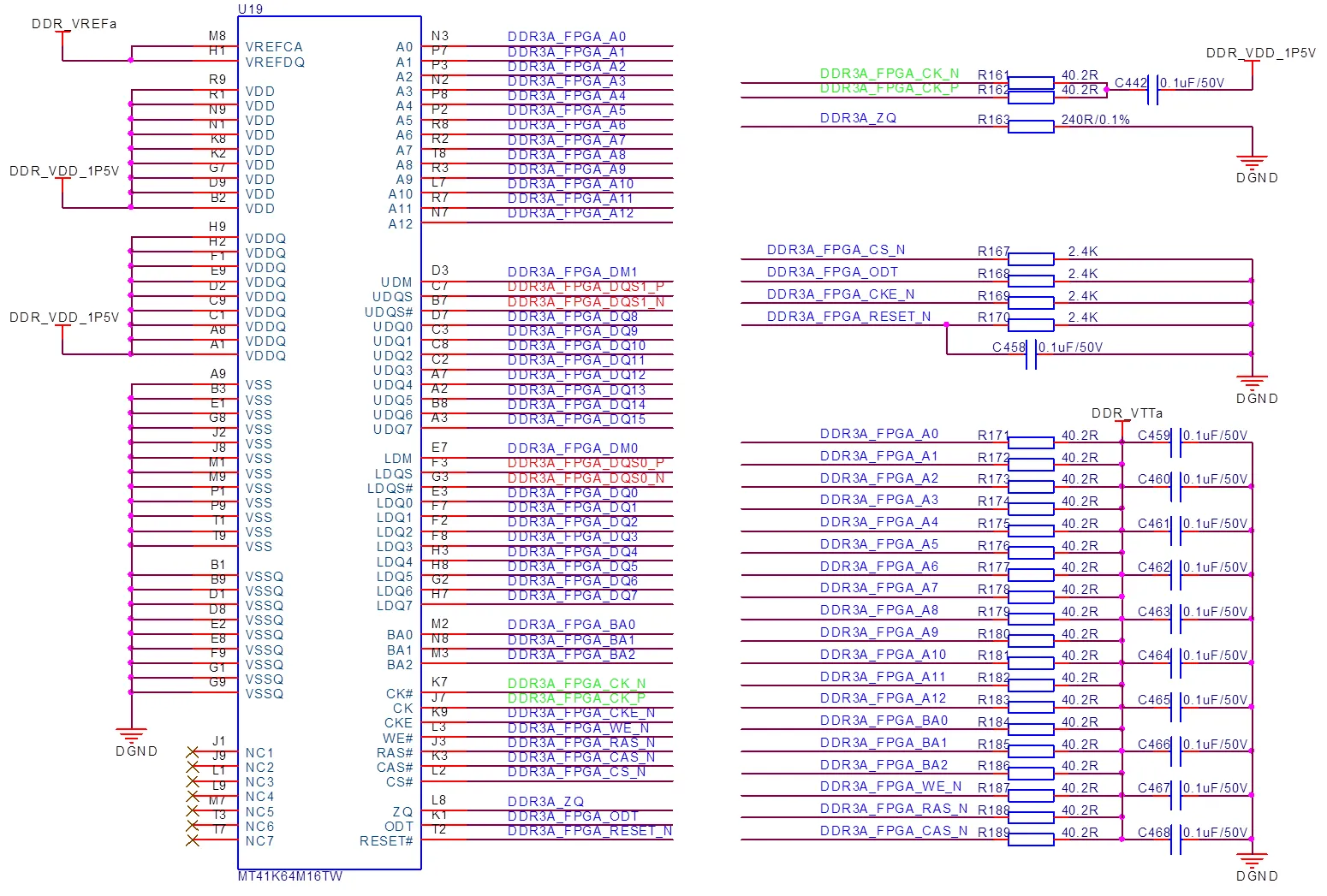

GSENSE2020输出图像数据量大,在量化位数为12bit模式下,数据率最高可达4.8Gbps,因此本设计选择了两颗Micron公司的MT41K64M16TW-107的DDR3 SDRAM。MT41K64M16TW-107时钟频率最高可达933MHz,容量为1GB,可以满足设计要求。

设计中两颗DDR3的数据线、地址线以及控制线与FPGA之间的连接均采用了独立连接设计,互不干扰,既可以满足不同数据率下的图像缓存处理,又可以实现高速乒乓操作。图4是单颗MT41K64M16TW-107的电路设计原理图,其中地址线和控制线均通过特定阻值的上拉电阻上拉到VTT电压,可以保证信号的质量,同时对时钟线设计了T形端接上拉并加入了隔直电容,可以能保证端接共模信号,同时使直流泄露最小,从而改善时钟波形。图像传感器输出的高速数据流,经过FPGA同时对两颗DDR3进行一读一写的操作实现缓存与处理。该电路实现了高速图像数据的缓存与处理,提高了数据吞吐量及系统性能。

Fig.3 PMIC partial design circuit diagram

图4 MT41K64M16TW设计电路

2.4 eMMC电路设计

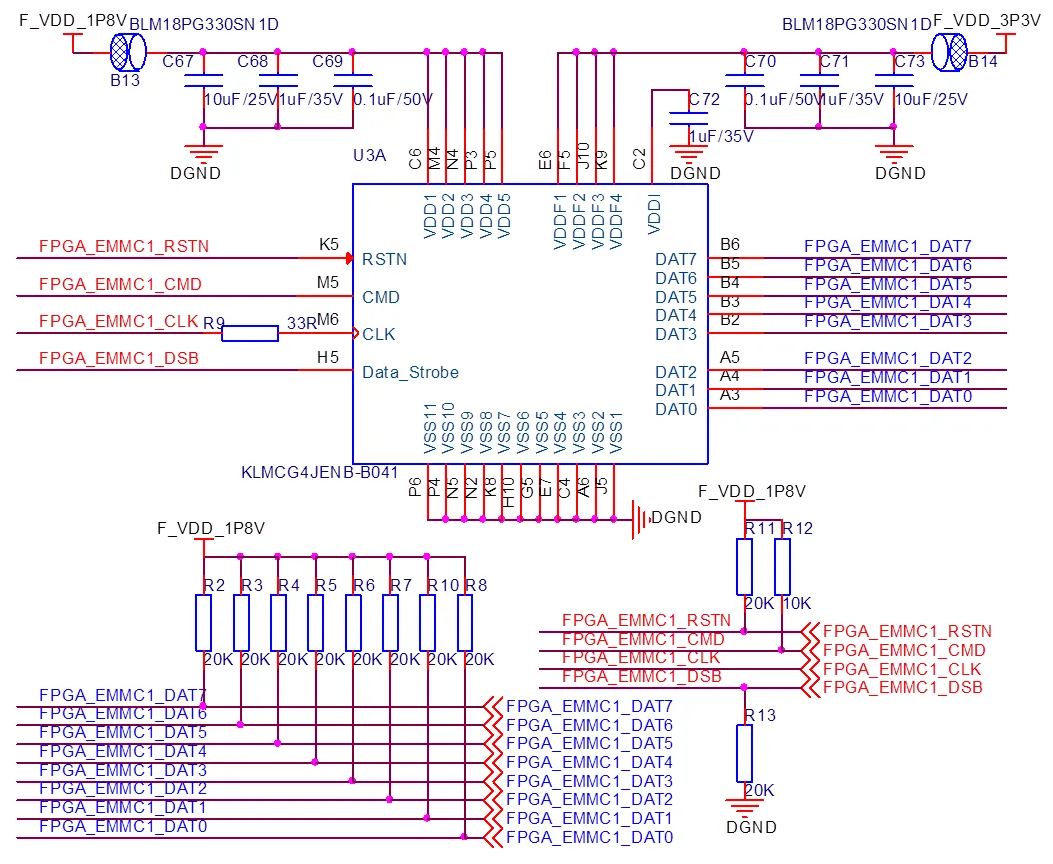

当微光探测成像系统装星之后,图像传感器获得的图像数据经过图像处理后,需要进行存储和延迟下传显示。因此本设计选用了4颗三星公司的eMMC芯片KLMCG4JENB-B041实现图像数据存储,阵列总存储容量高达256GB。该eMMC集成了控制器和快闪存储器,接口简单,工作速度快,最高时钟频率可达200MHz,可以满足图像传感器的高速存储、大容量的性能要求。

4颗eMMC与FPGA之间的连接,其中命令线CMD和数据线DAT0-DAT7是独立连接的,互不干扰,而时钟线CLK、电源线VCC、VCCQ以及地线VSS、VSSQ是共享的,可以实现4颗eMMC时钟同步和独立控制。在设计eMMC的电路时,在命令线和数据线与FPGA连接时,将其通过上拉电阻进行上拉,既可以提高芯片引脚的输出电平,也可以保证在上电配置过程中,芯片引脚为定态,还可以加大输出引脚的驱动能力。单颗KLMCG4JENB-B041的电路原理图设计如图5所示。由于该eMMC最高时钟频率可达200MHz,因此33W的串联端接电阻既可以保证阻抗匹配,又可以减少干扰,从而改善时钟信号波形。

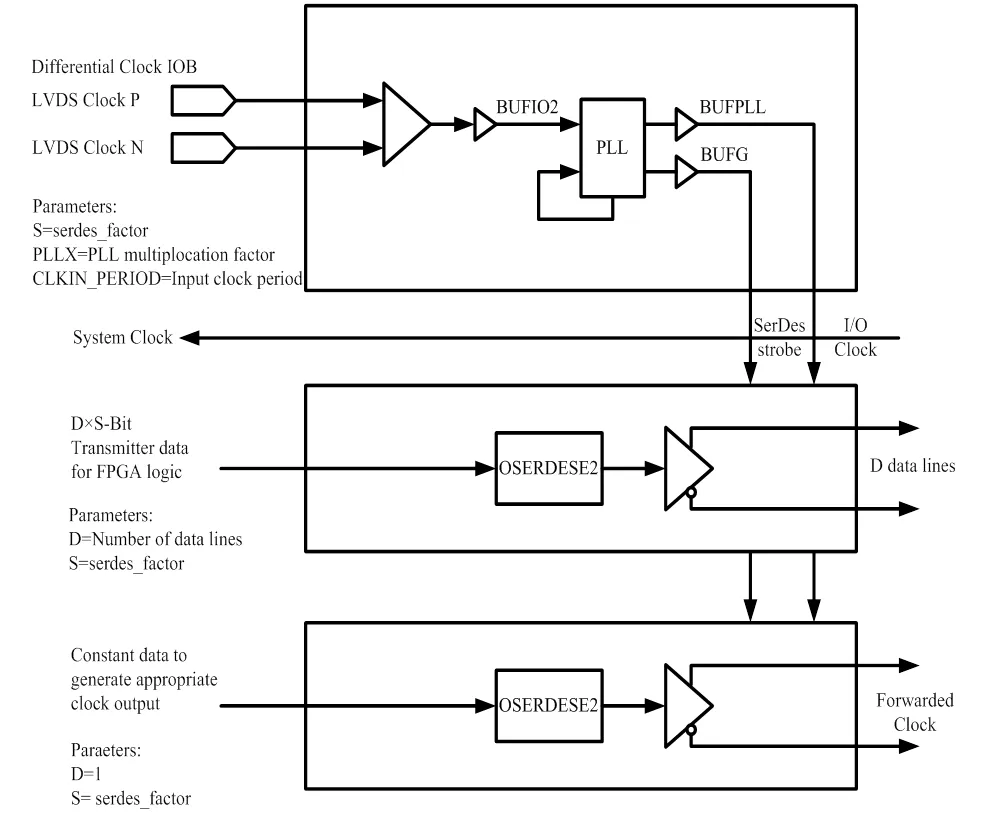

2.5 CameraLink电路设计

地面测试验证微光成像系统图像质量,采用了CameraLink接口作为图像数据的传输接口,通过CameraLink接口将图像数据传输到地面测试PC上位机进行显示。传统的CameraLink接口的数据发送和接收,均采用专用的串并转换芯片与成像系统进行数据传输,但是串并转换芯片占用体积大且其并行信号线会占用大量PCB布局布线资源,而且最高传输速率有限。Xilinx公司的K7系列FPGA内部集成了大量的IP核及原语如串并转换模块,可以实现CameraLink接口的低成本、小体积、更高速率、更稳定、无误码的传输并显示。

图5 KLMCG4JENB-B041设计电路

本设计基于CameraLink接口的Base模式实现微光成像系统的串行图像数据的传输。Base模式数据具有28位,包括1位帧有效位信号、1位行有效位信号、1位数据有效位信号、24位数据信号和保留信号,如表1所示[11]。根据Base结构分析,在本系统电路输出端选用了MDR26连接器构建CameraLink接口,利用FPGA的并串转换原语模块OSERDESE2实现数据格式转换。由于K7系列FPGA的OSERDESE2支持8:1的并串转换,因此将已经经过图像处理的图像数据按照CameraLink的Base数据格式组成28位图像数据,然后分成4组,每组均以7:1方式通过一个OSERDESE2即可完成并串转换,得到4组LVDS图像信号,如图6所示。以同样的方式对图像时钟按照CameraLink时钟格式进行并串转换得到LVDS时钟信号。最终将这4组LVDS图像信号和一组LVDS时钟信号连接至CameraLink接口,以实现图像数据在CameraLink接口的直接传输。

表1 Base模式的端口分配

图6 FPFA的7:1并串转换

3 系统实验验证分析

根据上述描述,完成微光探测成像系统电路设计,对成像系统电路进行测试及成像实验,以验证系统电路的实际性能,实验结果如下。

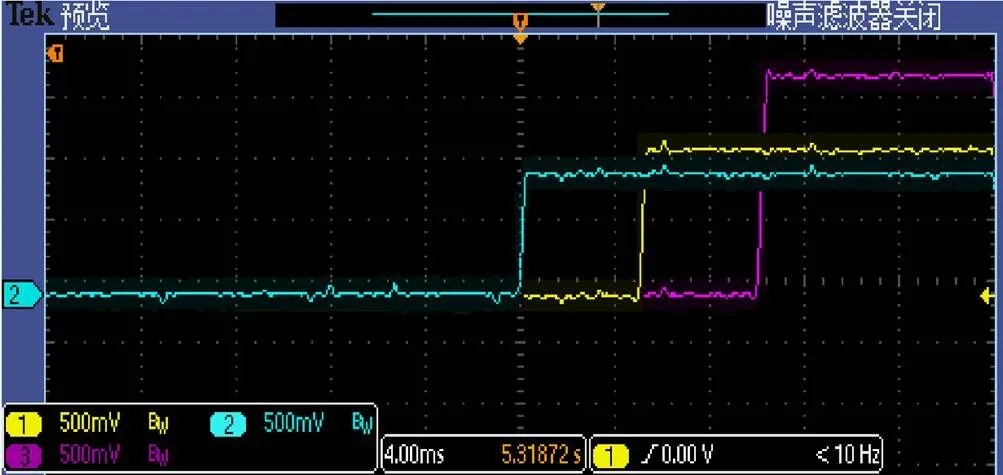

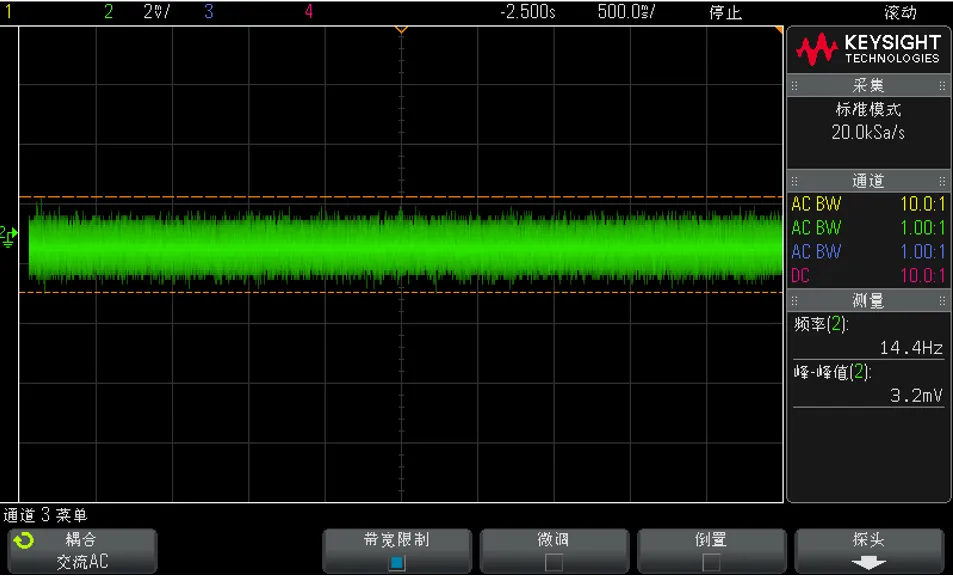

硬件电路系统实物如图7所示。首先对硬件电路进行测试调试,图8为FPGA的1.0V、1.2V、1.8V上电时序测试验证图,上电顺序及上电间隔均与设计相符。图像传感器的供电电源噪声对图像噪声质量有一定的影响,3.5V作为GSENSE2020的偏置电压、模拟电源及像素电源主要供电电压之一,其供电电压噪声直接影响图像质量,图9为3.5V的电压纹波测试结果,大小为3.2mV,这说明该电源噪声较小,可以满足低噪声设计要求。

Fig 7 System hardware circuit physical diagram

图8 上电时序图

Fig 8 Power-on sequence diagram

图9 电源纹波

GSENSE2020在量化位数为12bit模式下,图像数据只通过8个通道输出,为了保证这些数据高速输出,其输入时钟需要一个高频率时钟。当输入时钟设置为典型值600MHz时,其输出频率理论上可达300MHz,利用Vivado的ILA(在线逻辑分析仪)对其速率进行实时监测。实测结果表明,其单通道速率可达500Mb(ddr),因此数据率约为:

500×8=4Gbps (1)

由于受电路的布局布线的影响,且测试过程中图像传感器电路板和控制电路板之间的时钟线及数据线是通过普通的软排线连接,因此传感器的实测数据率会略低于理论值。

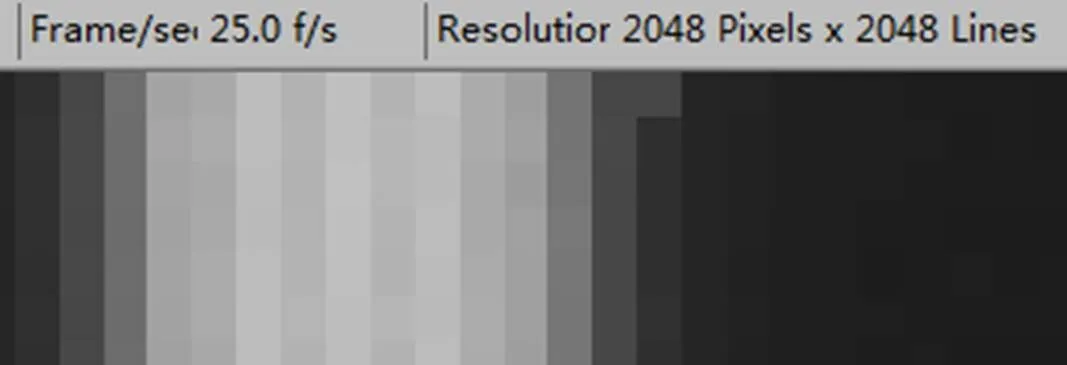

为测试验证整个成像系统的实际成像性能,在完成硬件系统电路调试后进行光机结构装调,然后对景物进行实际成像,通过CameraLink接口传输到PC图像采集上位机进行实时显示。由于上位机的CameraLink接收接口显示速率受限,因此配置图像传感器的输入时钟为375MHz,通过ILA测得实际单通道速率约为300Mb(ddr)。因此系统电路数据率可达:

300×8=2.4Gbps (2)

与此同时根据公式(3)(4)(5)可计算得出理论的帧频为27.2fps。在实验过程中上位机实际显示图像帧频为25fps,如图10所示,接近理论值。

图10 图像帧频

clk_seq=clk_INTER/12 (3)

line=560×clk_seq(4)

frame=×line(5)

式中:clk_INTER等于输入时钟频率;为输出的行数,≤2048rows。

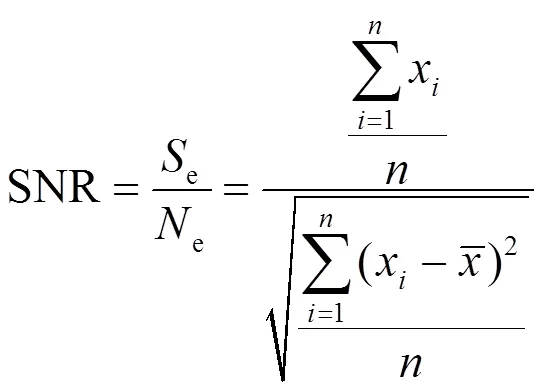

为了测试成像系统的信噪比,固定设置图像传感器积分时间,并设置增益为低增益,利用积分球进行辐照度,根据公式(6)[12]计算得到成像系统的信噪比为45.5dB,与理论值相近。

最终在低照度情况下,对实景进行探测成像,得到了清晰图像,如图11所示。

4 结论

本文基于微光图像传感器GSENSE2020设计了成像系统电路,利用FPGA驱动控制图像传感器的输出,实现了微光探测成像。同时该成像系统电路兼顾了控制双图像传感器扩展接口,为后续多波段同时探测成像设计如可见光加红外探测奠定了技术基础。经过实验验证,该成像系统电路功能和性能良好,电源供电纹波噪声低至3.2mV,通过CameraLink接口传输图像到PC图像采集上位机进行实时显示,速率为300Mb(ddr),数据率高达2.4Gbps,帧频可达25fps,系统的信噪比为45.5dB。这说明微光探测成像系统电路性能指标与理论分析值相近,且在低照度情况下得到了清晰图像,达到了预期设计要求。

图11 实景成像

[1] 郭晖, 向世明, 田民强. 微光夜视技术发展动态评述[J]. 红外技术, 2013, 35(2): 63-68.

GUO Hui, XIANG Shiming, TIAN Minqiang. A review of the development of low-light night vision technology[J]., 2013, 35(2): 63-68.

[2] 李德仁, 李熙. 夜光遥感技术在评估经济社会发展中的应用[J]. 宏观质量研究, 2015, 3(4): 1-8.

LI D, LI X. Application of night-time light remote sensing in evaluating of socioeconomic development [J]., 2015, 3(4): 1-8.

[3] 李翔. 基于夜光遥感数据的中国2005-2015年居民收入时空变化与驱动力研究[D]. 南京: 南京大学, 2018.

LI X. Study on Spatiotemporal Change and Driving Force of Resident Income of China from 2005 to 2015 Based on Night Light Remote Sensing Data [D]. Nanjing: Nanjing University, 2018.

[4] 李立金, 李浩洋, 徐彭梅, 等. 晨昏轨道微光相机成像策略研究及仿真验证[J]. 航天返回与遥感, 2017, 38(5): 29-34.

LI Lijin, LI Haoyang, XU Pengmei, et al. Simulation and verification of imaging strategy for low-light-level camera on dawn-dusk orbit[J]., 2017, 38(5): 29-34.

[5] 李贝贝, 韩冰, 田甜, 等. 吉林一号视频卫星应用现状与未来发展[J]. 卫星应用, 2018(3): 23-27.

LI Beibei, HAN Bing, TIAN Tian, et al. Application status and future development of JL-1 video satellite[J]., 2018(3): 23-27.

[6] 郭晗. 珞珈一号科学试验卫星[J]. 卫星应用, 2018(7): 70.

GUO Han. LJ-1 scientific test satellite[J]., 2018(7): 70.

[7] 祝庆贺, 熊文卓, 贺小军. 基于FPGA的星载成像系统设计[J]. 现代电子技术, 2017, 40(15): 64-67.

ZHU Qinghe, XIONG Wenzhuo, HE Xiaojun. Design of satellite⁃borne imaging system based on FPGA[J]., 2017, 40(15): 64-67.

[8] 梁超, 马天翔. 基于FPGA的CMOS成像电路设计[J]. 国外电子测量技术, 2016, 35(4): 71-76.

LIANG Chao, MA Tianxiang. Design of CMOS imaging circuit based on FPGA[J]., 2016, 35(4): 71-76.

[9] 郑扬帆, 尹达一, 李清灵, 等. 基于低噪声CMOS图像传感器的成像电路设计与实现[J]. 电子设计工程, 2018, 26(4): 188-193.

ZHENG Yangfan, YIN Dayi, LI Qingling, et al. The design and implementation of imaging circuit based on low⁃noise CMOS image sensor[J]., 2018, 26(4): 188-193.

[10] 单彦虎, 张晋顼, 任勇峰, 等. 基于FPGA的CameraLink图像数据接口设计[J]. 仪表技术与传感器, 2020(9): 51-54.

SHAN Yanhu, ZHANG Jinxu, REN Yongfeng, et al. Design of CamereLink image data interface based on FPGA[J]., 2020(9): 51-54.

[11] 隋延林, 何斌, 张立国, 等. 基于FPGA的超高速CameraLink图像传输[J]. 吉林大学学报: 工学版, 2017, 47(5): 1634-1643.

SUI Yanlin, HE Bin, ZHANG Liguo, et al. Ultra-high speed CamereLink image transmission based on FPGA[J]., 2017, 47(5): 1634-1643.

[12] 宁永慧, 刘辉, 赵庆磊, 等. 大面阵高帧频CMOS成像电子学系统设计[J]. 光学精密工程, 2019, 27(5): 1167-1177.

NING Yonghui, LIU Hui, ZHAO Qinglei, et al. High-frame frequency imaging system of large area CMOS image sensor[J]., 2019, 27(5): 1167-1177.

Design and Development of a Low-Light Detection Imaging System Circuit

JIANG Ting,CHEN Weinan,XIA Zhentao,HU Jibao,JIANG Shouwang,SUN Yongxue,LI Taiping,XIE Yongquan

(,200240,)

To achieve low-light detection in low-light remote sensing satellites, an imaging circuit is designed based on a low-light complementary metal oxide semiconductor image sensor named GSENSE2020. The imaging circuit facilitates the drive control of the image sensor and the reception and transmission of high-speed image data through a field programmable gate array (FPGA), provides low-noise power supply for the image sensor through DC/DC and low-dropout regulator, and uses a power management integrated circuit to solve the problem of FPGA power-on timing. The circuit also uses DDR3 to perform high-speed image caching and processing and adopts an embedded multimedia card to meet the requirements of image data storage rate and capacity. The intellectual property core and primitives of the FPGA are used instead of a CameraLink interface conversion chip to establish the CameraLink communication protocol. Thus, the circuit can directly transmit image data with high speed to the CarameLink interface. The experimental results show that the circuit’s functions and the performance of the imaging system reach the expected design goals. The output data rate of the system reaches 2.4Gbps, frame rate reaches 25 fps, and signal-to-noise ratio reaches 45.5dB.

low-light detection, COMS image sensor, LDO, PMIC, DDR3, eMMC, CameraLink

TN215

A

1001-8891(2022)10-1045-07

2021-03-10;

2021-04-01.

姜婷(1989-),女,江西上饶人,硕士,主要从事光电成像系统电子学技术方面的研究。E-mail:jiangting_sitp@163.com。