三模冗余对SRAM型FPGA寄存器上电状态的影响分析

2022-10-25马小霞贾露娟

马小霞,李 园,贾露娟,郭 睿

(兰州空间技术物理研究所,兰州 730000)

0 引言

现场可编辑门阵列(field-programmable gate array,FPGA)是当今数字系统设计的主要硬件平台,而Xilinx公司是最早也是最大的FPGA生产商,其芯片设计技术、开发软件和相关解决方案在业界拥有广泛的客户群[1]。其研制的SRAM型FPGA由于具有低成本、良好的重配置和较短的开发周期等特点,在航空航天嵌入式领域取得了广泛应用[2]。尤其侧重于高性能应用,性能满足各类高端应用的Virtex系列FPGA。

由于SRAM型FPGA在高辐射环境中极易受单粒子翻转(single event upset,SEU)的影响,造成FPGA逻辑错误和功能中断[3-5],因此在空间应用时必须对其采取加固措施。目前,使用最广泛的加固技术是配置刷新加三模冗余。三模冗余技术通过对3个相同的电路进行集成,然后对其运算结果进行表决[6],保证即使其中有一个电路出现错误也不会影响结果的正确性。

TMRTool 9.2i是Xilinx公司与桑迪亚国家实验室合作,针对Virtex系列FPGA专门设计的一款三模冗余实现工具,仅需要简单的设置,便可实现软件模块自动三模。根据TMRTool开发流程,工具修改综合后网表信息,修正后的网表文件作为输入再进行布局布线,最终实现FPGA软件。本文主要分析TMRTool对Virtex-II FPGA XQR2V3000网表文件的修正过程及修正前后软件布局布线结果差异,旨在了解三模冗余工具的处理机理,在电路设计和TMRTool使用时进行正确处理,防止软件经三模冗余处理后工作异常。

1 三模冗余处理

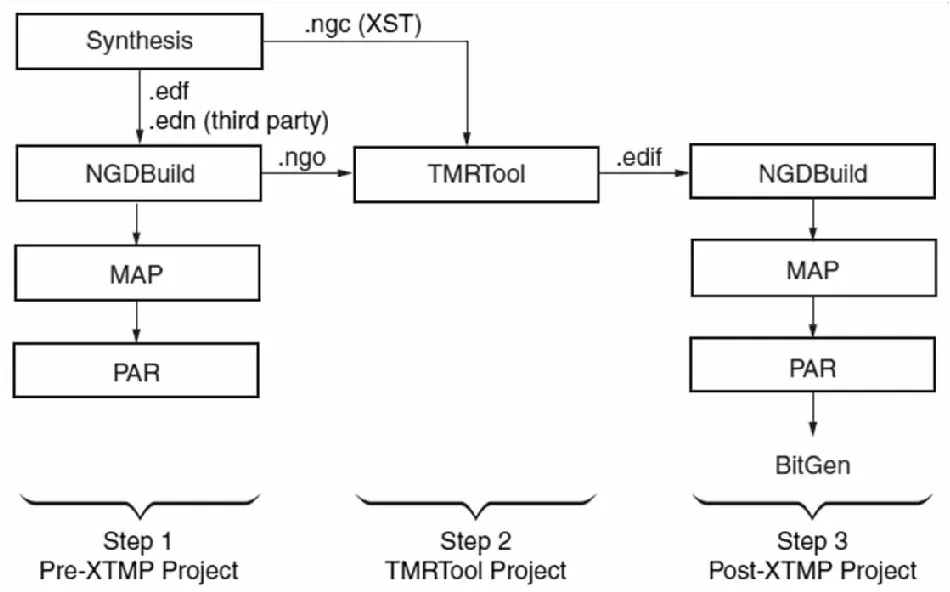

TMRTool开发流程如图1所示,其中Step2是影响软件三模冗余前后布局布线结果的重要步骤。

图1 TMRTool 开发流程[7]Fig.1 TMRTool development flow

TMRTool开发流程分为4步:

第1步:导入综合后的.ngc/.ngo网表文件。导入文件层次结构与设计层次一致。

第2步:编辑三模冗余类型和实现属性。综合工具将可综合的VHDL文件或Verilog文件编译成由与门、或门、非门、RAM、寄存器等基本逻辑单元组成的逻辑连接网表,以这些基本逻辑单元或基本逻辑单元的组合为模块按照三模冗余要求设置部件为相应的类型。每个部件可选择Don’t touch、Coverage、Standard、Custom四种类型。同时,工具支持选择XTMR实现属性。

第3步:实现三模冗余。工具按照属性设置和三模类型实现自动三模。

第4步:输出实现文件。

在未设置属性时,TMRTool工具按照默认属性设置实现三模冗余,但不同的处理属性设置导致TMRTool对网表信息的修正结果不同,以此为输入的布局布线结果不同。

实现XTMR属性包括可选择的处理步骤和处理设置。处理设置包括设计类型Design Type设置、Vcc/Gnd信号获得方式Power Source设置,默认三模输出类型Default Output XTMR Type以及是否移除移位寄存器,本文不做具体含义解释,重点介绍处理步骤含义。

处理步骤具体包括以下5步,实现三模冗余时,TMRTool根据是否勾选依次进行各步处理,默认TMRTool全部勾选。

1.1 替换寄存器

针对Virtex-II FPGA,ISE库提供了多种类型的寄存器组件,如FD_1、FDC、FDP等,但布局布线时,所有的寄存器组件均映射到配置逻辑(CLB/Slice)寄存器,CLB只有一种类型的寄存器。

该步操作使寄存器未使用的输入端口被绑定到FPGA内部半锁结构电路上,使其具有确定的逻辑连接。

1.2 提取Vcc/Gnd

半锁结构电路不占用布线资源但其对SEU敏感且无法用配置回读的方式进行检测[8-9],因此在空间应用时需移除该结构。TMRTool修改网表文件使寄存器未使用的输入端口连接至可靠的逻辑电平Vcc/Gnd上代替半锁结构。

Vcc/Gnd的获得方式有3种,具体如下:

1)连接至逻辑1的引脚;

2)连接至逻辑0的引脚;

3)内部结构获得。所有Xilinx产品均设计了Vcc/Gnd[8]。

通过寄存器替换和Vcc/Gnd提取操作,TMRTool移除了半锁结构,同时使得寄存器未使用端口连接至确定的逻辑电平Vcc/Gnd。

1.3 唯一化部件名称

该步操作的作用是重命名设计部件名称使得设计中所有的部件名称唯一化,防止因部件名称重复引起三模冗余操作异常。

1.4 三模冗余

经1.1-1.3步预处理后,网表文件具备了三模冗余的状态,TMRTool将按照指定的三模冗余类型和XTMR属性实现设计三模冗余。除部件三模冗余类型被设为Don’t touch的情况外,设计中部件被复制3份,同时插入表决器和反馈逻辑,以表决器输出作为部件的最终输出。

1.5 移除多余结构

经三模冗余后,设计中增加了一些空的结构,该结构可能在布局布线时引起异常。经该步处理,设计中多余的结构将被移除。

综上,根据TMRTool开发流程、XTMR属性设置和三模类型,TMRTool修改了网表信息,以TMRTool输出的EDIF文件作为输入进行布局布线,最终实现具备三模冗余容错的FPGA软件设计。

下面在布局布线属性设置相同的情况下对比TMRTool处理前后软件的布局布线结果和最终实现结果。

2 机理分析

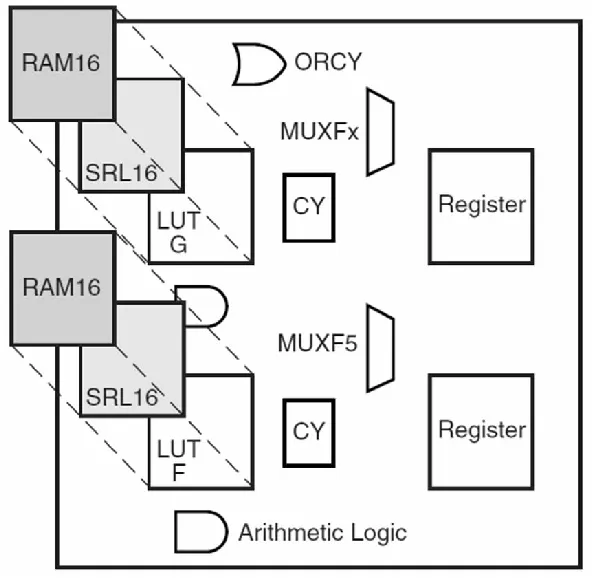

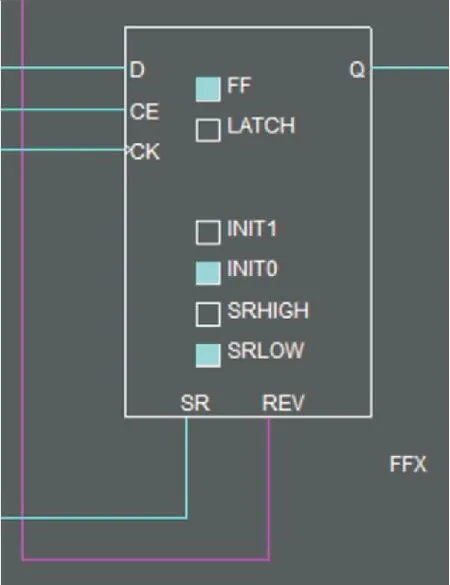

布局布线使软件映射至网表约定的FPGA器件对应位置。Virtex系列FPGA器件结构复杂,但组成结构固定。Virtex-II器件每个CLB/Slice包含两个LUT和两个寄存器[10],如图2所示。可以将其配置为分布式RAM、移位寄存器SRL、查找表LUT、触发器FF或锁存器LATCH使用。其中寄存器的接口如图3所示。

图2 Virtex-II Slice结构[11]Fig.2 Virtex-II Slice configuration

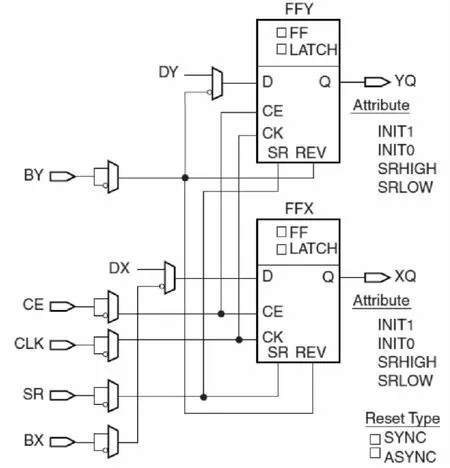

图3 Virtex-II Slice中寄存器/锁存器结构[11]Fig.3 Register / Latch configuration in a slice

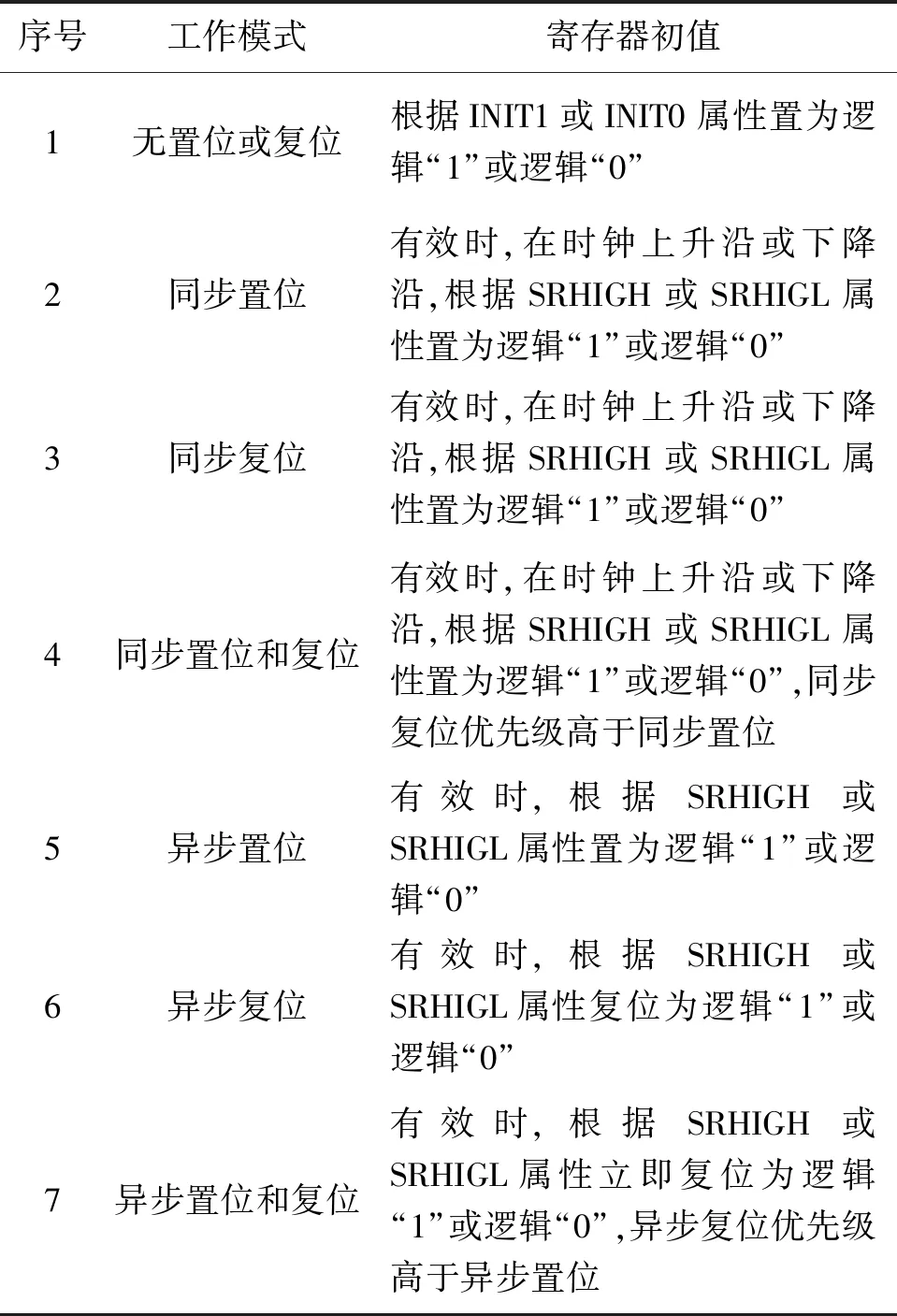

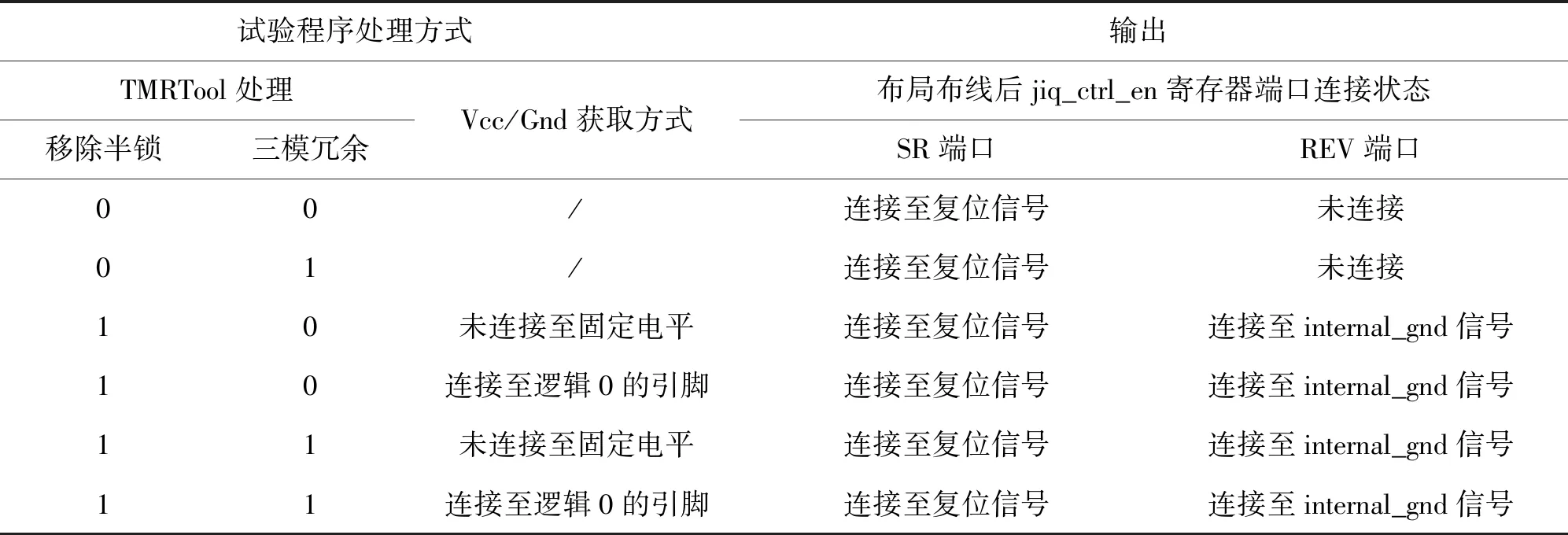

每个寄存器包括一个数据输出端口Q,一个数据输入端口D,一个时钟端口CK,一个片选端口CE,SR端和REV端均为寄存器的置位/复位端[10-11]。所有寄存器共用SR和REV。根据SR和REV连接状态及寄存器属性,每个寄存器可以被设置处于7种工作模式,如表1所列。

表1 寄存器初始状态说明Tab.1 Register initial status under different mode

1)寄存器在配置或全局初始化后的状态由INIT0和INIT1属性确定。

2)SR强制寄存器进入SRHIGH或SRLOW属性指定的状态。

3)当SR被使用时,REV强制寄存器进入相反的状态。

当CLB/Slice被配置为寄存器且软件设计了复位时,经布局布线后寄存器的连接状态发生改变,如图4和图5所示,绿色表示端口连接了信号,红色表示端口未连接信号。经TMRTool工具处理后的寄存器REV引脚至internal_gnd,该信号由逻辑电平Vcc/Gnd决定。

综上可知,TMRTool影响寄存器的初始工作状态。

图4 未经TMRTool处理时寄存器端口连接Fig.4 Register port connection status before TMRTool processing

图5 经TMRTool处理后寄存器端口连接Fig.5 Register port connection status after TMRTool processing

3 试验与验证

基于Xilinx ISE9.2.03i集成开发环境设计一个试验系统验证TMRTool对FPGA功能的影响。

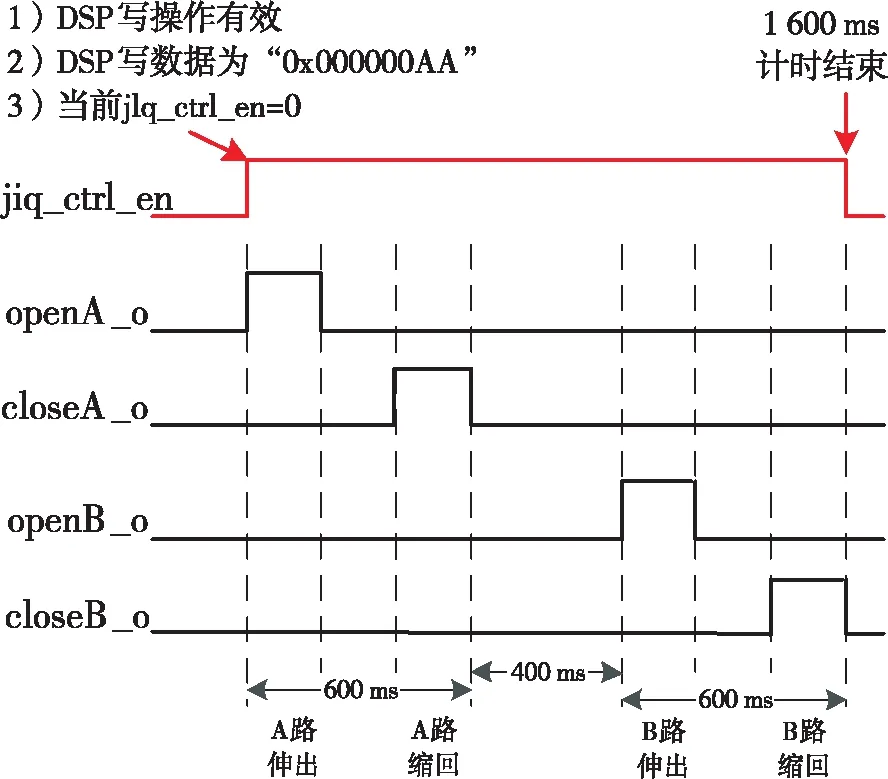

系统框架如图6所示,系统功能如下:当DSP将FPGA激励控制寄存器置为“0x000000AA”时,FPGA按图7输出脉冲,控制继电器吸合或断开,从而实现激励器伸缩杆的伸出或缩回;若DSP写其他值则FPGA不响应;若本次动作时序未执行完毕则不响应下一条继电器控制指令。在上电或复位状态下,FPGA不输出控制信号,默认输出信号为低电平,继电器不动作。FPGA复位信号由DSP给出。

图6 试验系统框架图Fig.6 Testing system diagram

使用Verilog语言实现该FPGA试验程序。如图7所示,设计中控制信号jiq_ctrl_en、计时寄存器、DSP写数据保存寄存器及其他内部寄存器初值或复位值均为0;当条件1)、条件2)和条件3)均满足时置jiq_ctrl_en为1并开始计时;当1600ms计时结束,置jiq_ctrl_en为0并清除计时,等待下次条件满足。在jiq_ctrl_en为1时,软件根据计时寄存器的值输出高脉冲,控制继电器动作。因此jiq_ctrl_en的状态变化是影响FPGA功能的关键。

图7 试验程序设计Fig.7 Testing software design

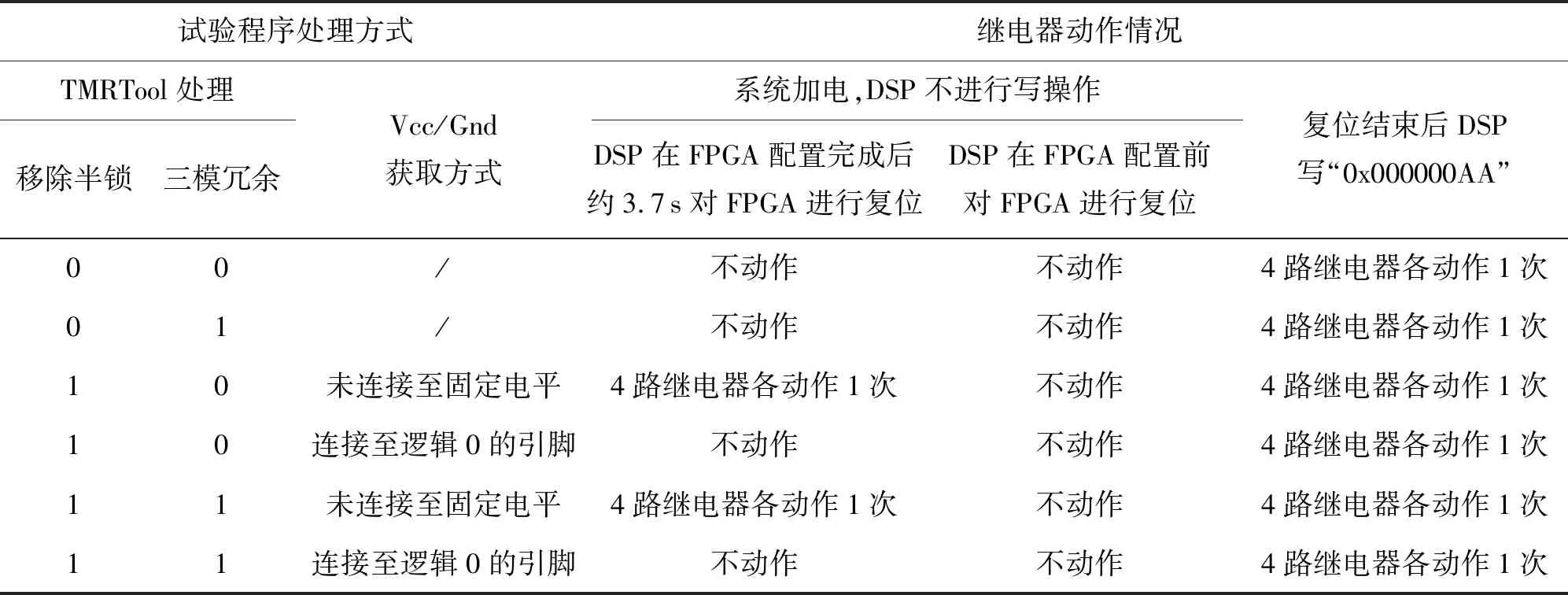

将该试验程序按图1流程进行不同的处理,查看jiq_ctrl_en寄存器的端口连接情况及继电器动作情况,详见表2和表3所列。

表2 TMRTool工具不同处理操作下寄存器端口连接状态Tab.2 Register port connection status under different TMRTool’s operations

表3 TMRTool工具不同处理操作下继电器动作情况Tab.3 Relays status under different TMRTool’s operations

从试验结果可知,经TMRTool处理后系统响应与需求不符。首先,系统加电FPGA配置完成后,若无复位,理论上系统应处于上电默认状态。在DSP未进行写操作时,继电器不动作。但实际上,在无复位信号的3.7s内,继电器发生了非预期的动作;第二,移除半锁操作改变了jiq_ctrl_en寄存器REV端口的连接状态;第三,FPGA复位时机和Vcc/Gnd引脚连接与系统上电状态有关;第四,当不三模冗余时,系统响应与需求一致。根据Virtex-II FPGA寄存器工作模式,当SR使用但无效时,REV强制寄存器进入与初值相反的状态,导致jiq_ctrl_en寄存器上电后直接输出逻辑1,时序控制计数器开始计数,进而FPGA输出控制脉冲,继而导致继电器动作,系统功能出现与需求不符的现象,说明三模冗余影响寄存器的初始工作状态。

4 结论

使用TMRTool实现FPGA软件三模冗余容错处理时,除3倍基本逻辑单元和插入表决器,工具还改变了所有寄存器未使用端口的连接状态。SR和REV作为寄存器的置位/复位端,其连接状态直接决定了寄存器的初始状态。SR和REV端口连接状态的改变,改变了软件的上电状态,导致软件进入非预期初始态,不受控制地直接输出非法时序,存在使设备异常动作的风险。

在航天领域,要求设备上电都有明确的初始状态,因此,在使用TMRTool进行三模冗余时,硬件设备必须满足工具应用需求,确保电路上有3个FPGA引脚连接至固定电平,同时TMRTool工具属性设置以及约束文件引脚绑定与电路设计一致,防止三模冗余引入上电状态异常问题。