应用于弹载SiC MOSFET 的RC吸收电路的设计与优化*

2022-10-22张晓娟景博张劼王洋李红波

张晓娟景 博张 劼王 洋李红波

(1.西京学院机械工程学院,陕西 西安 710123;2.空军工程大学航空工程学院,陕西 西安 710038)

碳化硅(SiC)和氮化镓(GaN)作为宽禁带半导体材料的代表,引发了电力电子的新一次革命。其中SiC MOSFET 由于更低的导通电阻以及更快的开关速度,正逐步取代Si IGBT,将电力电子装置的功率密度和效率提升到新的高度[1]。弹载电源中SiC MOSFET 使用广泛,但其高速开关带来的电气过应力与高频振荡不仅恶化了系统的电磁兼容特性,更危及了器件的安全工作区[2],降低了整机工作的可靠性,进而制约了SiC MOSFET 的进一步推广。

SiC MOSFET 高速开关暂态的负面效应主要源于以下两方面:一方面,SiC MOSFET 的结电容更小,开关速度更快,瞬变所带来的高di/dt、du/dt会成为电路中电磁干扰的源头,产生诸如串扰[3]、电磁干扰(Electromagnetic Interference,EMI)[4-5]等问题;另一方面,SiC MOSFET 对于回路中的寄生参数更加敏感,di/dt会与寄生电感相作用产生超调电压,du/dt会与寄生电容相作用产生漏电流,寄生电感和寄生电容在SiC MOSFET 近似阶跃输入的激励下又会产生衰减振荡,进一步加剧电磁干扰。

降低回路寄生电感,优化布线结构[6]被证明是一种有效的方法,但是依赖于设计者的经验,并且进一步降低寄生电感需要复杂的封装技术[7],成本较高。增设缓冲吸收电路是目前应用最广、成本最低的方法。该方法通过在MOSFET 两端并联无源器件,对于谐振网络进行阻尼以及能量吸收。文献[8]讨论了目前常用的三种吸收电路拓扑,并进行了横向对比;文献[9]给出了RCD 吸收电路的具体设计方案,实验证明该电路可以有效抑制MOSFET关断电压尖峰。目前,针对弹载设备中高速SiC MOSFET 的吸收电路设计方案鲜有报道,传统应用于Si 基器件的设计方法存在一定的局限性。

本文首先分析了SiC MOSFET 的开关特性,并分析了SiC MOSFET 的四种无源吸收电路优缺点。其次,针对其中应用较为广泛的RC 吸收电路进行建模分析,给出相关参数的具体设计及优化方案。最后,通过400V/20A 双脉冲测试电路进行了实验验证。

1 SiC MOSFET 的开关特性

图1 为应用于SiC MOSFET 开关特性分析的双脉冲测试电路。其中,Lload为负载电感,VBUS为恒定母线电压,Df和Cf表示续流二极管及其结电容,Cgs、Cgd、Cds表示SiC MOSFET 结电容,Lloop为桥臂走线寄生电感,Rg为栅源驱动电阻,Vdr为驱动电压。

图1 SiC MOSFET 双脉冲测试电路图

图2 为SiC MOSFET 开关暂态的典型波形,其中包括指令信号usignal、栅源两端电压ugs,漏源电压uds,漏极电流id。双脉冲测试电路的具体实验方法参照文献[10]。双脉冲测试电路模拟了SiC MOSFET 在感性负载下开关的的工作状态,其中续流二极管Df可以是BOOST 或无桥PFC 电路中常用的SiC SBD 肖特基二极管,也可以是SiC MOSFET工作在同步整流模式下的体二极管。

图2 SiC MOSFET 开关典型波形图

在开通过程中,由于反向恢复效应,漏极电流id存在超调,同时Cf与Lloop形成LC 谐振,导致了漏极电流的衰减振荡;在关断过程中较大的di/dt与Lloop相作用导致电压超调,此时SiC MOSFET 的输出电容Coss=Cgd+Cds与Lloop作用,形成漏源电压的衰减振荡。其中,电压uds的超调与振荡是实际工程中导致MOSFET 失效的主要原因,也是本文研究的重点。

关断电压的超调振荡随着SiC MOSFET 开关速度的提升会愈加显著,如图3(a)所示。增大栅极电阻可以对关断电压尖峰进行抑制,但是是以延时和损耗增加为代价的。图3(b)展示了关断电压随回路电感的变化趋势,显然降低寄生电感有利于降低uds的超调与振荡,但是目前对于寄生电感的主动控制还处于研究阶段。

图3 开关速度和寄生参数对关断电压尖峰的影响

2 现有无源吸收电路

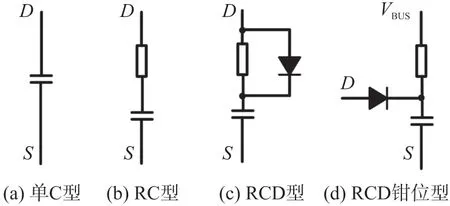

无源吸收电路主要有四种拓扑形式,如图4 所示。每一种吸收电路都并联在SiC MOSFET 的漏源极两端,以达到吸收关断电压尖峰的目的。

图4 常用无源吸收电路

单电容C 吸收电路如图4(a)所示。该电路增大了谐振回路的电容数值,进而削弱了关断电压尖峰,降低了振荡频率。但该吸收电路不存在耗能元件,在开通阶段SiC MOSFET 的电流应力较大。

RC 吸收电路如图4(b)所示。电阻的加入增大了谐振回路的阻尼,抑制电压尖峰,但同时也承担了一部分的功率损耗。这种方法可以缓解SiC MOSFET 开通时的电流应力,但同样削弱了关断电压尖峰的抑制能力,RC 的数值需要进行优化选取。

RCD 吸收电路如图4(c)所示。该电路在RC的基础上增加了一个二极管,在关断阶段等效于单电容C 电路,而在开通阶段等效于RC 电路。RCD电路虽兼顾了关断电压吸收和开通电流应力两个问题,但额外增加一个快恢复二极管或者肖特基二极管以保证电路的有序工作,这无疑大大增加了成本。

RCD 钳位吸收电路是RCD 的改进,只在SiC MOSFET 关断电压超调振荡阶段才会工作,将吸收电路对于功率管开关特性的影响降到最低,比传统RCD 电路的效率更高[11]。然而该电路同样需要额外的二极管,成本方面不具备优势。

本文选取常用的RC 吸收电路,对其进行建模分析,并给出缓冲电阻和电容的参数设计与优化方案。

3 RC 吸收电路的设计与优化

应用于SiC MOSFET 的RC 吸收电路如图5(a)所示,其等效电路如图5(b)所示。显然,RC 吸收电路的加入构成了一个二阶有阻尼振荡电路。在Pspice 中取母线电压VBUS=400 V,负载电流IL=20 A,驱动电阻Rg=10 Ω,回路寄生电感Lloop=100 nH,采用CREE 公司的1 200 V/90 A 的C2M0015120D 模型,进行仿真分析。

图5 RC 吸收电路及其等效电路图

3.1 RC 电路对于关断性能的优化

图6(a)为SiC MOSFET 关断电压尖峰的抑制效果。取Rs=10 Ω,Cs=2.2 nF,关断电压的峰值有了58 V 的下降,同时振荡频率由27.2 MHz 降到13.4 Hz,并且衰减速度加快。图6(b)为SiC MOSFET关断电压的频谱,显然在27.2 MHz 处有了10 dB/μV的衰减,这大大优化了系统共模EMI 特性。

图6 RC 吸收电路对关断电压的优化

3.2 RC 参数对于抑制效果的影响

如图6(a)所示,SiC MOSFET 的关断电压uds为有阻尼衰减的阶跃响应。根据图5(b)给出的LC 谐振回路等效图,可以得出加入RC 吸收电路后,系统的振荡频率fosc为

该电路的阻尼系数ζ可表示为

式中:Rd为等效阻尼电阻。

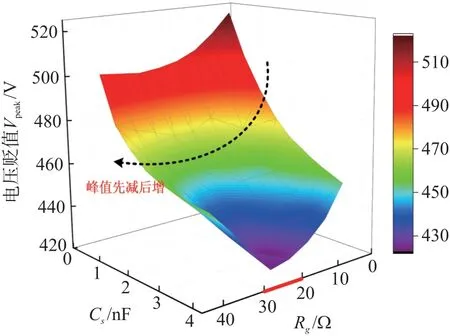

取ζ=1 的临界阻尼情况,可以得到此时等效阻尼电阻为

缓冲电阻Rs的取值范围即以Rd作为基准进行标定。缓冲电容Cs的取值范围则以SiC MOSFET的输出电容Coss作为基准进行标定。本例中Rd≈10 Ω,Coss=220 pF。

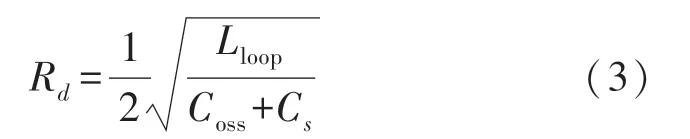

图7 给出了固定Cs=2.2 nF,选取Rs从5 Ω 到40 Ω 条件下,关断电压的波形图。值得一提的是随着Rs的进一步增大,系统阻尼不降反升。

图7 缓冲电阻对于关断电压尖峰的影响

同样的情况出现在Cs取值过大时,随着缓冲电容的增大,关断尖峰上升,如图8(b)所示。这是由于图5(b)的二阶等效电路图忽略了双脉冲系统中其他寄生参数,实际上应用RC 吸收电路的SiC MOSFET 驱动系统为一个高阶系统,存在多个极点,缓冲电阻和缓冲电容取值过大都会导致超调变化趋势的改变。在实际应用中,我们为保证RC 吸收电路设计的有效性,有如下约束

图8 缓冲电容对于关断电压尖峰的影响

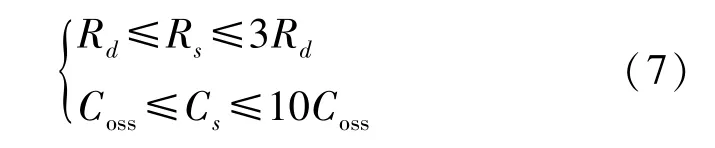

选取缓冲电阻Rs=5 Ω~40 Ω,缓冲电容510 pF-3.9 nF,可得到关断电压峰值的变化趋势,如图9 所示。显然,随着缓冲电容取值的增大,电压峰值降低,但衰减趋势随电容值上升而放缓。同时,随着缓冲电阻取值的增大,电压峰值呈现先减后增的趋势,并在20 Ω~30 Ω 区域内取到电压尖峰的最小值。所以,一味增大缓冲电阻取值对于降低电压峰值无效;一味增大缓冲电容取值对于降低电压峰值效果不显著,甚至会出现反向趋势。增大电容对于电压峰值的抑制效果要优于增大电阻。仅从削弱电压尖峰的角度来看,应固定Rs数值,并在10 nF 以内增大Cs。

图9 关断电压尖峰的变化趋势

3.3 RC 参数对于损耗的影响

除了对关断电压尖峰的抑制效果,系统的损耗也是衡量RC 吸收电路参数设计优劣的标准之一。对于电力电子装置,损耗的增加意味着效率的下降以及散热负担的加重,进而会降低系统的功率密度。对于应用于SiC MOSFET 的RC 吸收电路系统而言,主要关注SiC MOSFET 本身以及耗能缓冲电阻Rs上的功率损耗。

SiC MOSFET 的开关损耗可表示为其漏源电压uds与漏极电流id的积分

缓冲电阻上的损耗可表示为

式中:tu表示uds的边沿变化时间。

图10(a)和(b)分别给出了不同R、C取值条件下SiC MOSFET 开关损耗与Rs热损耗的变化趋势。不难看出,和缓冲电阻的损耗相比,SiC MOSFET 的损耗变化的幅度相对较小。对于SiC MOSFET 的开关损耗,其随着缓冲电阻的增大而减小,这是得益于超调损耗的降低;其又随着缓冲电容的增大而增大,这是因为RC 吸收电路的插入一定程度上降低了SiC MOSFET 的开关速度。对于Rs的热损耗,其随着自身电阻值的增大而增大,增大速度逐步放缓,体现了公式(6)中二次项的变化趋势;另外,热损耗同样随着缓冲电容的增大而增大。

图10 系统部件损耗的变化趋势

总损耗是系统效率的集中体现,其变化趋势和缓冲电阻热损耗类似,如图11 所示。

图11 总损耗的变化趋势

在确定Rs取值后,可根据对于电压超调量和总开关损耗的要求,对Cs进行折中取值。显然,一味增大R、C取值对于提升系统效率是不利的。于是,在公式(4)的基础上对于RC 取值有进一步约束

实际设计过程中,未插入RC吸收电路下可测得uds的响应波形,得出临界阻尼电阻Rd的数值;其次,在公式(7)约束条件下选择合适的缓冲电阻和缓冲电容;最后根据应用场合对于R、C数值进行微调。对于EMC 要求严格或者寄生参数较为恶劣的场合,建议适当选取较大的Cs值以达到尖峰与振荡足够的衰减;对于效率要求严格的场合,在保证尖峰不超过额定电压的情况下,尽量选择较小的Cs值。不建议将增大Rs值作为优化设计的方式。

4 实验验证

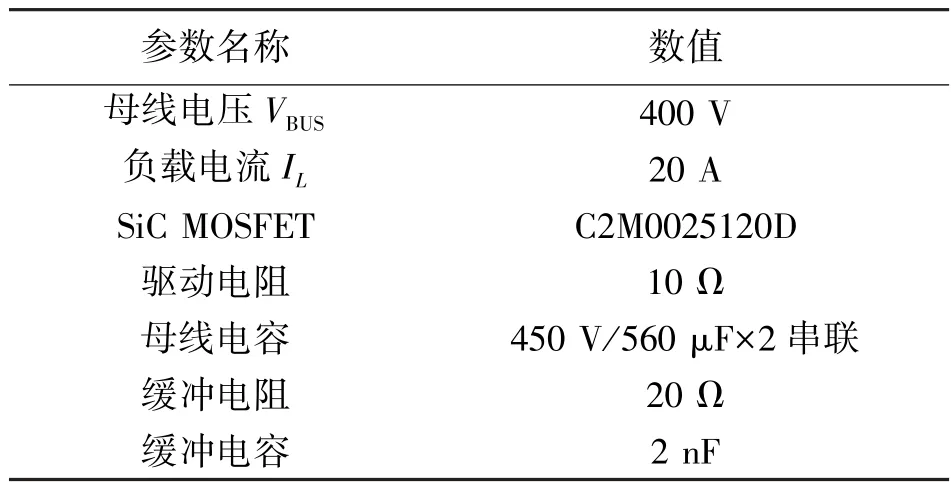

为验证本文提出的R、C参数优化设计方法的有效性,搭建了如图12 所示的双脉冲测试平台。实验的相关测试参数如表1 所示。

图12 实验电路

表1 双脉冲测试电路参数

图13 所示为加入RC 吸收电路前后SiC MOSFET 的关断暂态电压波形图。显然,RC 吸收电路的加入将超调量由330 V 降低到了180 V,有效提升了SiC MOSFET 开关暂态瞬间的可靠性。

图13 RC 吸收电路实验效果

5 结论

针对弹载电源中SiC MOSFET 关断暂态的电压超调振荡现象,首先,分析了应用于SiC MOSFET 的三种无源吸收电路的优缺点。其次,对于其中应用较为广泛的RC 吸收电路进行建模分析,给出相关参数的具体设计及优化方案,限定了缓冲电阻和电容取值的约束条件。最后,通过400V/20A 双脉冲测试电路验证了设计的有效性。