中央处理器安全测试与自修复技术研究*

2022-10-20周永忠洪晟姜义初顾爽李雷刘亮高欣妍阴宏伟岳天羽

周永忠,洪晟,姜义初,顾爽,李雷,刘亮,高欣妍,阴宏伟,岳天羽

(1.北京智芯微电子科技有限公司 数字芯片设计中心,北京 100192;2.北京航空航天大学 网络空间安全学院,北京 100191;3.北京航空航天大学 未来空天技术学院/高等理工学院,北京 100191)

0 引言

CPU(中央处理器)系统通常由板载集成电路驱动,具有微型化、标准化、通用化等一系列特点。随着工业控制对设备精密度、复杂度、安全度以及功能密度要求的日益提高,中央处理器安全技术成为工业控制芯片可靠的重要保障,因此研究其安全测试和自修复技术具有重要意义。

当前中央处理器安全测试以及测试前的故障注入成为国内外研究的重点,研究系统面对突发情况时的自修复技术有利于更好提高工控芯片的安全性。当前技术主要是致力于学科融合,应用生物等各领域的知识硬软件结合进行,但各方法都有所偏重,单独的故障处理技术无法很好地满足工业控制的安全需求。因此,有必要建立协同各方面故障处理技术的模型来指导中央处理器的安全发展方向。

本文研究中央处理器安全测试与自修复技术的整个流程,对不同技术进行优劣对比,最终提出了一种融合各个技术的安全协同模型,对中央处理器发展的趋势作出了总结与展望,得到有意义的结论。

1 中央处理器安全测试与自修复进展

1.1 基本概念及相互关系

对中央处理器系统进行安全测试,首先需要故障注入。故障注入从本质上来说属于一种模拟,是将错误或者错误效果注入目标系统,对系统进行模拟干预来造成故障,从而为后续的测试操作作为条件和准备;安全测试是监测系统在故障到来时采取的应对措施,用于得到系统对于故障的内部处理机制来评估系统的容错能力;自修复技术是指中央处理器在面对某些故障时所采取的调度替代、容错、重构、冗余等一系列自我保护机制,目的是排除故障对系统运行带来的不良影响。

1.2 实现方式及分类

1.2.1 故障注入

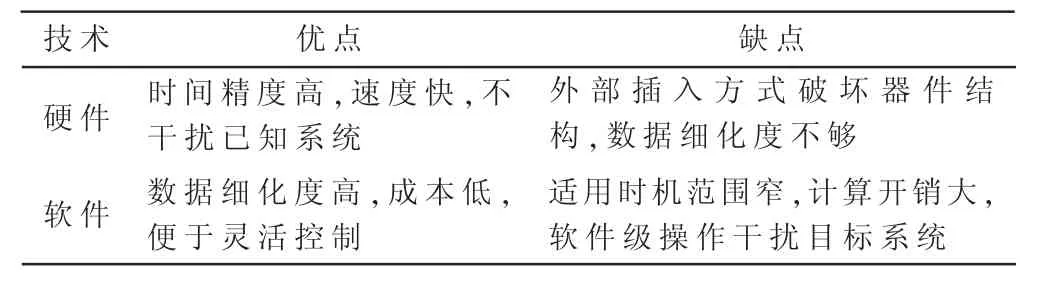

故障注入[1]技术是判断系统可靠性和识别敏感区域的必要条件[2],实际应用中,可以通过硬软件配合同时实现两者的优点[3]。优缺点对比如表1 所示。故障注入尚存在功能引脚限制导致的指示器激活缺陷,还需要在管脚上作进一步的技术突破[4]。

表1 传统硬软件注入技术优缺点对比

1.2.2 安全测试

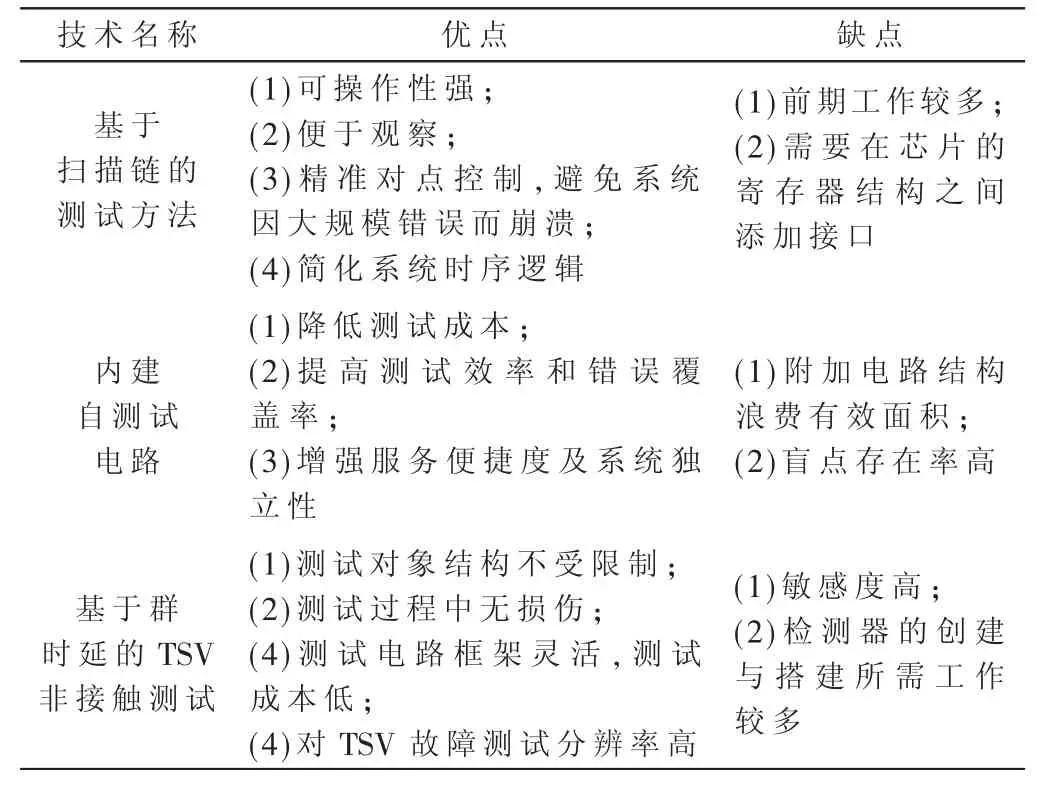

传统安全测试采用增加测试点的方法,效率低、成本高、可实现性低[5]。目前主要有基于扫描链的测试、TSV 非接触测试和内建自测试,超大规模的集成电路多实施内建自测试电路[6]。

Stratigopoulos[7]、Roy S[8]等提到利用ML(机器学习)故障测试,通过输入原始数据来训练机器处理和测量大量数据。电路时序复杂度、模拟电路的非离散性和参数缺失性带来的计算复杂性问题可以交给ML 解决;S Jayanthy[10]、Di Natale G[11]、Dalpasso[12]等提出延迟测试技术,隐藏延迟故障传感器在上升和下降的时钟边缘采集数据,还可利用纳米技术设计开关双极器件的布尔模型,可捕捉复杂器件中逻辑的瞬时切换。

1.2.3 自修复技术

传统修复技术采用可替代CLB 块(可配置逻辑模块),空间开销较大。现有方法包括替代修复技术,实时容错自修复技术、AES、ASIC、BISR、基于细胞阵列的自修复技术、电压对比成像技术、贝叶斯技术、NOC 容错机制和基于Mesh 的路由器级容错体系等。

2 安全测试体系

2.1 故障注入技术

2.1.1 硬件故障注入技术

传统的硬件注入需要附加硬件设备的帮助,安全性低,不方便试验[13]。

插入法截取输入输出信号,对高速系统时序影响大,准确度较低;探针法将探针和芯片管脚捆绑改变管脚的电流,但对BGA 封装芯片无效;JTAG 调试技术中,BSC(边界扫描寄存器单元)正常不参与运行,但调试模式下其各单元相接,分离内部芯片和外部管脚,在三种方法中占优[13]。

2.1.2 软件故障注入技术

传统软件测试需要目标系统对于实验者处于开放状态,与某些保密领域的工作要求是矛盾的[14]。Doctor集成软件开发环境[15]使主机和目标系统依托于不同结构,用定时器随机规定时间后注入错误效应;Pin 法随机插入可执行程序,随机选取内存区域或通过超时、软件陷阱、硬件异常等方法,注入错误源代码;SFIS[16]基于单粒子事件,改变原有程序,但之后代码可恢复原状。对中央处理器系统进行安全测试,首先需要故障注入。故障注入从本质上来说属于一种模拟,是将错误或者错误效果注入目标系统,对系统进行模拟干预来造成故障,从而为后续的测试操作作为条件和准备;安全测试是监测系统在故障到来时采取的应对措施,用于得到系统对于故障的内部处理机制来评估系统的容错能力;自修复技术是指中央处理器在面对某些故障时所采取的调度替代、容错、重构、冗余等一系列自我保护机制,目的是排除故障对系统运行带来的不良影响。

2.2 测试技术

2.2.1 基于扫描链的测试方法

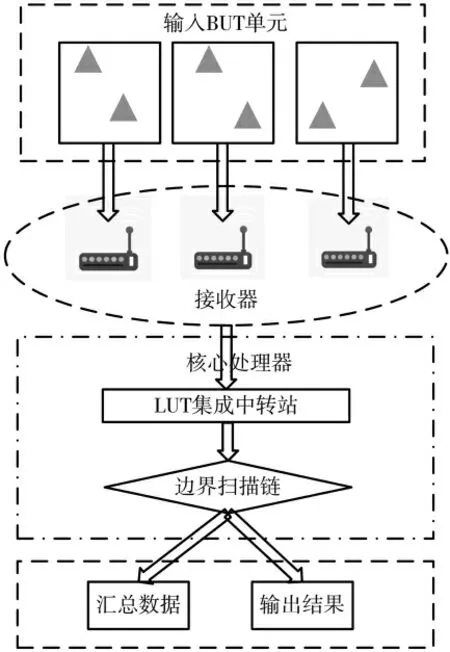

陆云云[17]等提到扫描链大体可以分为两种,一种存在于芯片内部独立化元件,另一种存在于芯片的I/O 端口显示板级制造缺陷,原理如图1 所示。Bhavani G[18]等提到,有自修复能力的扫描结构可提高故障测试的定位范围,采用延迟测试电路等技术可减小故障测试所需的功耗。

图1 边界扫描链测试方法原理

2.2.2 内建自测试电路

BIST(内建自测试方法)的核心是构建最小功能单元链以及迭代的方法,结构内部由开关、CLB 以及局部连线部分组成[19]。石超[20]等提到BIST 可以直接得到测试结果,核心部件由ORA(输出响应分析)、BUT(被测单元)以及TPG(测试激励生成器)三部分构成,结构流程如图2 所示。成本茂[21]等还提到了CUT (Circuit Under Test),若将TPG 对应的电路更换成适配于CUT 的电路,会使结果输出更加便捷。

图2 内建自测试流程

2.2.3 基于群时延的TSV(透硅通道)故障非接触测试方法

TSV 属于密度高,间距小的复杂高速互连结构。无探针信号可进行多音混合测试设计,通过检测器得到输入输出信号的CF值,分辨率较高[22]。Shang Yuling[23]等提出基于电特性的TSV 多音混合信号模型,所用金属线功耗小,覆盖范围包括欧姆级至百万欧姆级。测试时提取并合并子测试向量,利用单卡故障模型有助于减少测试向量,从而降低VLSI 测试成本[24]。不同测试技术优缺点比较如表2 所示。

表2 测试技术优缺点比较

3 中央处理器自修复技术体系

3.1 基于实时调度的替代修复技术

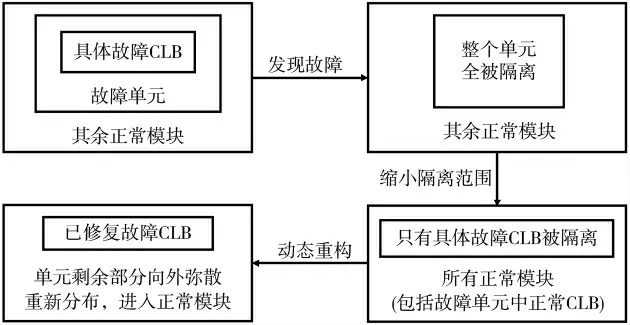

替代修复技术的起源于生物系统自修复[25],原理如图3 所示,通过划分小单元来减少故障出现时所隔离的正常单元的范围来重定位,实现了低成本,高效率[25],但硬件资源消耗大。

图3 实时调度自修复技术原理

基于FPGA 的重构修复技术将粗粒度与细粒度划分相结合:只有低优先级故障时,尽可能减小隔离范围;只有高优先级故障时,使用备用模块解决;当高低优先级同时出现时,先删除部分低优先级腾出空间,再解决高优先级。

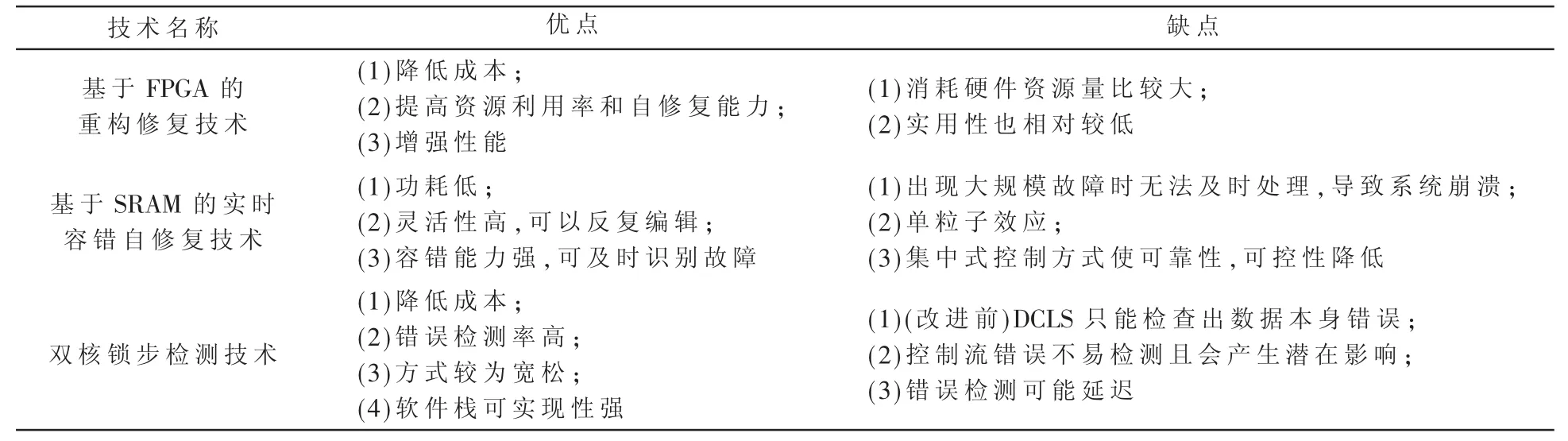

3.2 实时容错自修复技术

徐伟杰[26]等提到基于SRAM 型的FPGA 技术,采用表决器三选二技术,只要有两个正常便不会报错,但错误逐步积累并爆发会使系统崩溃。Peña-Fernández M[27]等提到DCLS(双核锁步)进行冗余多线程支持和控制流错误检测,将两个处理器分别执行的操作步骤逐一对比,一旦出现不同步的情况便会触发报警机制。优缺点对比如表3 所示。

表3 替代修复与容错自修复优缺点比较

3.3 基于其他技术的自修复技术

Sheikhpour S等[28]提到AES(高级加密标准)法,包括循环码、时间、奇偶校验冗余等。Zandevakili H等[29]提到ASIC(专用集成电路结构)和BISR(内置自修复技术)。ASIC在最小延迟下,可重构基本单元自我修复后将新的路由网络替换故障部位;BISR 处理永久故障,分为故障检测、故障诊断、故障隔离和冗余分配。

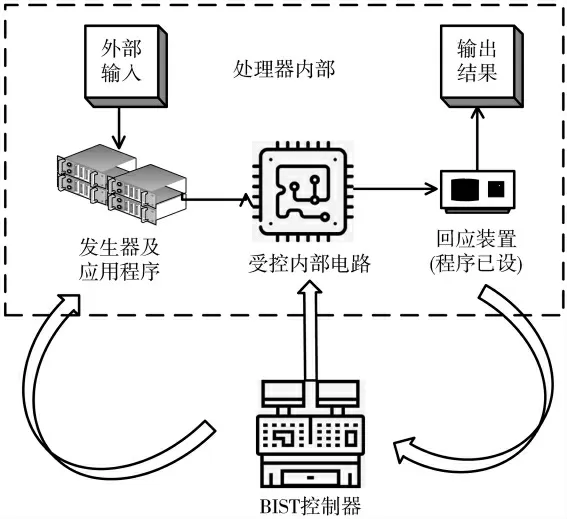

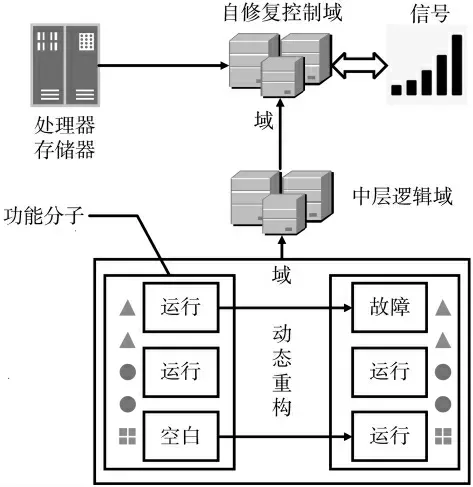

袁霄亮[30]等提到基于细胞阵列的自修复技术(见图4)。一个小分子工作时,其他分子处于休眠状态,总体呈动态重构,自由度、自主性提高[27]。Rahiminejad E[31]等提到基于神经形态的模拟集成电路,在宽频率内补偿受损突触。

图4 基于细胞阵列的自修复技术

Carroll R[32]等提到IC 修复,细化识别节点后同电压对比成像结合贴合各个面;Fu W[33]等提到贝叶斯技术,以集成数据为驱动探测探针卡故障,文本转换为数字后以网络图的形式可视化;Fan W[34]等提到NOC 内部容错机制,环面布局利用循环嵌入不完整节点;Khera V K[35]等提到基于Mesh 的具有路由器级冗余的容错NOC,结合重构算法和备用路由器法,每个路由器集合中可容忍一个故障路由器。

4 中央处理器协同安全架构模型

综合上文对安全测试和自修复技术的研究分析,将故障注入与测试在自修复前进行来提高中央处理器安全性能,总结出如图5 所示的安全协同结构模型。将故障注入结合JATG 调试技术、Doctor、Pin、SFIS 可更好地提升中央处理器的安全性能。可测试设计以TAP 为核心,根据具体情况选择芯片内部或端口的方法。对于特殊结构的封装集成电路,基本采用内建自测试电路,单粒子翻转则可用TSV 法解决。故障修复以实时调度和实时容错自修复技术为主,结合其他领域技术进行修复也是提高性能的关键一步。

图5 中央处理器安全协同模型

5 结论

随着工业控制领域竞争日益激烈,工业控制芯片中央处理器的安全性得到广泛关注。科研工作者们发掘各种可靠测试与自修复技术模型,旨在最终提高中央处理器的安全性。现做三个方面总结:

(1)软件和硬件结合、物理建设与模拟实验结合、设计与评价阶段结合是未来技术发展趋势。

(2)由于硬件的物理性接触与处理器结构中微小部件的高灵敏度产生矛盾,新技术开发应以算法设计为主体。

(3)系统容错机制的整体控制模糊性带来错误崩溃等安全隐患,采用分布式自控、精准对点、分块隔离可有效解决。