存储系统中L 波段射频直采技术设计与实现

2022-10-20林文成董郑宇李琼

林文成,董郑宇,李琼

(中国电子科技集团公司第五十二研究所,浙江 杭州 310012)

0 引言

按标准的雷达频率命名法[1],L 波段是指1 000~2 000 MHz 的无线电电波波段。按传统实现方式[2],先采用射频模拟下变频模块在模拟端将1 000~2 000 MHz 变频到100~1 100 MHz,然后采用低采样率的ADC 进行信号的采集。此方法由于采用了大量的包括低噪放、滤波器、衰减器和本振电路等模拟器件[3],考虑到模拟器件本身易受干扰和有源器件容易引入噪声等因素,会大大降低系统的无杂散动态范围(Spurious-Free Dynamic Range,SFDR)值,一般只能做到50~55 dBFS。本文提出了全新的一种真正实现L 波段全频段射频直采的设计方案,采用超高采样率(采样率达到6 GS/s)的ADC 芯片实现射频直采,不但简化了前端的采样电路,而且使SFDR 提高到了65~70 dBFS。

1 存储系统中的射频采集存储方案

存储系统中传统的射频采集存储方案如图1 所示。

图1 传统数据采集存储方案

从图1 中可以看出,方案中主要板卡包括射频下变频模块[4]、中频模拟采集模块、存储控制单元和电源模块等。此方案不但使得存储系统变得复杂,板卡数量较多,同时性能上受到了比较大的影响。

本项目采用如图2 所示方案,与图1 对比可知,本方案中少了射频下变频模块和中频模拟采集模块,取而代之为射频直采模块,大大降低了前端电路设计的复杂度。另外,射频直采模块主要由单片ADC+FPGA 架构组成,硬件成本在5 万元左右。两个方案的成本相差大概在7.5万元。

图2 本文采用的数据采集存储方案

根据Nyquist 采样定理,fs≥2fh[5],为了实现L 波段的全频段射频直采,采样率需要满足fs≥4 000 MHz,为了得到更好SFDR 性能,本文将采用fs=6 000 Mz 来实现L波段的全频段射频直采。本文采用ADC 芯片为ADI 公司的AD9213BBPZ-10G。该芯片支持最大的采样率为10.25 GS/s,量化位数为12 bit,最大接收带宽为6.5 GHz(-3 dB),SFDR值为70 dBFS,接收带宽满足L 波段的设计需求。下面描述具体设计实现方案。

2 射频直采方案硬件设计

2.1 时钟电路

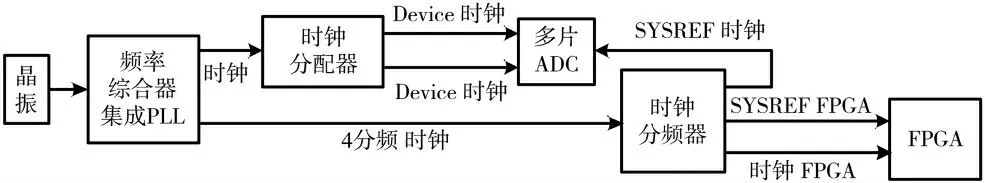

传统时钟电路采用超低抖动自带有支持JESD204B[6]总线的专用时钟芯片实现,但是目前采样率已达6 GS/s以上,市面上单片的时钟芯片解决方案已无法满足需求,需要采用多芯片级联构建的方式实现,具体实现框图如图3 所示。

图3 时钟电路原理框图

多芯片级联构建电路有如下特点:

(1)支 持JESD204B总线。

(2)输出的频率范围灵活可调,输出范围更宽。既能兼容单芯片的方案,也能满足采样率不断提高的使用要求。

(3)具备高可塑性,通过简单的模块更换,可以实现更高频率的输出,满足不同项目的不同采样率的使用需求。

频率综合器采用ADI 公司的ADF4372,单芯片集成锁相环(Phase-Locked Loop,PLL),超低抖动值(38 fs)[7],输出通道有3 路,其中一路最高输出频率为16 000 MHz,剩余两路最高输出频率为8 000 MHz,内部集成固定分频比电路,分别是1/2/4/8/16/32/64。本设计中,采样率设计为6 GS/s,ADF4372 输出1 路Device Clock 给时钟分配器,由分配器分成多路Device Clock 送给多片ADC作为ADC 的采样时钟。时钟分配器采用ADC 公司的HMC987,支持最高工作频率为8 000 MHz,可以将1 路时钟通过内部分配输出9 路时钟。

时钟分频器采用TI 公司的LMK04828,LMK04828 时钟芯片是一款专用的JESD204B 超低抖动时钟芯片,Device Clock 和SYSREF Clock 是成对输出的。由于其最高输出频率只能达到3 080 MHz,无法满足本项目的需求,但是可以运用其内部的分频电路和SDCLK 和DCLK 是成对输出的特性,作为Clock FPGA 和SYSREF FPGA 的输出接口。

前端采用高频率稳定度的晶振,晶振频率为100 MHz,频率稳定度达0.5 ppm。

整个电路工作原理如下:晶振产生的时钟输入给频率综合器,频率综合器产生两路时钟,分别为6 000 MHz和1 500 MHz,6 000 MHz 送给时钟分配器,分配给多个ADC 使用,1 500 MHz 送给时钟分频器,输出SYSREF Clock、SYSREF FPGA、Clock FPGA 分别给ADC 和FPGA使用。此电路设计既保证了各时钟的同源性,又满足了ADC 采样时钟和JESD204B 总线对不同频率时钟的需求。

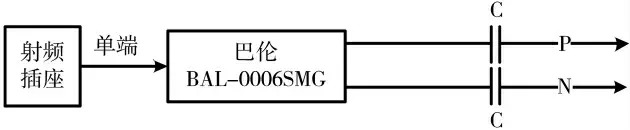

2.2 射频采集电路

本文采用ADI 公司生产的最新ADC 器件AD9213-BBPZ-10G,为了减少前端模拟电路对采样性能的影响,整个前端电路采用以巴伦为主要器件的无源器件搭建而成,如图4 所示,巴伦为一种三端口器件,实现将匹配输入转换为差分输出而实现平衡传输线电路与不平衡传输线电路之间的连接的宽带射频传输线变压器[8]。

图4 前端采集原理框图

输入的射频信号通过巴伦转换为差分信号后,再通过交流耦合电容送给ADC 器件,耦合电容的值需要依据实际工作频率值进行选取。公式如下:

其中f 为最小工作频率;Zc为电容中的等效串联电阻(ESR),一般小于1 Ω。L 波段电路中优选COG(NPO)材质的大封装电容,大封装尺寸的比小封装尺寸的电容频率特性要好。

2.3 FPGA 处理电路

ADC 器件的后端接入现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA),FPGA 选用Xilinx 公司的VIRTEX 7 系列690T 芯片。为了保证在全带宽模式下正常工作,将ADC 的16Lane 接入FPGA 的GTH 总线上。VIRTEX 7 系列690T 芯片最多含有80 GTH 收发器,最高速率支持13.1 Gb/s,满足JESD204B总线7.5 Gb/s 的总线速率要求。

3 射频直采方案软件设计

如图5 所示,本系统通过在V7_690T FPGA 内嵌入MicroBlaze 处理器软核并运行配置控制程序实现对时钟芯片ADF4372、LMK04828 和ADC 芯片AD9213 进行配置控制。利用Xilinx JESD204 IP 核搭建如图6 所示的Block Design 框图[9],实现与AD9213 JESD204Bx16 接口对接,接口协议采用JESD204B Subclass1。

图5 系统实现简图

图6 FPGA_JESD204Bx16 接收端Block Design 框图

AD9213 内部结构简图如图7 所示,其内部自带数字下变频(Digital Down Converter,DDC)功能模块,使用时可以根据需求配置相关寄存器选择JESD204B 输出数据源。AD9123 可以预设16 种固定中心频率,通过GPIO 或者SPI 寄存器进行切换,此种切换不需要对JESD204B 链路重新进行同步,若需要设置其他非预设的中心频率,则需要对JESD204B 链路进行重新同步操作,整体响应时间较慢。本设计为了灵活配置中心频率且加快响应速度,使AD9213 工作在全带宽采集模式下,在后端的FPGA中实现DDC 功能。

图7 AD9213 内部结构简图

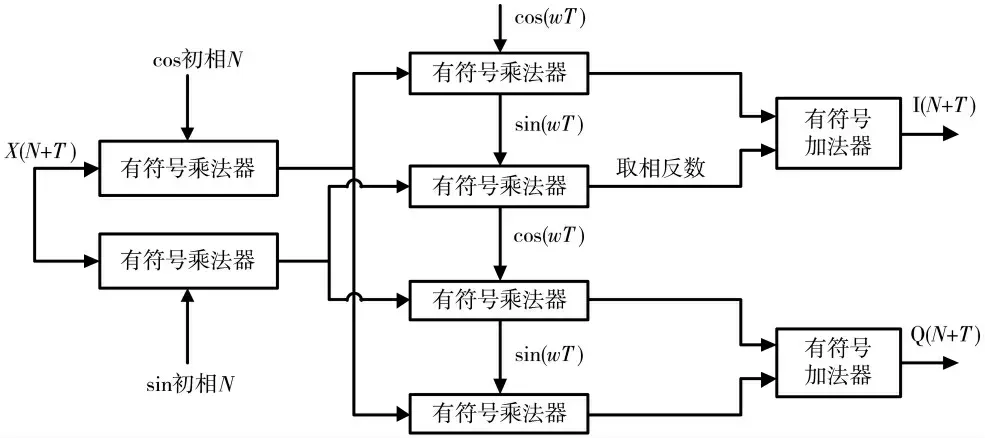

对JESD204B 接收的数据按照JESD204B 协议标准帧组成格式进行解析即可得到原始采集的中频信号。FPGA 端实现DDC 功能框图如图8 所示,由于AD9213的采集带宽较大,若按照典型的单路数据进行混频运算势必需要非常高的时钟频率,故需要采用并行NCO 混频设计,然后对混频后的I、Q 数据结果进行并行滤波、抽取。根据使用效果将不同的NCO 混频参数传递至并行混频模块即可实现动态切换中心频率的效果。

图8 DDC 算法原理框图

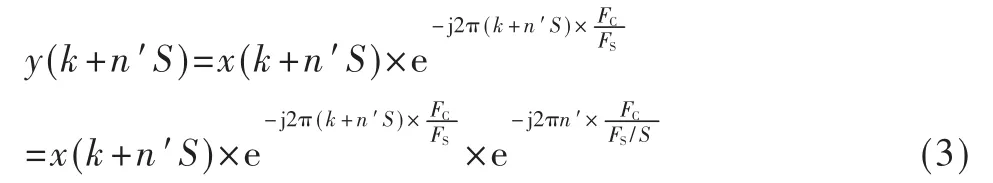

并行NCO 混频算法实现的原理推导过程如下[10-11]:

典型的混频运算数学公式如下:

其中FC表示中心频率,FS表示采样频率。

当采样数据按照并行输入时,令n=k+n'S(k 为某时刻的并行点序号,k=1,2,3,…,S;S 为并行采样点个数),则可到如下公式:

对上式进行三角函数展开即可得到如图9 所示的算法框图的计算过程。

图9 并行NCO 混频算法框图

4 系统性能分析和实测

在存储系统中,将前端射频直采的数据送至存储控制单元进行存储,并通过存储控制单元的网络接口,可以将已存储的数据进行快速地卸载到分析设备中,以便于后续的数据分析和处理。当对1 路射频模拟信号进行直采时,采样率fs采用6 000 MS/s,在1 000 MHz 进行全带宽采集时,记录的存储带宽计算可得:6 000 MS/s×(12 bit/8)=9 000 MB/s,单路的存储带宽为9 000 MB/s;单路按1 000 MHz 带宽进行数字下变频后所得I/Q 数据(抽取倍数4 倍,采样率下降到1 500 MS/s)可得采集存储带宽为9 000/4×2=4 500 MB/s。

整个系统选用Intel i7 CPU 控制器+FPGA 可编程逻辑器件作为主控元件。采用基于FPGA 的高速串行总线和PCIE 互连技术的高性能存储系统构架实现数据的快速传输。详细实现框图如图10 所示。

图10 详细系统框图

FPGA 自带的GTH 高速串行总线接口按8.0 Gb/s速率进行传输,每组GTH X4 接口传输带宽理论可达4 GB/s,按RapidIO 协议工作时的损耗,1 组X4 接口实际传输带宽具备3.2 GB/s 传输能力,射频直采模块用2 组X4 RapidIO 接口的存储带宽可达6 400 MB/s,满足前端4 500 MB/s 的采集存储带宽。

射频直采模块将数据送往存储控制单元,存储控制单元主要由Intel i7 CPU 控制器和m.2 电子盘组成,m.2电子盘采用PCIE3.0 X4 接口完成高速的数据存储。PCIE3.0 按8 Gb/s 速率进行传输,一组PCIE3.0 X4 接口传输带宽理论可达4 000 MB/s,按64%效率进行计算,其实际可用带宽为2 560 MB/s,因此采用2 组m.2 电子盘的存储带宽可达5 120 MB/s,满足前端4 500 MB/s 的存储带宽。因此整个系统的采集处理和存储同步进行时,实时效率可达100%,能将采集的数据实时完全地存储下来。

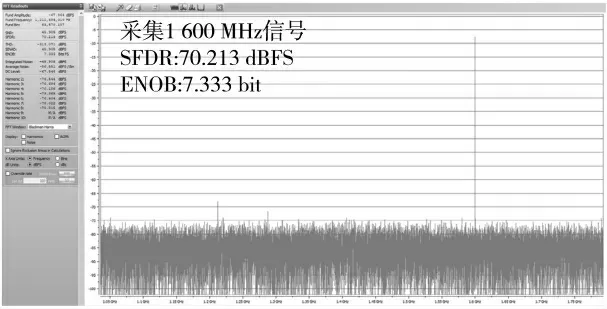

系统实际测试的数据如图11~图13 所示,图中为L波段不同频点的射频直采频谱图,从图中可以看出,采用本文的射频直采方案,可以将SFDR值提高到67 dBFS~75 dBFS,ENBO 可达7.0 bit~7.3 bit。

图11 950 MHz 频点的性能图

图12 1 600 MHz 频点的性能图

图13 2 150 MHz 频点的性能图

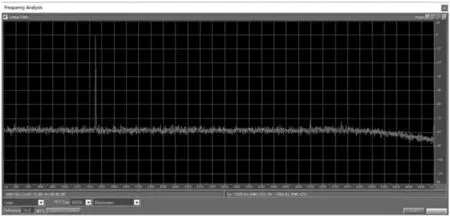

另外通过DDC 算法后的数据的性能如图14 所示,SFDR 性能可达70 dB 以上,ENBO 可达7.3 bit。

图14 DDC 性能实测图

经过对系统性能的测试,可以看出本文设计的6 S/s波段射频直采的存储系统在全频段上的SFDR值依然能保持在67 dBFS 以上,可见系统具有良好的采样存储性能。本文采用了高性能的ADC、简单的前端电路设计及低抖动的时钟电路等设计方案,最终实现高性能的L波段射频直采的存储系统。

5 结论

本文介绍一种运用在存储系统中的L 波段射频直采设计和实现方案,对整体的硬件方案、软件方案分别进行阐述,最后对系统的性能指标进行实际测试,测试结果表明了系统的良好性能。另外,整个方案在减少系统复杂度、降低硬件成本的同时,提高系统的SFDR值,为存储系统提供更加纯净的信号数据,同时也更有利于后续的数据分析处理。