基于单片机和FPGA的等精度频率计系统设计

2022-10-19毛群

毛群

(阿坝师范学院 电子信息与自动化学院,四川汶川, 623002)

0 引言

频率测量在信号处理、工程应用中随处可用,常见的频率测量方法有直接测频法和周期测频法以及等精度测频法。其中直接测频、周期测频法的弊端在于测频误差要随待测信号本身频率变化而变化,使其在工程应用中有所限制。而等精度测频法测量精度高且不会因待测信号频率变化而发生变化[1]。

1 等进度测频法原理

等精度测量频率方法消除误差的原理是采用被测信号触发门控信号,使得实际门控信号周期不再是一个固定值,而刚好是被测信号周期的整数倍,这样便消除传统测量中产生±l的周期误差,使测频精度与待测信号频率无关,实现待测信号全频率范围等精度测量[2]。其时序如图1所示,设在闸门时间T内,计数器计数N个待测时钟,计数M个基准时钟。

图1 等精度测频工作时序图

在时间T内,利用两个计数器同步计数关系有:

则待测信号频率为:

2 频率计系统设计

数字频率计系统由自动增益控制AGC模块、整形模块、频率采集模块、主控模块和液晶显示模块构成,系统结构框图如图2所示。频率采集模块采用FPGA实现,用它设计等精度测量模块和SPI通信模块,对数据进行采集后送给单片机,完成对频率数据的采集和与主模块通信。主控模块采用STM32F103C8T6单片机,其内置64K或128K闪存程序储存器,具有快速处理数据、低功耗、价格低廉等优点。STM32单片机接收数据后,对数据进行处理计算,送LCD液晶显示。系统前端主要是利用压控放大器AD603和检波电路实现信号增益控制,集成施密特触发器74HC14电路模块实现信号整形[3]。

图2 系统结构框图

3 核心模块设计

■3.1 自动增益控制及整形电路设计

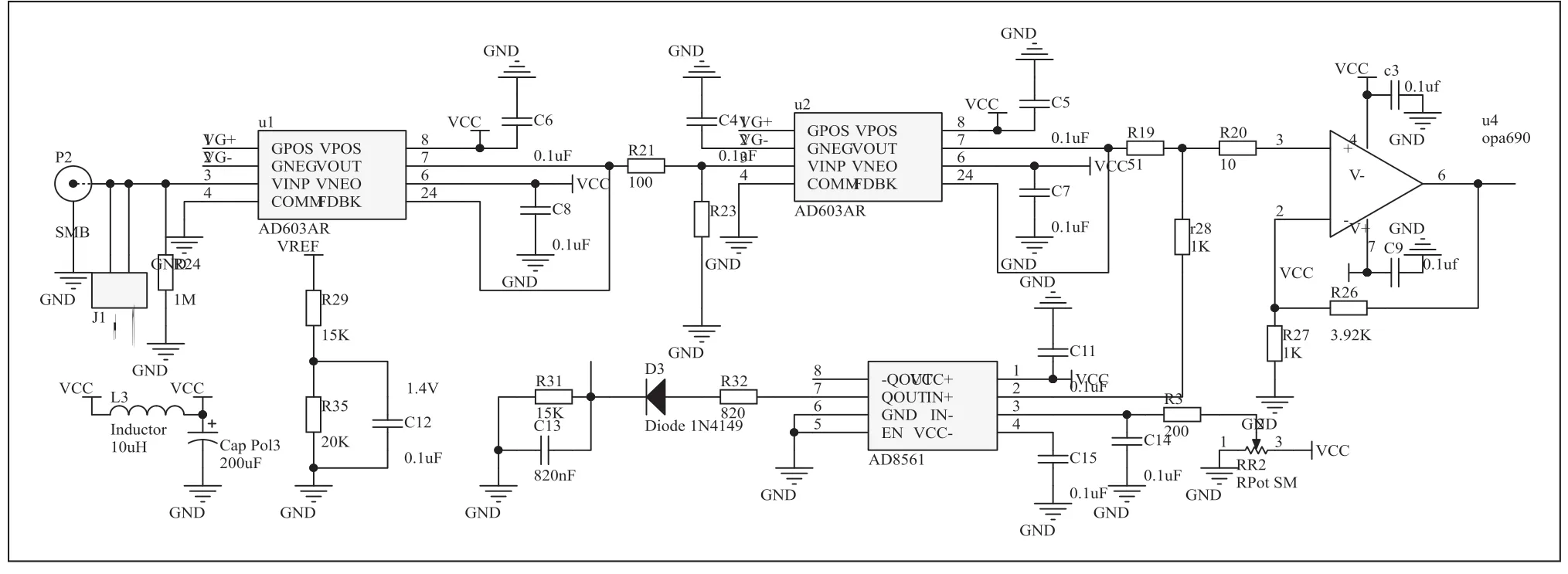

为适应各种频率、幅度的待测信号fs,频率计系统设计了自动增益控制电路(AGC),该模块主要由程控放大器AD603、高速比较器AD8561、集成放大器OPA690和检波电路构成,如图3所示。电路基本原理:通过放大信号反馈改变电路放大倍数,实现自动调节,使放大信号幅度在一定的范围内保持稳定[4]。从而控制其增益,使其输出幅度稳定的信号。输出信号通过如图4所示共射放大整形电路输入FPGA。

图3 自动增益控制电路图

图4 整形电路图

■3.2 等精度测频模块电路的FPGA设计

基于等精度测频原理,通过Verilog语言编写代码,设计等精度测频模块电路,电路如图5所示,本设计采用的是FPGA CycloneII-EP2C5T144C8N。脉冲计数(signal)采用系统时钟分频。单片机发送清零信号对FPGA计数器清零,发启动信号到FPGA的enable端口。经过逻辑判断后计数模块输出高电平的clken信号到DFF触发器输入D端口,此时触发器输出Q端是低电平,计数模块还没有开始计数和计时,只有当输入信号出现上升沿时,触发器输出Q端才输出高电平到计数模块的gate_ctr端口(门控信号),计数模块在门控信号为高电平时开始对输入信号和标准时钟信号计数。当计时到1s时,计数模块控制逻辑输出低电平的clken信号到DFF触发器D端口,此时触发器输出Q端还是高电平,计数模块还没停止工作,只有当输入信号出现上升沿时,触发器输出Q端才输出低电平到计数模块的gate_ctr端口。因为计数器是在输入信号上升沿开始工作,同样在输入信号的上升沿结束,实现了等精度测频,没有脉冲计数的误差[5~6]。

图5 等精度测频原理的FPGA设计电路图

在结束一次测量后,计数模块(freq)输出finish信号给单片机,单片机分时读取计数数据和计时数据,并完成计算处理得出频率。读取数据需要sel、addr0、addr1控制信号参与,数据口(count)是8位,而计数(计时)32位,可分批读取,当SEL为1时,读取计数值,分4次读取;当SEL为0时,读取计时值,分4次读取,然后进行数据处理。读取并处理完成数据的频率值后,进入下一次测量。下一次测量前,单片机发送clr清零信号到FPGA,把上一次的计数计时数据、信号标志位等复位;单片机发送启动信号(低电平)到FPGA的enable端口,开始新一轮测量。

■3.3 FPGA模块设计

FPGA除了完成等精度测量电路,还要实现将采集的频率数据与主控单片机模块通信,故在FPGA中设计SPI通信模块。其工作时序为SCK上升沿数据采样,下降沿输出数据。在SPI通信模块中先分别捕捉由STM32传送的SCK信号的上升沿和下降沿,然后SCK上升沿且CS为低电平,FPGA作为从机逐位读取STM32主机发送的命令数据并寄存在rxd_data中,再传送freq模块的rxd_command;SCK下降沿且CS为低电平,FPGA从机通过MISO通道向STM32主机逐位传送寄存在txd_Data中的数据。采用Verilog语言编程实现的FPGA电路设计如图6所示。

图6 FPGA模块整体电路图

■3.4 单片机主控模块设计

单片机主控与外围电路连接如图7所示,本设计使用STM32F103C8T6单片机。其中2脚~14脚外接一个LCD液晶显示,用于显示测得的信号频率和周期;21脚~24脚是用于与FPGA通信的四条SPI串线:从设备片选CS、MISO通道、MOSI通道和时钟信号SCLK。四条SPI串线控制整个系统:通过SPICS选中FPGA或初始化FPGA,时钟信号SCLK是由STM32控制,STM32向FPGA发送数据时设置为高电平,STM32接收FPGA传回的数据时设置为低电平。MOSI通道用于STM32向FPGA发送数据或者命令,而MISO通道则是用于FPGA向STM32发送数据或者命令,通过这两个通道,在时钟信号的相应阶段,实现STM32和FPGA的通信。

图7 STM32电路连接图

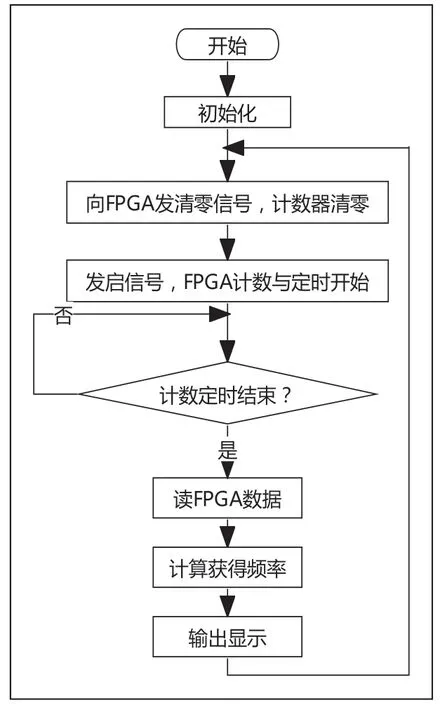

STM32主控设计流程如图8所示。当系统开始运行,STM32单片机初始化I/O端口和LCD液晶显示后,根据SPI协议,通过MOSI端向FPGA发送初始化命令(其中包括使能清零和数据清零),再向FPGA发送测频使能信号,控制FPGA开始测频,FPGA计数器计数和定时。单片机检测FPGA是否传送回测频结束信号,确定状态:如果接收到测频结束信号,则从FPGA中读取测频数据,同时控制FPGA停止测频,然后对采集的数据进行运算处理得到所测的频率和周期,并在LCD1602液晶上显示,再将FPGA初始化,启动下一次测量。

图8 STM32单片机主控流程图

4 系统测试

由于自动增益控制电路带宽设计约为45MHz。系统测试时,在选 择1Hz~40MHz内 选 取100Hz、100kHz、1MHz、10MHz、40MHz频率点进行测试,测量结果如表1所示。从测量结果可以看出,所设计的等精度数字频率计系统消除了频率测量中的±1误差,在整个测量范围内测量相对误差都在2×10-4以内,系统具有较宽测量范围和一定精度。

表1 测量结果

5 结论

本文设计的数字频率计主要利用FPGA和单片机设计,由FPGA采集计数值,单片机进行频率值计算和显示,规避了FPGA不便于浮点运算的不足,有效利用单片机便于控制及人机交互的特点。实验表明,提高系统晶振频率和精度,可有效保证频率计的测量精度,该设计具有潜在的实用价值。