一种新型Ku频段硅基氮化镓多通道功率MMIC*

2022-09-28姚明

姚 明

(中国西南电子技术研究所,成都 610036)

0 引 言

单片微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)功率放大器作为当今相控阵天线射频前端不可替代的器件,广泛应用于雷达航天等领域[1-2]。在这些应用领域,相控阵阵元数量日趋庞大:一方面,小型化的要求使得射频通道高密度集成,多通道集成于一个芯片的需求越来越强烈;另一方面,以碳化硅(SiC)基氮化镓(GaN)为代表的第三代半导体功放单元由于其优秀的功率输出能力,在相控阵天线的射频前端中越来越多被采用[3-5]。然而,其过高的成本限制了相控阵天线在许多平台上的应用。近十年来,国际上一直在探索基于Si基GaN工艺的功率集成技术,试图将GaN材料的功率优势和Si材料的低成本和高集成度优势相结合。本文设计了一款Ku频段Si基GaN多通道功率放大芯片。该芯片通过一定的隔离技术实现了多个射频通道的集成,同时采用了一种提高耐压能力的新型匹配技术,规避了Si基GaN工艺的耐压局限,使芯片既具有高集成度、低成本的优势,又能在工作频段内满足大于40 dBm的饱和输出功率和大于35%的功率附加效率的性能要求。

1 工艺平台及器件特性

本芯片采用OMMIC公司的3英寸0.1 μm T型栅Si基GaN D01GH工艺平台。该工艺采用AlN/GaN/AlGaN有源层生长在高阻Si衬底上的异质结结构。晶体管电流增益截止频率100 GHz,功率增益截止频率为180 GHz。栅漏击穿电压典型值为40 V,最大跨导为620 mS/mm。有两种电阻可供选择,一种是方阻为40 Ω/口的NiCr薄膜金属层电阻,另一种是高阻值的GaN有源层电阻。该工艺的金属-绝缘体-金属(Metal-Insulator-Metal,MIM)电容也有两种不同的介质类型,一种是电容密度较高的Si3N4介质层电容,一种是Si3N4+SiO2介质层电容。

2 芯片设计

芯片设计和仿真在ADS软件平台中完成。在芯片功能结构设计之前,首先要对晶体管进行直流工作点扫描,根据功率和效率指标的要求,确定晶体管的直流工作点和放大器的类型。接下来要对管子的输出能力进行Loadpull仿真,得到管子最大输出功率和效率的特性,从而可以对管芯的性能进行评估,然后在此基础上选取管芯模型、分配各级增益,最终确立电路的拓扑,完成设计。

2.1 体结构

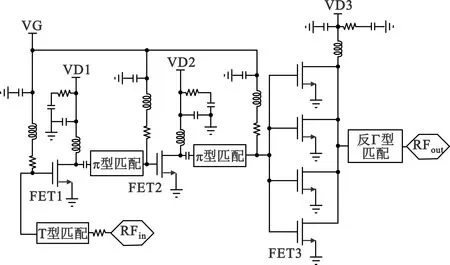

芯片功率放大通道的电路原理图如图1所示。其中,VG为栅极供电,VD1、VD2和VD3为漏极供电。在Ku频段,该工艺的晶体管功率密度约为3 W/mm。根据输出功率指标的要求和管芯Loadpull仿真的结果,同时考虑到功率设计值与真实测试结果一般会有1 dBm左右的差距,确定末级输出至少要3.8 mm的栅宽。因此末级晶体管FET3选取了单管芯8个栅指,单个栅指宽度120 μm,共4路8×120 μm管芯合成的尺寸结构。根据增益的要求,功率放大器采用了三级放大器级联的结构。除了末级的输出放大器以外,倒数第二级为驱动放大器,驱动末级达到饱和。驱动晶体管FET2采用与功放晶体管相同的尺寸,以保证其驱动能力。第一级放大器为增益放大器,其作用是达到总增益的要求。为了满足高输出功率和高效率的指标,三级放大器均选择AB类放大器。

图1 功率放大电路原理图

2.2 匹配电路设计

如图1中所示,末级输出匹配网络采用微带线—接地电容—微带线—接地电容形成的两级反Γ型匹配网络,将Loadpull得到的最佳输出阻抗匹配到标准的50 Ω阻抗。该两级反Γ型网络在参与匹配的同时,还起到了四路功率合成网络的作用。级间匹配网络均采用微带加接地电容形成的π型网络,起到共轭匹配的作用。输入级采用T型匹配网络,将第一级放大器的输入阻抗共轭匹配到50 Ω。

2.3 多通道设计

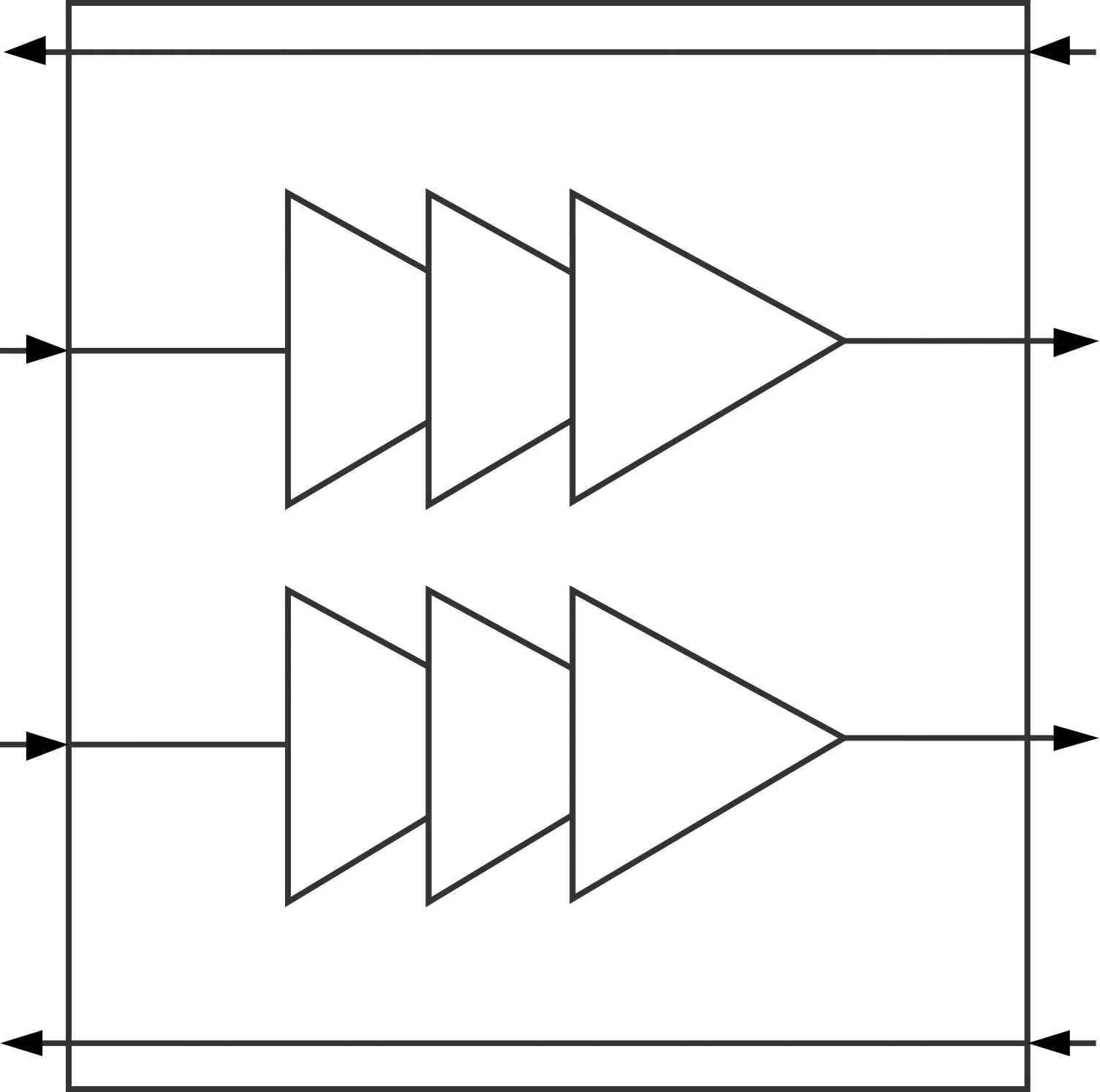

为了满足高集成度的应用要求,该芯片集成了两个功率放大通道和两个无源直通通道。多通道集成的示意图如图2所示。芯片的直通通道主要用于收发机接收通道的集成,通过设计和工艺保证即可,无需测试。经仿真,直通通道射频插损在工作频段内小于0.4 dB。

图2 多通道集成示意图

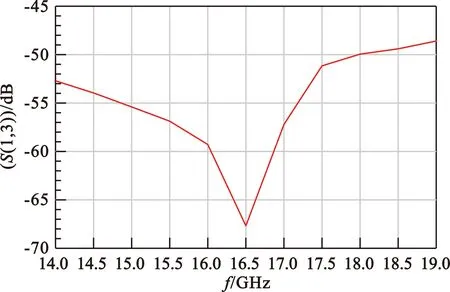

为了抑制两个功率放大通道之间的耦合现象以及无源直通传输路径和功率放大器之间耦合现象,在各个通道之间总共加入了3根接地隔离线。在面积允许的前提下,在隔离线附近放置了尽可能多的接地孔。其中无源直通通道与功率放大通道之间的隔离度仿真结果如图3所示,可以看出,在工作频率的范围内,两种通道之间有50 dB以上的隔离。

图3 直通与功率放大通道之间隔离度仿真

2.4 功放稳定性设计

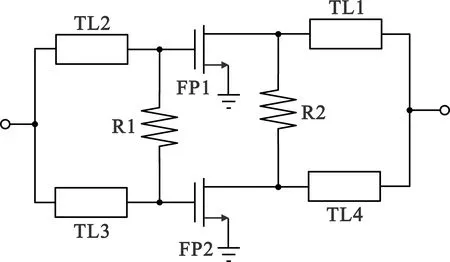

奇模振荡经常发生于窄带和增益压缩区域附近,在这种情况下输出功率会突然下降[6]。这种现象在功率合成中更加容易出现。为了抑制这种情况,在末级4个功率合成的晶体管之间加入了3个电阻以消除奇模振荡的影响。以其中的两个功率合成的放大晶体管FP1和FP2为例,它们的栅极和漏极之间分别并接电阻R1和R2,如图4所示,这样可以消除不平衡的信号。其中TL1~TL4为传输线。

图4 末级奇次模消除电路示意图

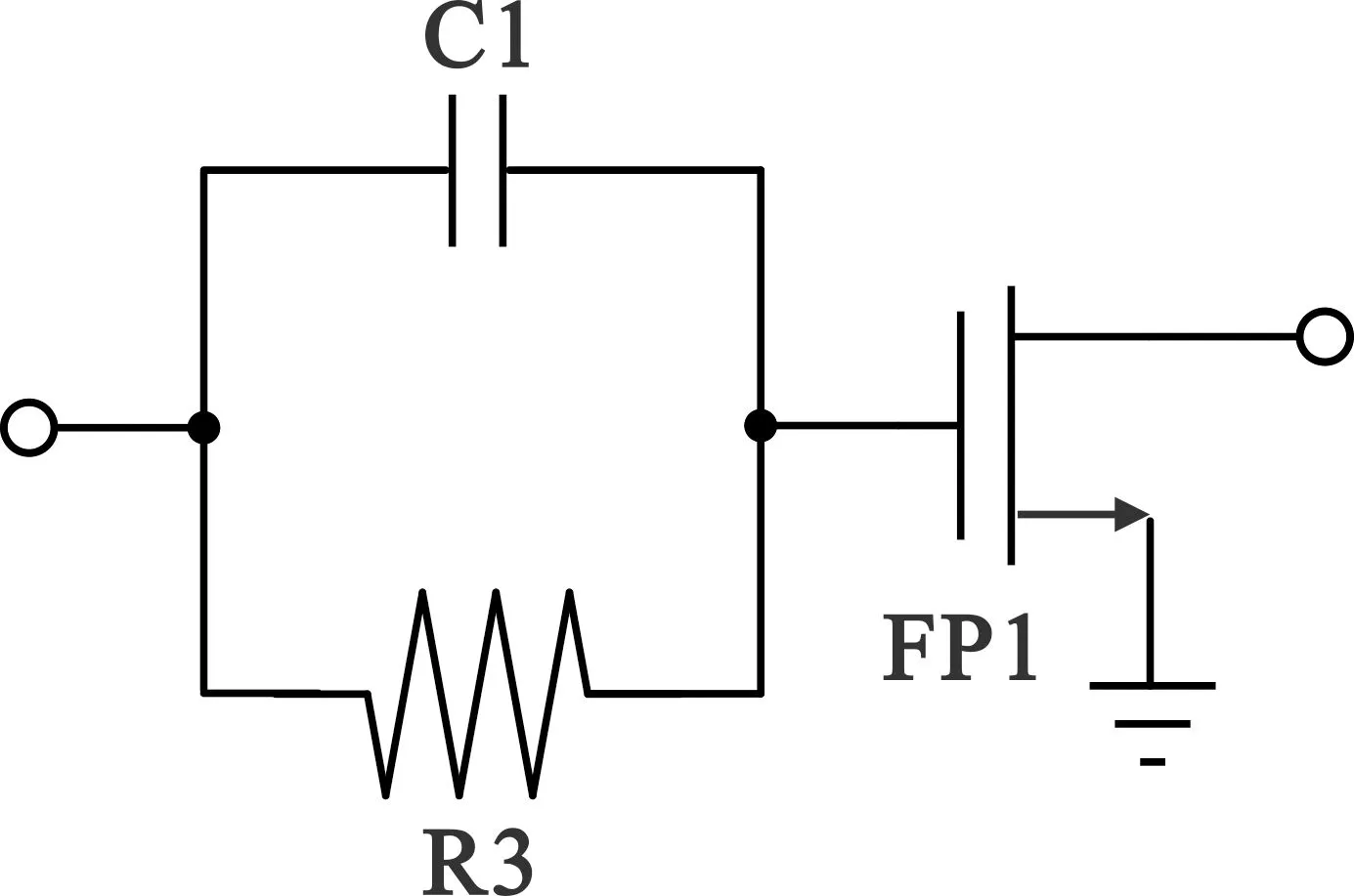

任何晶体管,只要不是无条件稳定,当连接上输入输出匹配网络或者直流网络时,都有可能产生偶模振荡[6]。为保证电路的稳定性,在所有放大管的栅极输入端,除了串联电阻R3外,同时加入一个与电阻R3并联的电容C1,如图5所示。这样既可以消除偶模振荡,又可以调节需要消减增益的频段,保证带内的增益平坦度。

图5 放大管输入端偶模振荡消除电路示意图

功放通道整体稳定性仿真如图6所示,可以看出在全频带范围内,功放的稳定因子均远远大于1。另外,功放每一级放大器的稳定因子在全频带范围内也必须大于1。因篇幅所限,仿真结果未列出。

图6 功放通道整体稳定性仿真结果

2.5 提高电容耐压能力的一种新型设计方案

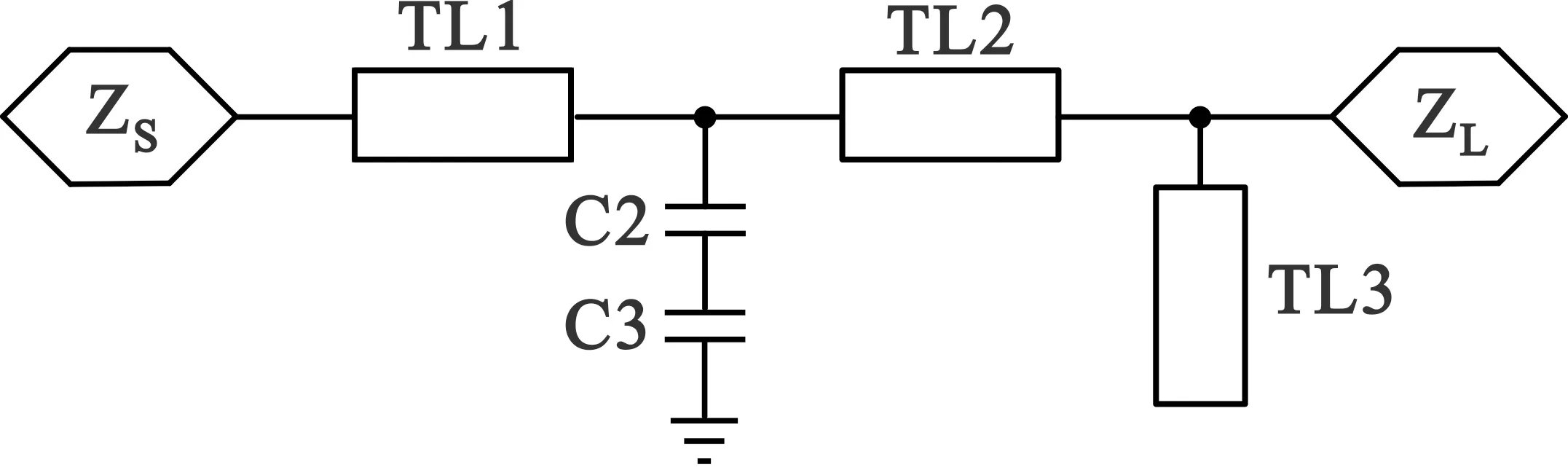

在芯片的前几轮流片测试中,当进行功率推饱和时,会出现功率放大器末级匹配电容烧毁的问题。这个问题与Si基GaN工艺的栅漏击穿电压较小有关。相对于SiC基GaN工艺90V的栅漏击穿电压[5],Si基GaN工艺的栅漏击穿电压不到前者的一半,这制约了Si基GaN工艺的大功率应用,也是该工艺有待解决的问题。为了规避该问题,在综合考虑到芯片尺寸要求的情况下,本文采用了以下两个方案:一是针对末级功率管输出的第一级匹配电容,用两个串联电容C2和C3来代替原来的单个电容,通过分压的方式减少单个电容被击穿的风险;二是针对最后一级匹配电容上承受的电压波动最大的情况,用微带线TL3完全代替最后一个匹配电容,这样可以完全规避电容击穿的问题,当然相应地会增加芯片的面积。末级匹配网络的设计方案如图7所示。

图7 提高末级匹配电容耐压能力设计示意图

3 芯片的加工与测试

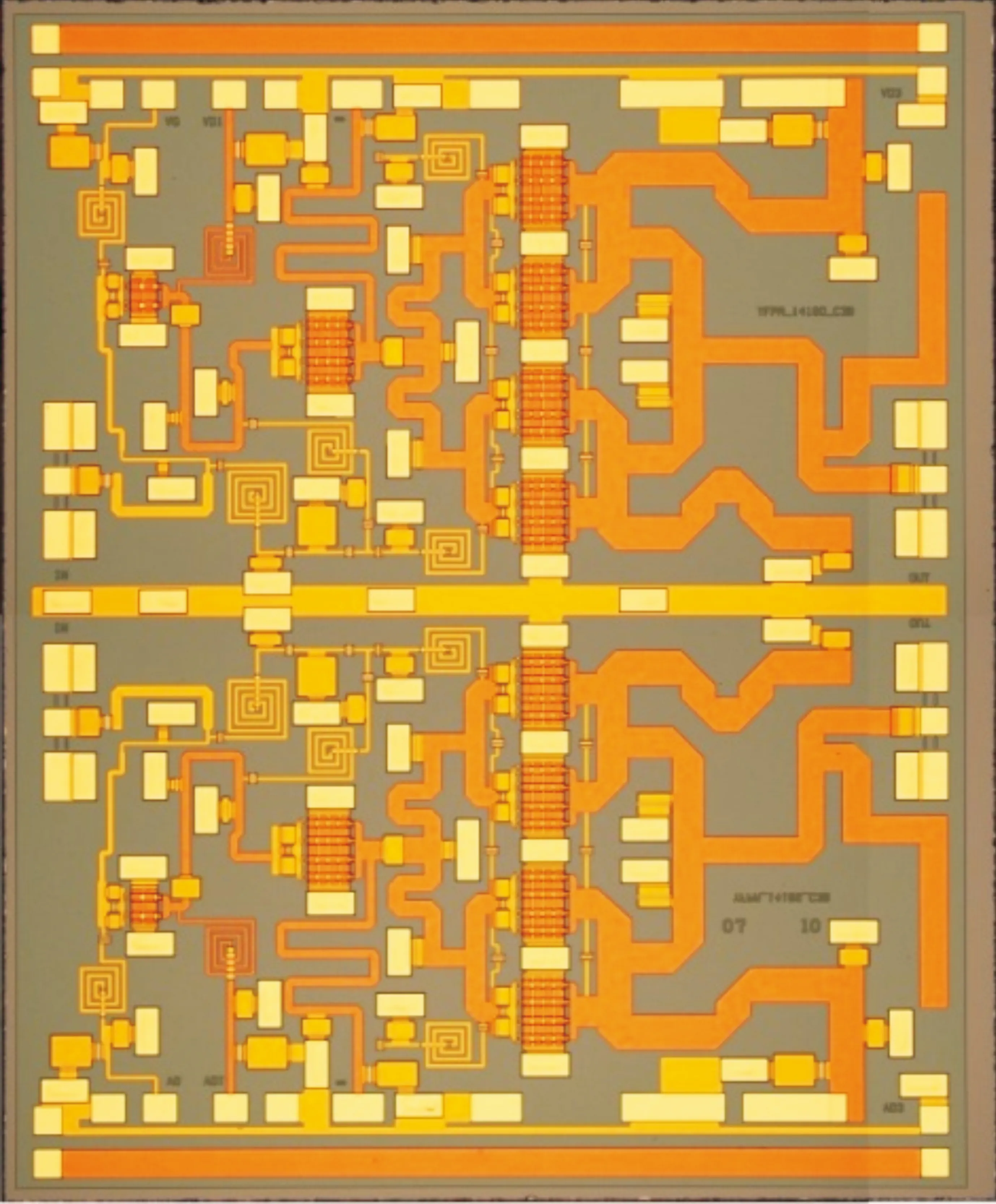

该Ku频段的多通道功率放大器芯片最终版实物照片如图8所示,芯片尺寸为3.5 mm×2.85 mm。

图8 14~17 GHz Si基GaN多通道功放芯片照片

芯片测试采用在片的方式进行,测试环境如图9所示。功率放大器栅极供电-0.8 V,漏极供电14 V,脉冲占空比10%。

图9 芯片测试环境照片

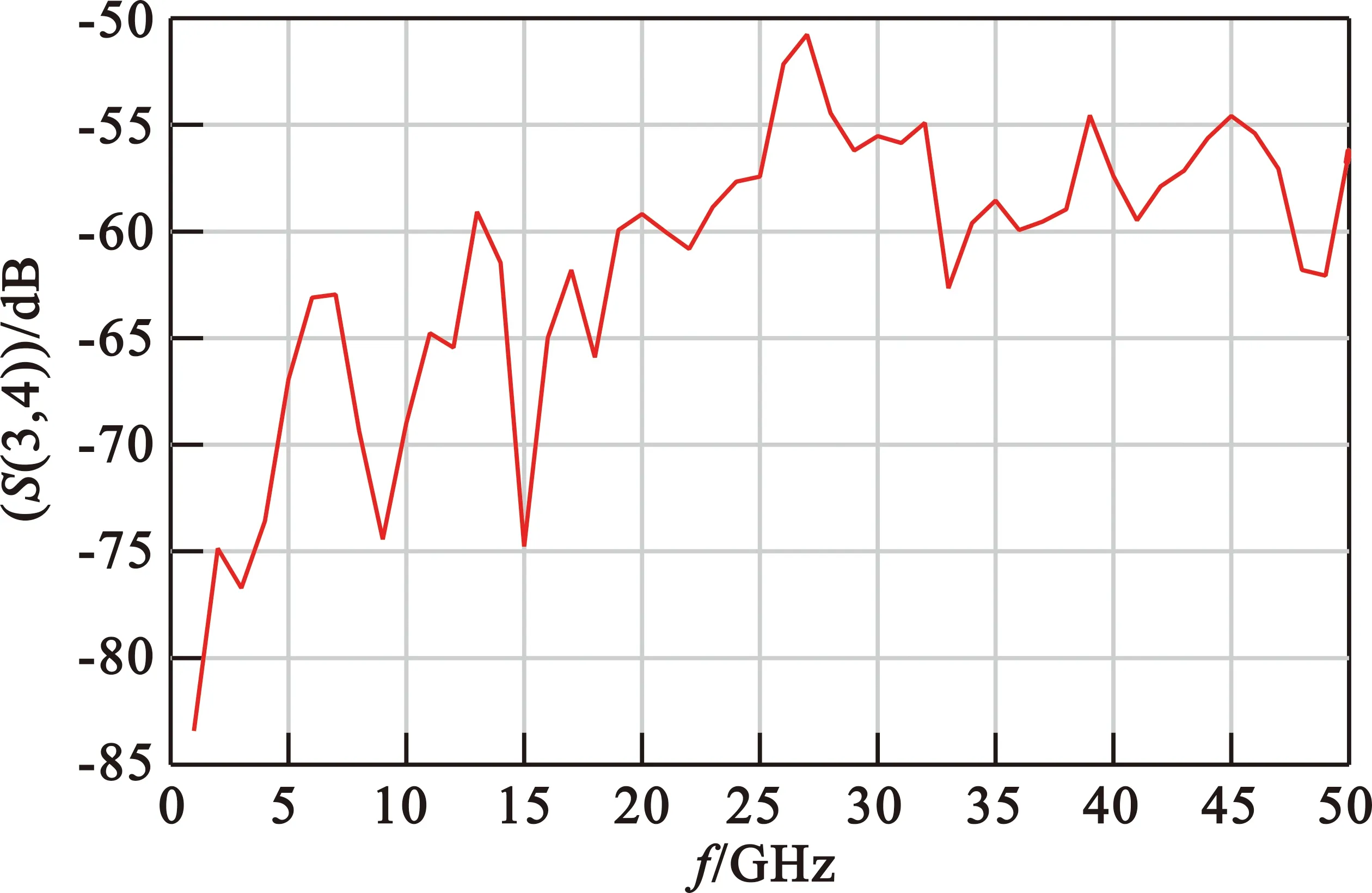

芯片的通道隔离度测试的结果如图10所示,可以看出各种通道之间的隔离度均大于50 dB,和仿真结果相吻合。

(a)功放通道端口交叉隔离度测试结果

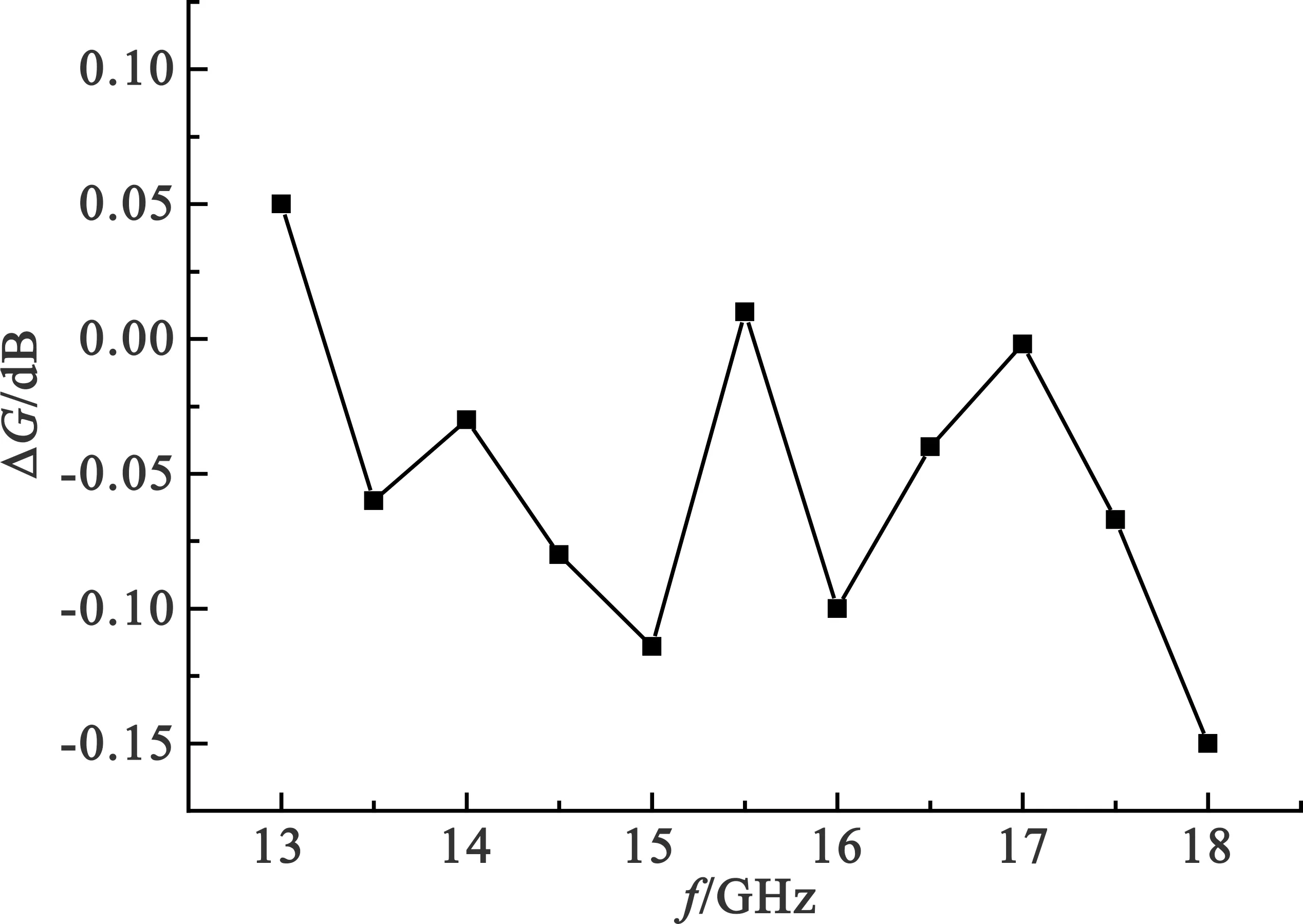

芯片双功放通道的幅相一致性和大信号测试结果均需要综合统计。其中,双通道幅度相位一致性小信号测试结果如图11所示,可以看出在工作频段内,幅度增益一致性小于±0.15 dB,相位一致性小于3°。由此可见,双功率放大通道一致性较好。

(a)幅度一致性测试结果

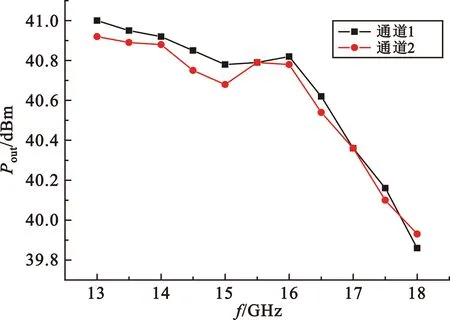

双通道大信号测试结果如图12所示,可以看出随着频率的升高,饱和输出功率呈现下降的趋势,功率附加效率先上升后下降,而且大于16 GHz以后,两者下降都较快。这种现象与频率偏离设计中心频率以及工艺自身特性相关。但在14~17 GHz工作频带内,饱和输出功率大于40 dBm,饱和带内功率附加效率(Power Added Efficiency,PAE)大于35%,能够满足应用的需求。如果改进Si基GaN工艺以进一步提高电容的耐压能力,该芯片的饱和输出功率和功率附加效率将能够进一步提高。

(a)功率放大通道饱和输出功率测试结果

4 结束语

本文介绍了研制的一款基于0.1 μm Si基GaN工艺制造的多通道功率放大器芯片,该芯片集成了两个功率放大通道和两个无源直通通道。针对多通道的特殊情况,通过通道之间的接地隔离技术提高通道之间的隔离度。针对Si基GaN工艺的耐压局限性,对末级匹配网络采用了一种新型的高耐压设计,最终既满足了工艺要求,又达到了多通道中功率放大的性能要求。该芯片的优点是低成本和多通道集成,不足之处是相对于SiC基GaN功率放大芯片功率输出能力偏弱。随着Si基GaN工艺的发展以及设计手段的不断完善,该类型功放芯片的功率输出能力有进一步提升的空间。