基于DB-PAM4 的高速SerDes 自适应均衡器设计

2022-09-27王和明吕方旭吴苗苗陆德超

王和明 ,王 正 ,吕方旭, ,吴苗苗 ,陆德超

(1.空军工程大学 防空反导学院,陕西 西安 710000;2.国防科技大学 计算机学院,湖南 长沙 410073)

近年来,由于大数据、物联网、5G 通信的飞速发展,人们对于高速传输数据的需求越来越大。而数据传输速率越高,对于高速串行链路的挑战越大,高速串行通信链路之间的有限带宽信道成为制约数据传输速率的瓶颈[1]。均衡器作为SerDes(SERializer/DESerializer)系统中接收机的核心模块,其对信道补偿能力的大小决定着整个SerDes 收发系统的性能。

由于趋肤效应、介质损耗的影响,使得信道整体呈低通特性,信号经过信道后高频衰减和低频衰减不一致,当数据传输速率达到112 Gb/s 时,高频部分的严重衰减会导致信号质量急剧下降,产生较大的码间干扰,误码率急剧增加。为了解决信道衰减引起的码间干扰问题,恢复原始数据,均衡器被广泛应用于高速串行链路中。此外,温度变化、信道长度等因素的影响也会造成不同程度的信道损耗,为了增加均衡器的适应性,需要实现自适应均衡。

为了实现数据的高速传输,已经提出了多种自适应均衡算法。其中最传统的做法是发射端直接发送PAM4 信号[2-3],利用接收端多级固定的CTLE 电路和多抽头的自适应均衡器进行调节。但是随着数据传输速率越来越高,对均衡强度的要求也越来越高,导致传统做法中抽头数量也越来越多。Saber 等[4]提出了一种DB-PAM4 信号的传输方式,发射端直接产生DBPAM4 信号用于传输,DB-PAM4 信号所需的带宽是PAM4 信号所需带宽的一半,因此对于接收端均衡有一定的改善,但其信号相较于PAM4 信号有-6.3 dB的裕度损失,因此该方式只适用于信道损失较小的光通信中。在接收端,Saber 等[4]的设计只采用了FFE进行自适应均衡,抽头系数多达131 个。Im 等[5]设计了一款112 Gb/s PAM4 长程收发器,当信道损耗大于37.5 dB 时依然能进行有效均衡。但是其在发射端采用四分之一前馈均衡器(FFE)进行预均衡,接收端采用两级CTLE 来均衡输入信号,ADC 采样后输入31抽头的FFE 和1 抽头的DFE 进行数字均衡。整体的均衡方式太过复杂,不同种类均衡器之间没有相互配合。

为了实现接收端较低的均衡强度同时减小信号的带宽,本文提出了一种新的DB-PAM4 产生方式和联合自适应算法。DB-PAM4 信号不在发射端直接产生,而是利用信道本身的滚降特性再经过自适应CTLE 和FFE 的调节产生类似于双二进制处理的效果。同时,联合自适应算法能够充分利用不同均衡器的优势实现信号的可靠还原;发射端的预编码使得信道引入的码间干扰可控,避免了差错传递,保证了算法收敛的可靠性;16 抽头的FFE 和1 抽头的DFE,使得在电路实现时整体功耗较低。仿真结果显示,在112 Gb/s 的数据传输速率下更换不同长度、不同损耗的信道,该算法均能实现双二进制处理且均衡效果显著。

1 基本原理

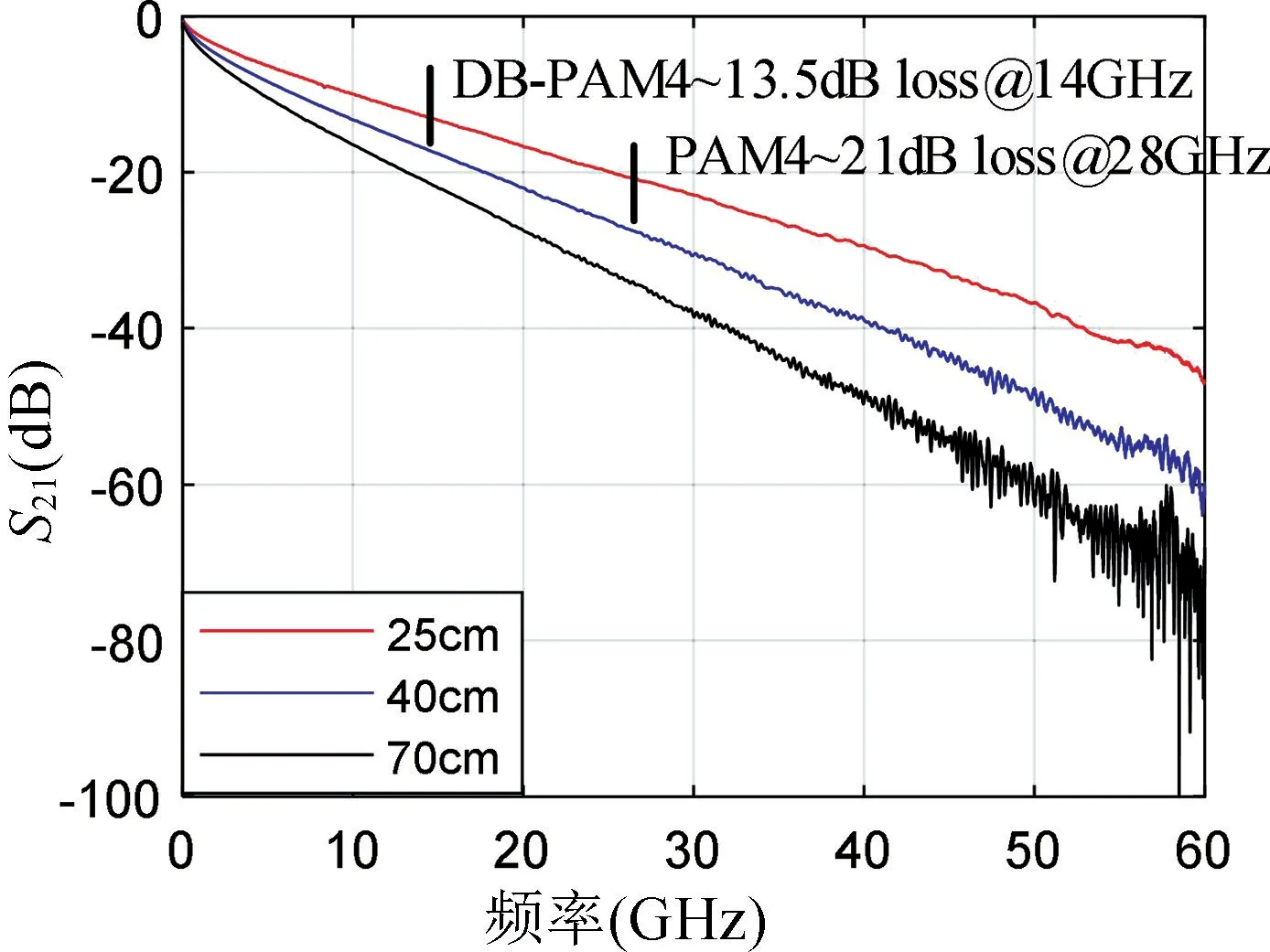

25 cm,40 cm 和70 cm 长背板信道的实测幅频特性曲线如图1 所示。在112 Gb/s 的传输速率下,使用PAM4 信号调制方式其半波特率衰减至少达到-21 dB以上,所引起的码间串扰会使得误码率急剧增加[6],采用传统的均衡器很难均衡如此大的信道衰减。

图1 不同信道的S21传输函数Fig.1 S21 transfer function of different channel

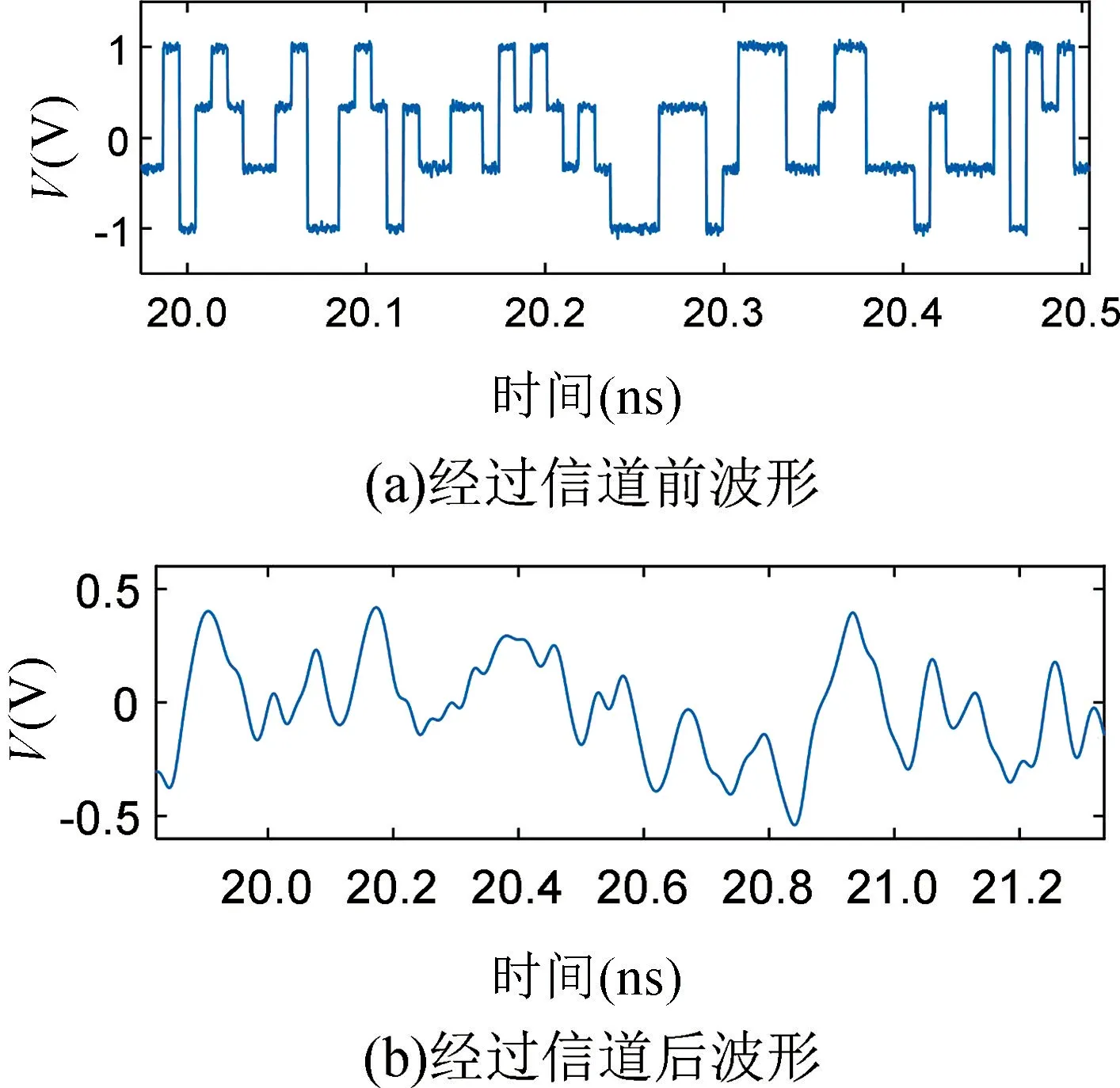

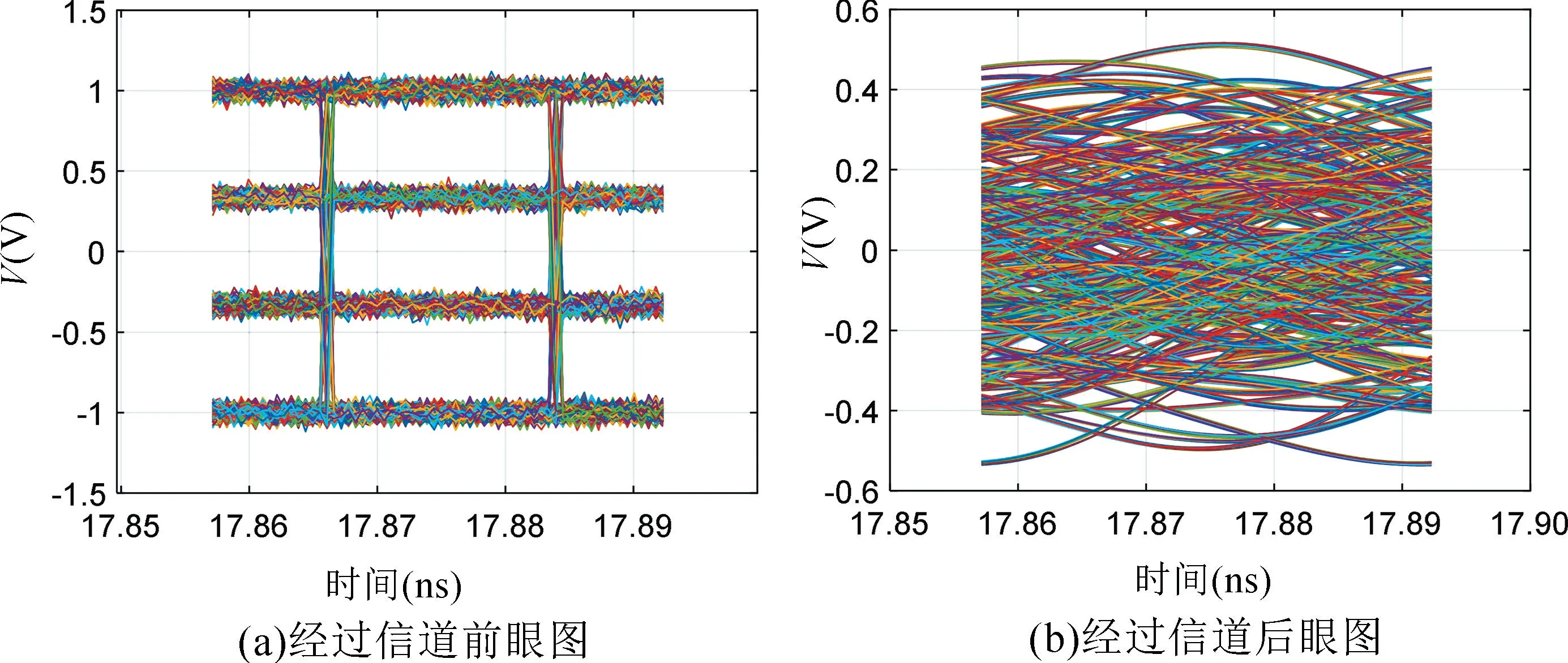

图2 给出了在25 cm 长背板信道下,发射端在一定的电源噪声下发送112 Gb/s 的PAM4 信号,经过此信道后,由于严重的码间干扰,接收端已经无法采集出有效的信号。

图2 经过信道前后数据的波形Fig.2 Waveform of data before and after passing through channel

自适应均衡器的主要作用是在保持信号群延时基本不变的情况下补偿信道的高频衰减,使得在信号的Nyquist 带宽范围内保持信道的理想性。在实际电路中,很难保持28 GHz 带宽的信道维持全通特性,因此使用双二进制(DouBinary)调制方式来减小信号所需带宽就显得至关重要[7]。

1.1 DB-PAM4 信号的产生

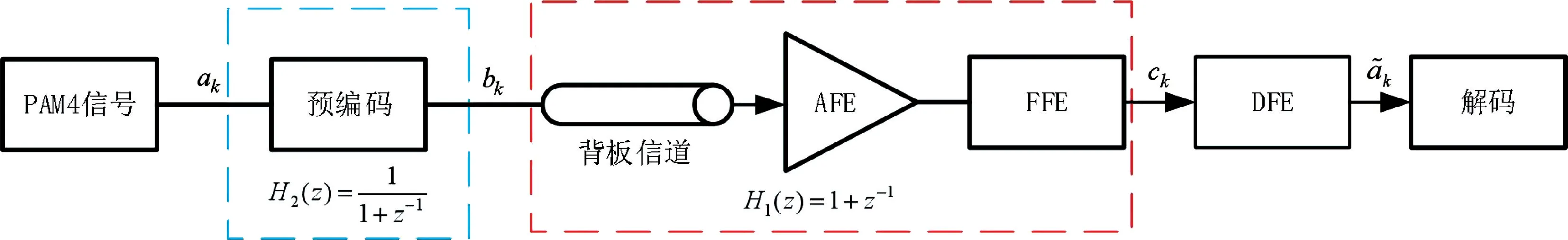

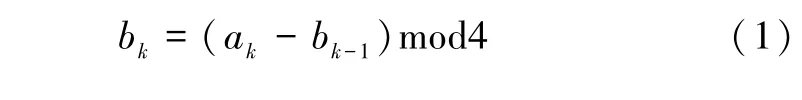

图3 给出了DB-PAM4 产生的线性模型,为了将两个相邻不相关的PAM4 码元变成相关的七电平DBPAM4 信号,减小信号在传输过程中的差错传递,保证接收端信号的准确性,要对原始的PAM4 信号进行预处理[8]。预编码方式为:

图3 DB-PAM4 信号的产生原理Fig.3 Principle of DB-PAM4 signal generation

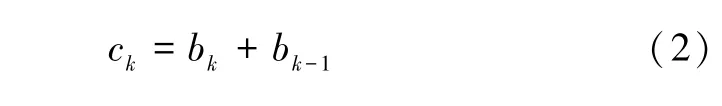

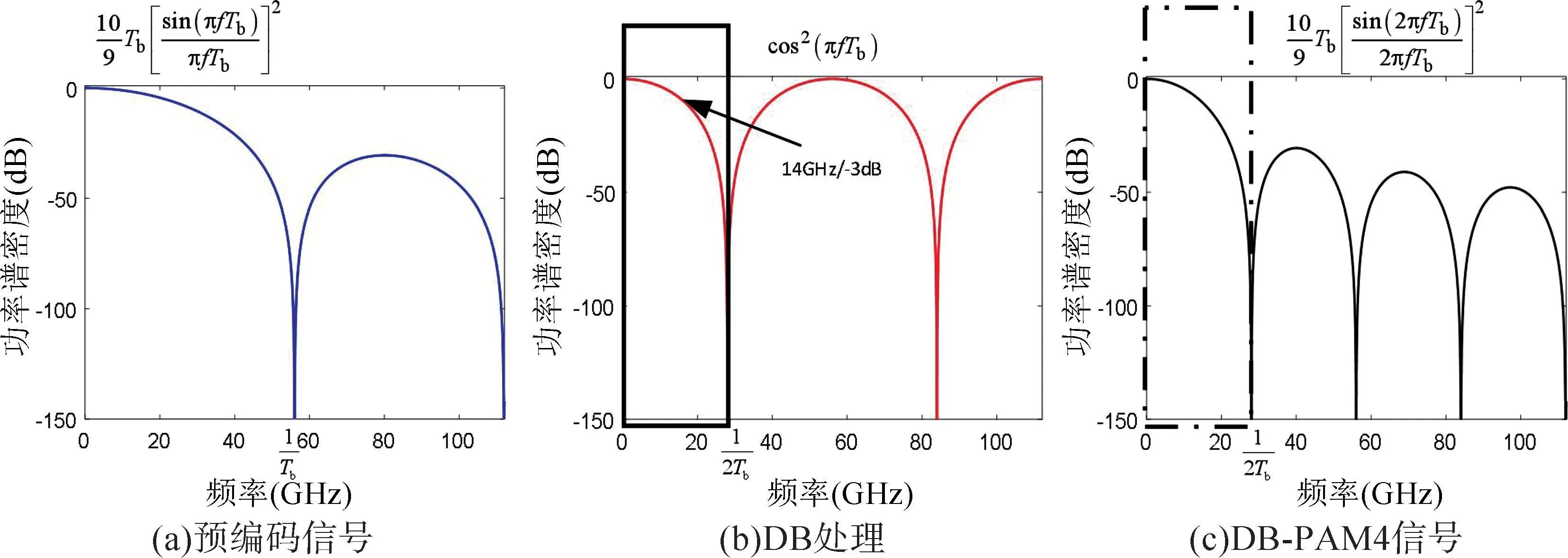

式中:bk是预编码后的信号;ak是原始的PAM4 信号。预编码过后的信号依然属于PAM4 类型信号,其对应的功率谱密度如图4(a)所示。各个电平信号的概率密度不发生变化。在此信号基础上进行双二进制编码,可生成DB-PAM4 信号。编码方式为:

在接收端,传输来的DB-PAM4 信号进行模4 运算就能正确解码出PAM4 信号。保持了收发信号的准确。解码方式是:

双二进制编码将两个相邻的码元相关联,人为引入了可控的码间干扰[10],使得利用信道的双二进制处理成为可能。如图3 所示,预编码对应的z域表达式为:

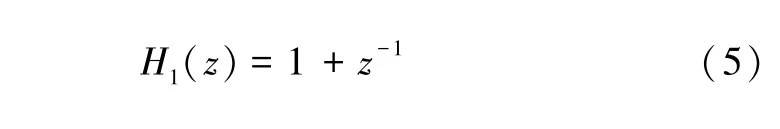

其中的双二进制处理对应的z域传递函数为:

其对应在频域的传递函数为:

式中:Tb为符号周期;1/2 为衰减因子,用于平衡输出端总功率。

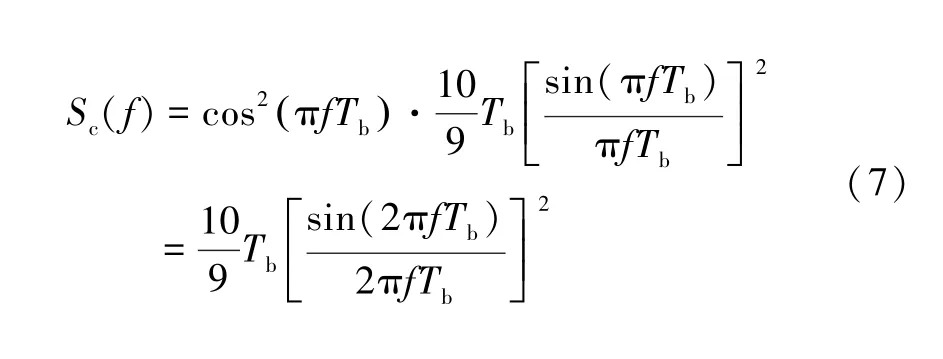

预编码后的PAM4 信号再经过双二进制处理后的功率谱密度为:

但在实际电路中,由于信道是低通的,无法满足在无限的频带范围内保持双二进制处理的频谱方式,如图4(b)所示的DB 处理方式。由公式(8)可知,当只利用双二进制处理主瓣时依旧能保持原始信号中91.2%的能量,且在接收端能够产生DB-PAM4 信号,如图4(c)的虚线框所示部分。基于此,在使用均衡器对信道进行处理时,只需保证在28 GHz 的范围内拟合双二进制处理的过程,无需对整个频带内做处理,图4(b)实线框给出了这种处理方式的具体形式。这种处理方式极大地增强了对于信道带宽的利用率,减小了所需的均衡强度。

图4 DB-PAM4 的产生方式Fig.4 DB-PAM4 generation method

图3 给出了PAM4 信号转换为DB-PAM4 信号的线性模型,将两个不相关的码元变成了相关的7 电平信号,人为在两个码元间引入了可控的码间串扰(Intersymbol Interference,ISI)。虽然电平有7 个,但由公式(2)可知,DB-PAM4 的信号具有相关性。其信号序列中不可能产生{-1,1/3}、{-1,1} 等等这类大的电平跳变。该处理方式保证了接收端正确解码的同时,将原有信号各个电平出现概率进行了重新分配。PAM4 信号中,{00,01,10,11} 产生的概率是均等的1/4。而DB-PAM4 中信号{000,001,010,011,100,101,110} 出现的概率分别为{1/16,1/8,3/16,1/4,3/16,1/8,1/16},这使得大部分信号都处于共模电平附近,相当于将原来的PAM4 信号“挤压” 到直流处,为DB-PAM4 信号的传输提供了极大的优势[10]。

1.2 基于均衡器产生DB-PAM4 原理

图3 展示了在PCB 背板信道中DB-PAM4 的产生方式。在电路中,高速的预编码信号经过信道传输后,在接收端使用自适应的CTLE 和FFE 处理,使得整体的传递函数接近于H1(f)的第一瓣,如图4(b)所示。用这种方式产生DB-PAM4 信号吸收了大量的信道损耗,降低了接收端的均衡强度,使得数字均衡器的抽头减少成为可能,后续DFE 只需要少量抽头就可实现信道均衡。

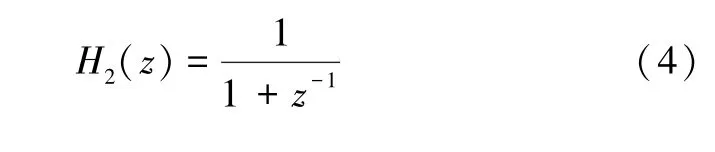

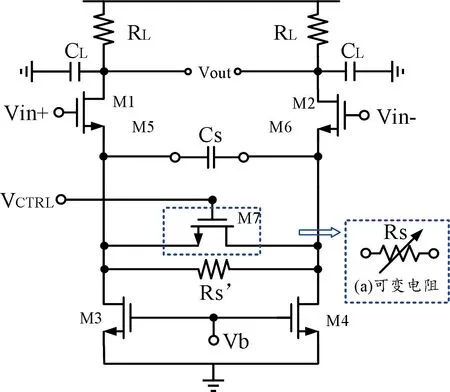

CTLE 属于线性均衡器[11],能够补偿特定频率的高频衰减。在低频处以常数项进行衰减,高频处进行增益,作用刚好与信道特性互补。本文中所使用的CTLE 电路如图5 所示。其传输函数为:

图5 Rs可调的CTLE 电路Fig.5 CTLE circuit with adjustable Rs

式中:gm是放大器的跨导;CL是负载电容;RL是负载电阻;Cs是退化电容;Rs是退化电阻。可以得到CTLE 的直流增益和峰值增益分别为和gmRL。增大退化电阻Rs,CTLE 的直流增益降低,与高频增益的差值越大,均衡效果越强;减小退化电阻Rs,直流增益越大,均衡强度越弱。在本文中,当发射机发射112 Gb/s 的Pre-PAM4 信号时,如图4(b)所示,要保证对信道的DB 处理,峰值频率不应小于14 GHz,否则无法使均衡后的信道频率特性拟合DB 的频率特性;均衡峰值频率越大,对不同信道的适应性越强。因此在本文中CTLE 的均衡点频率在20 GHz 左右,能同时适应不同信道且对CTLE 的要求不是很高。在频率固定时,对于不同长度的背板信道,通过改变直流增益调节信道使其适应DB 处理就可以初步得到DB-PAM4 信号。

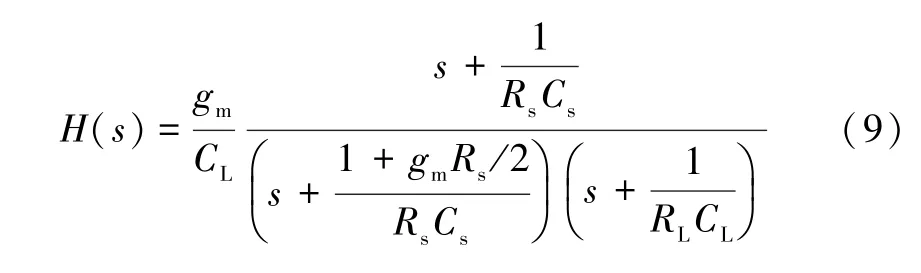

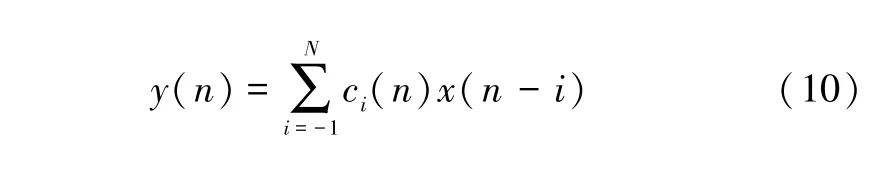

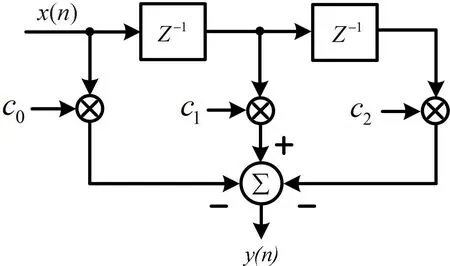

FFE 的作用基本上类似于有限脉冲响应(Finite Impulse Response,FIR)滤波器,它是利用波形本身来校正接收到的信号,能够处理前项和后项的码间干扰。FFE 的输出信号y(n)与输入信号x(n)的表达式为:

式中:ci(n)是FFE 的抽头系数。FFE 的结构如图6 所示。输入信号x(n)经过一系列延迟之后,分别与抽头系数ci(n)相乘,最后经过求和输出。

图6 FFE 结构Fig.6 FFE structure

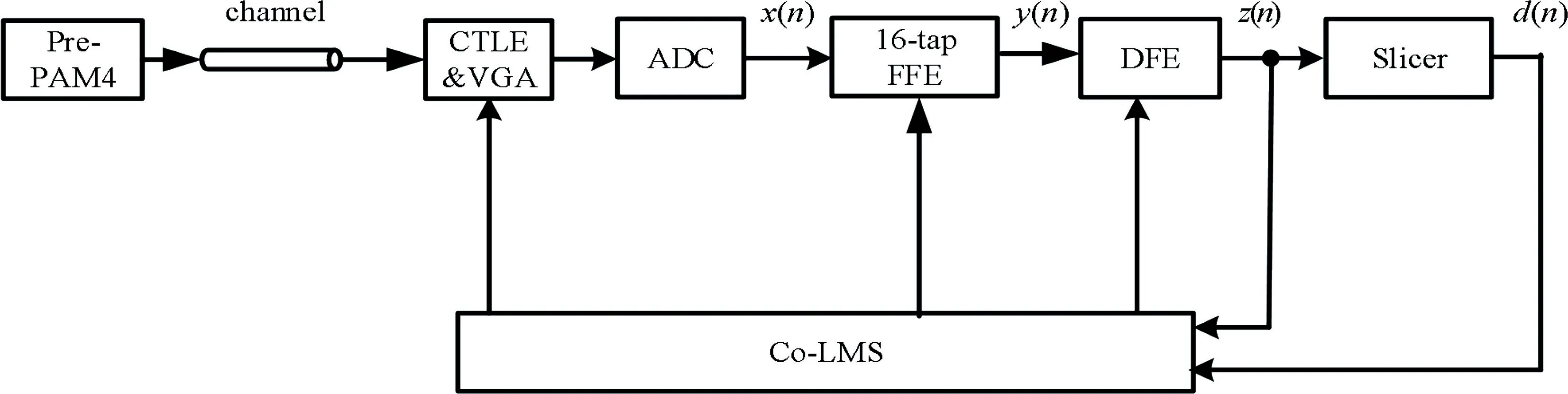

DFE 是一种非线性均衡器,由反馈滤波器和判决器(Slicer)组成,可以消除当前码元对后续码元的ISI,对于信道的反射和波动有较好的补偿作用。但是DFE在同抽头数量下功耗比FFE 大。本文只采用一抽头的DFE 作为均衡,用以减少误差信号。

DFE 的结构如图7 所示,判决器的判决值经过反馈滤波器后,与输入信号作差,直接从输入信号中消除ISI,然后信号从Slicer 的前面输出,输出信号可表示为:

图7 DFE 结构Fig.7 DFE structure

式中:w1,w2,…,wn是DFE 的抽头系数。

2 协同自适应均衡算法

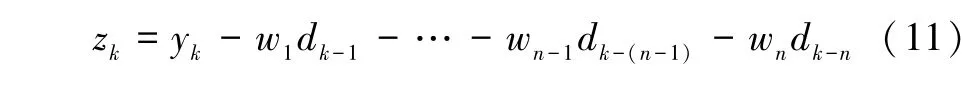

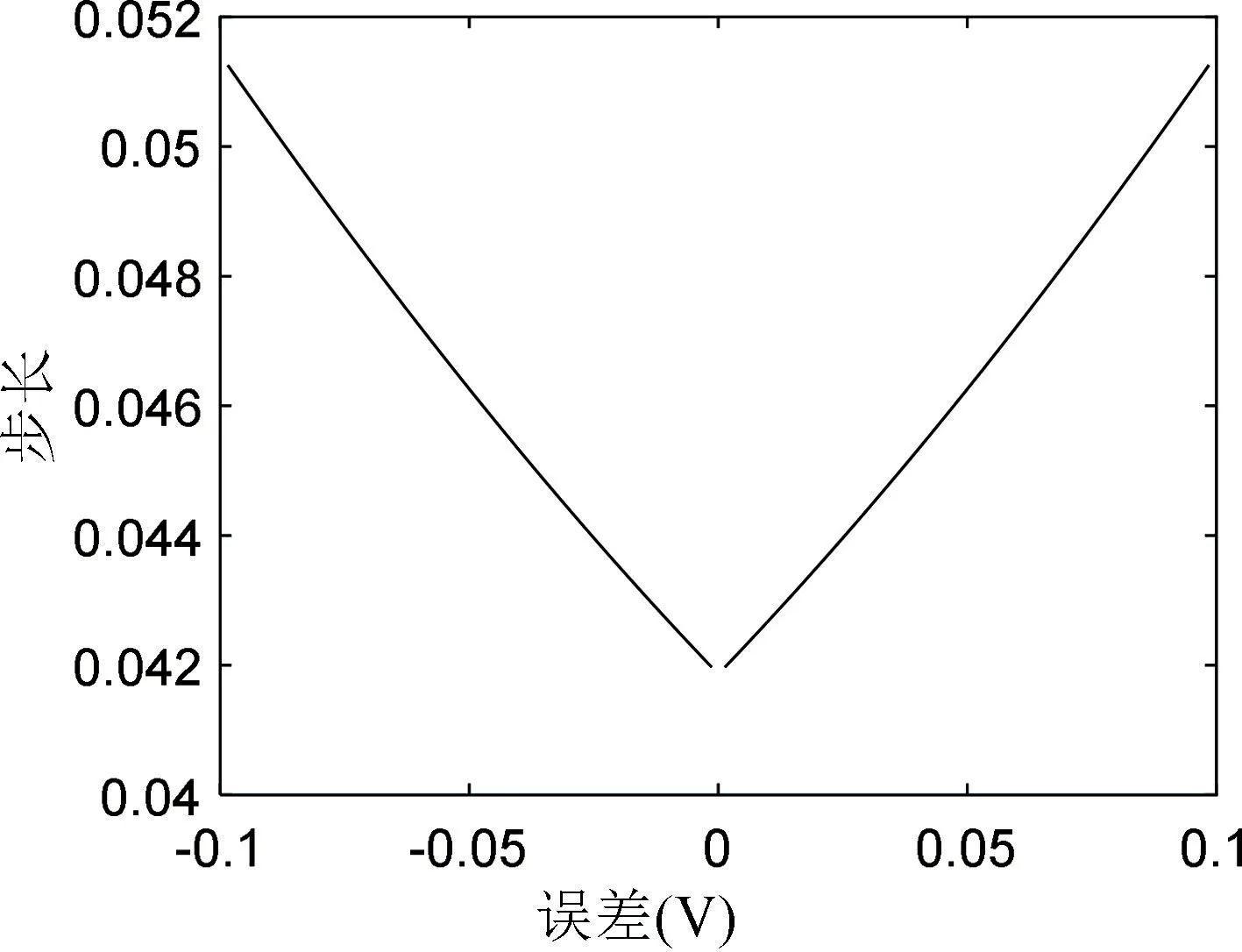

传统的LMS 算法通常只针对单一的均衡器进行自适应调节,这种调节方式保证了算法收敛的准确性,但采用单一均衡器的抽头数量就会大大增加,无法发挥多种均衡器协同的优势[13],而固定的收敛步长使得算法收敛速度十分缓慢,而且为了保持信号的准确传输往往需要训练序列。史航等[14]提出了一种变步长的LMS 算法,该算法虽然解决了传统自适应算法收敛速度缓慢的问题,但是算法整体过于复杂,不适合使用数字电路实现,本文仅用其算法预估联合自适应仿真中的步长大小。其算法公式为:

式中:μ(n)是适应算法的步长;e(n)为FFE 输出值与理想信号的误差。

在改进的变步长LMS 算法[14]和传统的基于单一滤波器的LMS 基础上,本文提出了一种协同自适应均衡算法(Co-LMS),其采用CTLE、FFE 和DFE 协同工作,利用不同均衡器的优点共同解决接收端信号质量差的问题。多种均衡器相互协同的方式使得算法快速收敛的同时也让自适应算法有较强的鲁棒性,在整体上利于数字电路的实现。即使将步长μ设置得较大,DFE 均衡器的强判决也能够使得抽头系数收敛于LMS算法维纳最优解附近,算法整体的收敛速度大大提升而不会遗漏关键信息。

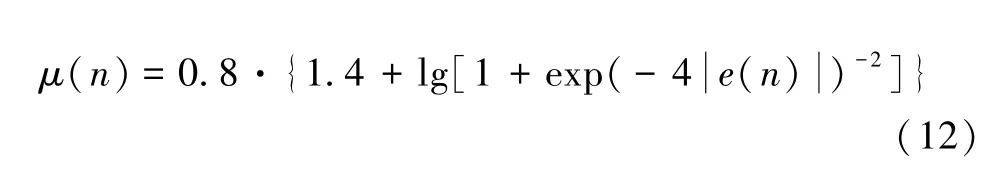

算法原理如图8 所示。其中,用DFE 的判决值作为理想信号,与DFE 输出之差作为整个算法的误差来源。DFE 的输出接近于理想信号且同时带有信道的特性,作为自适应调节信号的输入,能够保证误差信号的相对平稳,利于抽头系数收敛。Slicer 判决为一种强均衡,将DFE 输出数据符号化,避免了噪声引入的误差,在误码率较低情况下,能够代替外部的训练序列,提高信号的传输效率,但如果一开始误码率较高,抽头系数就会朝着错误的方向收敛。为了保证输出信号的准确性,就要保证CTLE 的退化电阻Rs和FFE 的抽头系数快速达到稳定。因为Co-LMS 算法只需要将一种类型的均衡器在特定信道中达到最优解,即可保证算法整体的鲁棒性。故本文将协同自适应均衡算法的收敛期望定在DFE 上,使DFE 抽头系数在稳定时达到维纳最优解,而FFE 的抽头系数只需要在其维纳最优解附近就不会影响接收端信号准确性。基于此,FFE以较大的步长μ来提高算法收敛的速度,DFE 以较小的步长μ来减小误差,保证输出的准确性。改进后的算法公式为:

式中:z(n)为DFE 的输出;y(n)为FFE 的输出值;W(n)为DFE 的抽头系数值。由式(13)可知,抽头系数越多,能够处理的码间干扰位数越多,相应地功耗和算法复杂度也会增加。DFE 只能消除码间干扰的后标分量,其功能与FFE 相重叠,且作为Co-LMS 算法的最优解本身制约较多。本文使用DFE 主要用于改善信道畸变和信号反射问题,减小算法的剩余误差,1 抽头的DFE 就可满足功能需求。为了平衡功耗和均衡强度,本文采用了16 抽头的FFE 和1 抽头的DFE 进行数字均衡。

3 仿真验证

为了对算法进行验证,在MATLAB 中建立了如图3 所示的收发机系统。包括发射机、接收机、信道和译码器。

发射机输出眼图如图9(a)所示,发射机产生预编码之后的pre-PAM4(bk)信号,其速率为112 Gb/s,经过抖动时钟采样后形成波形输出,其电源噪声方差为0.03。如图9(b)所示,经过信道后,信号幅度降低,眼图完全闭合。利用该收发器模型,先进行变步长算法的仿真分析,将图8 中的CTLE 固定,进行32抽头的FFE 仿真,无DFE 均衡器。得出的剩余误差和步长关系如图10 所示。

图8 协同最小均方算法原理Fig.8 Principle of Co-LMS algorithm

图9 经过信道前后眼图Fig.9 Eye diagram before and after passing through the channel

图10 变步长算法的误差与步长关系Fig.10 Relation between error and step size of variable step size algorithm

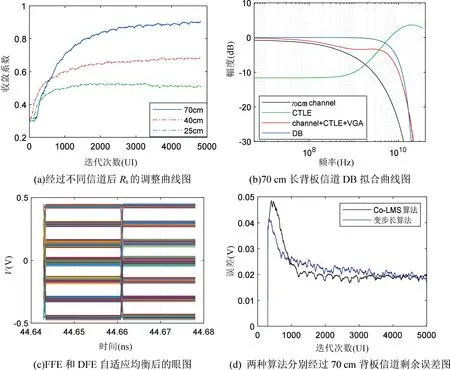

由图10 可知,最大误差为0.0985,最小误差为0.0013,步长范围是[0.052,0.042]。接下来对协同自适应均衡器进行行为级仿真,在Matlab 中搭建的行为级仿真模型如图8 所示,仿真的数据长度为10000个UI(单位时间间隔),以变步长FFE 所得步长分析为参考,FFE 步长取变步长的最大值以保证收敛速度,DFE 取误差最小值左右用以减小系统稳定时的剩余误差。CTLE 的步长由CTLE 电阻阵列所决定。故联合自适应算法中CTLE、FFE 和DFE 的迭代步长分别取0.15,0.05 和0.005,CTLE 的初值设置为0.3,峰值频率值设定在20 GHz。在不同信道下CTLE 收敛曲线如图11(a)所示。可以看出,在不同尺寸信道中该算法依然能够很好地收敛,算法的鲁棒性较强。在70 cm 长的背板信道中,收敛后的CTLE 系数保持在0.78左右,所调整得到的Rs电阻值为670 Ω。如图11(b)所示,以70 cm 背板信道为例,经过CTLE 和VGA 的调节,处理后信道初步满足了DB 处理的功能。

图11 经过信道后算法的自适应调节过程Fig.11 Adaptive adjustment process of the algorithm after channel

FFE 是协助CTLE 产生DB 效果的重要工具,经过800UI 的迭代,FFE 快速收敛,DB-PAM4 的产生引入可控的前项码间干扰,因此设计FFE 要弱化其消除前向干扰的能力。7 个前馈抽头,1 个主抽头和8 个后项抽头,用于解决DB-PAM4 的拖尾。16 个抽头系数分别为 [-0.0053;0.0040;-0.0075;0.0005;0.0059;0.0235;0.0075;1.4817;0.0130;0.0794;0.0225;0.1287;0.0319;-0.1475;0.0381;-0.1362],其中第8 个抽头是主抽头。DFE 的抽头系数稳定后为0.29,能够较好地完成后项码元的均衡和减小系统误差。最终输出数据的眼图如图11(c)所示,6 个眼睛能够明显张开,产生7 电平的DB-PAM4 信号。联合自适应算法与变步长算法剩余对比如图11(d)所示,在112 Gb/s 的数据速率下,联合自适应算法1500 个UI后达到稳定,收敛的时间小于27 ns,系统稳定后,剩余误差为0.02 V 左右。变步长算法采用固定的CTLE和自适应的FFE 均衡器,在2000 个UI 处接近收敛,剩余误差为0.02 V,两者稳定后的误码率均为0。与变步长算法相比,联合自适应算法收敛速度更快,且在算法设计上更加简单。

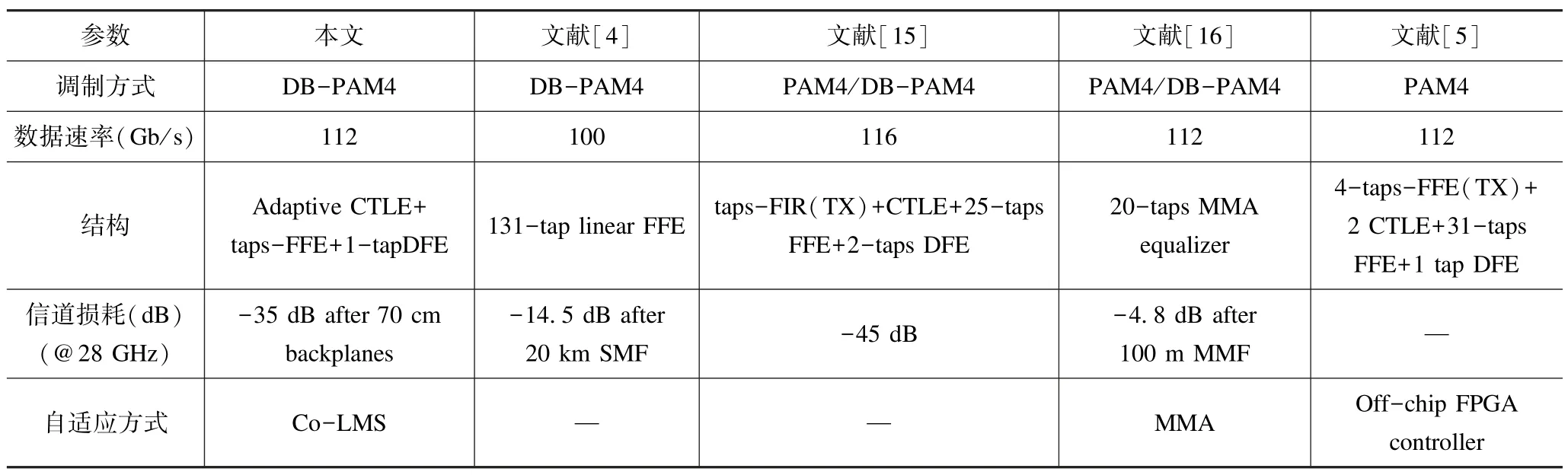

将联合自适应算法所设计的均衡器与其他文献提出的不同算法的均衡器相比较,结果如表1 所示。Saber 等[4]和Zuo 等[16]提出的设计均采用DB-PAM4的传输方式,由于采用光纤通信,信道损耗小,单种多抽头的自适应均衡器就可完成信号处理,对于均衡的难度不是很大。Lacroix 等[15]和Zuo 等[16]两篇文献均采用PAM4/DB-PAM4 双模接收机构架,但Lacroix等[15]提出的各种均衡器之间相互独立,均衡复杂。Im等[5]提出的设计采用PAM4 信号,但其采用的多种均衡器均由外部的FPGA 模块驱动,自适应处理复杂。本文所采用的联合自适应算法在较大的信道损耗下处理同速率数据所需抽头数更少,充分体现了联合自适应算法的优越性。

表1 本文与其他文献对比Tab.1 Comparison of this article with other documents

4 结论

本文设计了一个基于背板信道的DB-PAM4 自适应均衡器。该技术利用DB-PAM4 的相关码元优势,在信道传输时引入可控的码间干扰。相较于传统信号传输方式,DB-PAM4 的产生能够吸收信道损耗,减少所需的信道带宽,降低均衡强度。自适应的CTLE和FFE 能够根据信道变化自动调节均衡强度,以适应对应的DB 处理功能。联合自适应算法使用DFE 的判决输出作为理想信号,不需要传统算法的训练序列,减少了算法的复杂度,提高了信号的传输效率。CTLE、FFE 和DFE 相配合,加快了收敛速度,提升了输出信号质量。仿真结果显示,在112 Gb/s 的数据速率下更换不同损耗的信道,该自适应均衡器均能起到显著的均衡效果。与传统的自适应均衡器算法和变步长算法相比,该算法下所需的均衡强度大大降低,均衡器的抽头数量更少,更利于数字电路实现和降低功耗。在今后传输速率进一步提升时优势更加明显。