红外探测器芯片表面应力释放技术比较研究

2022-09-09段晓丽徐步陆

段晓丽, 徐步陆

(1. 河南省安阳市高级技工学校, 河南 安阳 455000;2. 上海硅知识产权交易中心有限公司, 上海 200030)

0 引 言

五十多年来,碲镉汞(HgCdTe)红外探测技术和产品持续发展,在民用、工业和航天、气象等领域得到广泛应用[1-2]。碲镉汞材料由于其接近100%的量子效率,以及从近红外到甚长波全波段的极广的应用范围,与硅材料在微电子领域的地位类似,碲镉汞材料在红外探测领域中同样树立了绝对的优势地位。目前,随着半导体制造技术的发展,光学图像传感器(CIS)、红外焦平面探测器也开始出现“背照式”、“前照式”等多种结构,性能和功能也朝着高灵敏、低噪声、双多色、大面阵、信号处理一体化集成的下一代焦平面探测器方向不断前进。红外焦平面探测器可分为制冷型和非制冷型两大类,它们用途不同、性能不同、结构不同,成本也不同。其中,制冷型红外焦平面探测器温度分辨率和灵敏度高、探测距离和识别距离远,在探测率、噪声等效温差等反应灵敏度的指标上同样大幅优于非制冷,主要应用于科学研究、工业检测、宇航、防务等领域的高端仪器装备[3-4]。这种红外焦平面探测器芯片的发展方向是大面阵规格、小像元尺寸,采用的晶圆工艺已经开始由6英寸(150 mm)转向8英寸(200 mm)。2017年,一款面阵面积为1 280 μm×1 024 μm,中心距为25 μm的百万像素级的碲镉汞凝视焦平面探测器芯片被公布出来。2019年,上市公司高德红外公开了一款1 280 μm×1 024 μm规模、12 μm像元尺寸的制冷型探测器芯片。

红外焦平面探测器芯片最常见的结构是,通过倒装焊重填填充胶方式,连接碲镉汞外延片和读出电路。这类红外芯片在生产测试和应用寿命周期内,会往复经历60~80 K的工作温度与室温之间宽域温度循环冲击。由于组成探测器芯片的几种组件材料热膨胀系数不同,必然产生应力、应变,而且运输、使用中也不可避免有震动等不规律外部冲击。因此,在生产中残留的芯片边缘瑕疵在上述冲击,以及加工应力残留等因素的影响下,芯片可能产生裂缝从而导致碎裂,材料界面也因裂缝产生、生长引起分层等失效现象[5]。这种失效会导致相应区域成像失败,而且失效过程不可逆,最终致使昂贵的探测器芯片无法维修而报废。因此通过恰当的情报技术研究方法,探明前人在此领域的工作成果,并进行研究比较,提炼总结,提出新的技术思路与方案,无疑可产生具有高性价比的现实技术和经济价值。

1 探测器芯片应力失配专利技术路径研究方法和过程

红外焦平面探测器芯片,是作为工业级中高档产品向专业用户提供。基于新颖性、创造性和实用性,芯片制造方及整机厂商对芯片产品的设计和生产不断提出新的技术方案,专利的申请则更能保护企业知识产权和商业利益。同时,这类由生产催生出的专利提供的技术路线、方案,更有利于真实产品的技术瓶颈突破和工业量产实现[6]。因此,本文主要通过对专利文献知识的挖掘,研究前人红外焦平面探测器芯片方面的技术解决方案,同时在研究过程中提出了自己的技术方案。

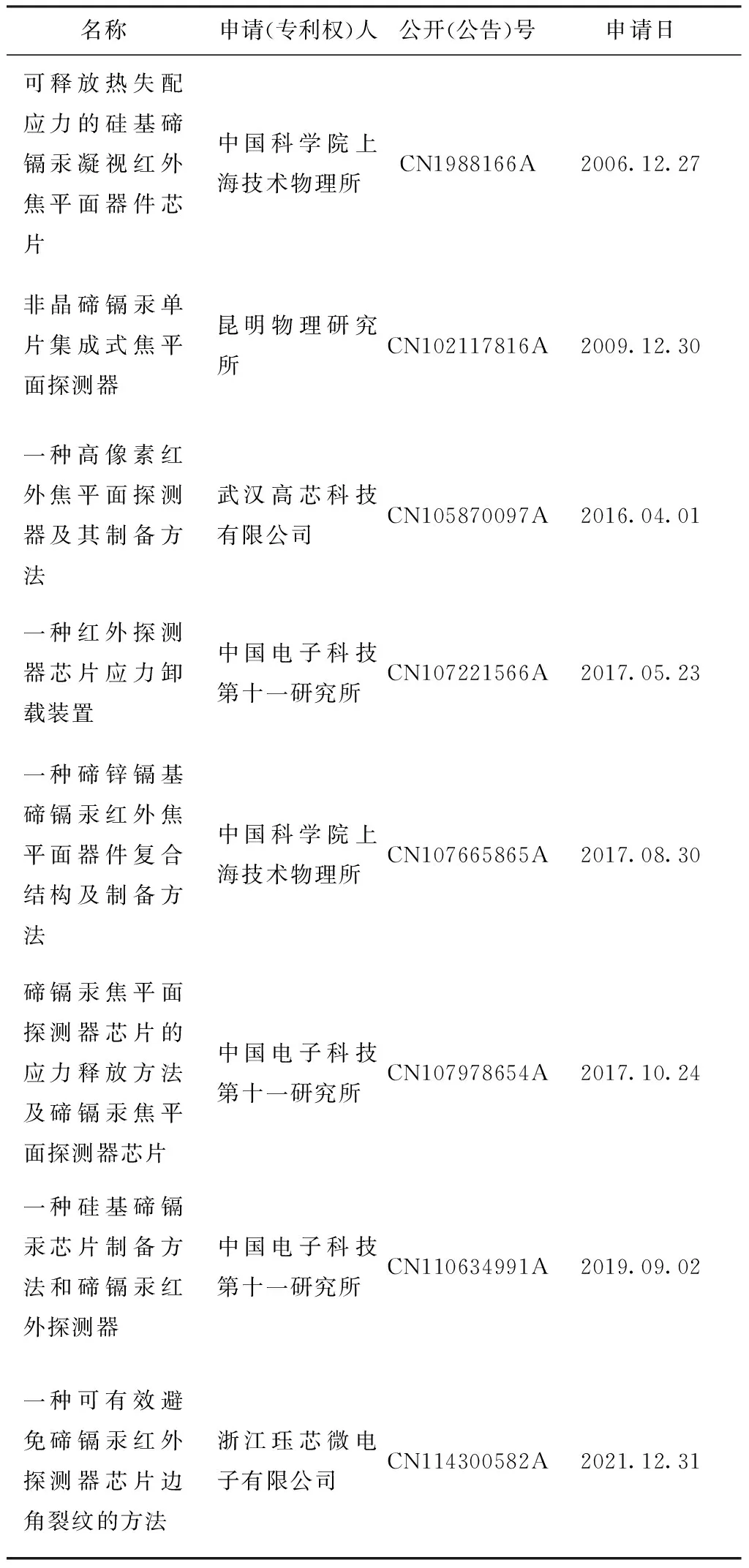

本文专利文献检索采用国家知识产权局知识产权出版社的中国知识产权网信息服务系统。专利检索方法为限定国际专利分类,以及限定中英文“红外焦平面探测器芯片”和“应力(释放、消除)” 组合关键词为检索策略。专利检索截至日期为2022年3月31日前公开(公告)专利,检索时间为2022年4月。检索分析专利类型包含发明(美国专利含申请和授权专利,中国专利含公开和授权公告)和实用新型,不包含外观专利设计。最后,经数据清理、去除噪声后获取八篇价值相对较高的发明专利,详见表1。

经过对表1所述专利包所载技术实施方案研究发现,这专利的申请(专利权)人的确是红外焦平面探测器芯片和系统的主要供应商。这反映过去的十五年中,这些行业领先者在此领域都面临过恶劣环境下芯片热失配失效的共性技术难题。各单位不断进行技术创新,其技术方案新颖、实用性程度高。整体而言,国内外对探测器芯片应力失配问题处理的研究,主要有三种技术解决路线。技术路线一,采用基板刚性补强芯片,如CN107221566A、CN107665865A、CN102117816A。技术路线二,采用高分子材料贴附缓解芯片应变,如CN110634991A、CN105870097A。技术路线三,在芯片加工过程中晶片表面设置应力释放图案,如CN1988166A、CN107978654A、CN114300582A。三种技术路径各有好处,前二种方法的思路是芯片加固,增加了辅助结构材料,制造工艺相对简单,器件整体更复杂。第三种方法的技术路线不改变器件总结构,通过在芯片上设置释放图案来释放芯片应力。方案分为设置应力释放点、应力释放槽和应力释放环等三种,下面进行分析。

表1 探测器芯片应力失配高价值专利文献列表

2 三种专利技术分析

前述“在芯片加工过程中表面设置应力释放图案”的技术路线,根据芯片表面应力释放的目的、思路不同,采取了应力释放点、应力释放槽和应力释放环三种方法。CN1988166A、CN107978654A、CN114300582A中的这些方法充分利用了微电子精细加工设备和能力,并同步开发了产品制造工艺。实施前,要控制工艺加工精度,对可能带来的有效光敏源面积、探测效率的损失进行全面评估、综合设计。文中诸图引自相应的说明书附图。目前,红外探测器像元间距已经缩小至10 μm以内,阵列规模越来越大,因此需要根据实际需求选择合适的技术方案。

2.1 应力释放点方案

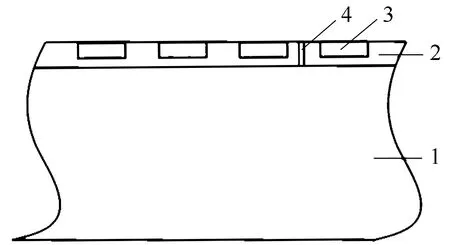

应力释放点方案,作为硅衬底与碲镉汞外延薄膜之间热失配问题的解决办法,由CN1988166A提出。该方案首先在碲镉汞外延薄膜上形成的光敏元列阵上,每10~20个光敏元间设置隔离区;然后,通过等离子体干法刻蚀在隔离区面上形成的局部应力释放小孔。小孔深度为碲镉汞外延薄膜的厚度,小孔内表面置有钝化层,小孔尺度小于有效光敏元面积的1%。

图1、图2是应力释放点方案的纵剖面和俯视结构示意图。图中,1为硅衬底,2为碲镉汞外延薄膜2,3为光敏元列阵,4为小孔。该方案需要在小孔精密加工时严格控制刻蚀速度、时间、深度等工艺参数,最大程度避免周围材料损伤和影响信号收集面。该方案在一种像元数320×240硅基碲镉汞红外焦平面列阵器实测结果为:芯片抗“室温—液氮温度77 K”温度循环冲击能力提升10倍,由10次提升至100次。

图1 应力释放点方案的纵剖面示意图

图2 应力释放点方案的俯视示意图

2.2 应力释放槽方案

应力释放槽方案,作为大面阵凝视型碲镉汞焦平面探测器芯片的应力释放方法,由CN107978654A提出。方案通过采用电感耦合等离子体,在芯片上刻蚀碲镉汞浅沟槽阵列。通过刻蚀速率和时间,控制刻蚀深度小于吸收层厚度,刻蚀宽度小于像元间隔宽度,确保刻蚀浅槽位置介于某两个N形区域之间。该方案的核心是,隔离槽位置和深度的控制,防止引入新的影响因子。图3、图4是应力释放槽方案的纵剖面和俯视结构示意图。实例是一款百万像素级的碲镉汞凝视焦平面探测器芯片,面阵规格为1 280×1 024。中心距为25 μm,刻蚀深度为1 μm~2 μm。单个浅槽为十字形,共计16个。实测结果为:经历多次开关机温度冲击(77 K到室温)未发现芯片碎裂。说明应力释放槽方案对大面阵芯片应力释放起到明显作用。

图3 应力释放槽方案的纵剖面示意图

图4 应力释放槽方案的俯视示意图

2.3 应力释放环方案

应力释放环方案,作为碲镉汞芯片加工缺陷和工作负载中芯片因应力引起裂纹问题的解决办法,由CN107978654A提出。方案采用光刻胶图案保护、去除,通过湿法腐蚀的工艺手段,在碲镉汞芯片成像区周边蚀刻产生至少一圈边框图案的凹槽。这个闭合的边框槽,会将划片时崩边产生的微裂纹隐患有效阻在碲镉汞芯片的有效成像区域外,从而阻断了断裂纹向感光功能核心区扩展。闭合边框凹槽理想的设计宽度为15 μm、正面刻蚀深度为20 μm、背面刻蚀深度为碲镉汞芯片外延层厚度。图5是应力释放环正面刻蚀方案的俯视图。图6是应力释放环背面刻蚀方案的俯视图。图中:1为读出电路,2为碲镉汞芯片,3为有效成像区,4为边框凹槽。该方案需要在边框凹槽加工时,严格控制刻蚀速度、时间等工艺参数,以控制开槽的深度和宽度。实测结果为:在碲镉汞芯片正面开槽后产生裂纹比从84.7%降低至4.85%。双面开槽,良率提升更多。

图5 应力释放槽正面刻蚀方案的俯视示意图

图6 应力释放槽背面刻蚀方案的俯视示意图

3 薄膜沉积紧固带方案

某公司生产的中波640×512/15 μm探测器有效像元率已经达到99.99%[7]。然而,红外敏感材料的某些缺陷,只有在芯片加工工艺过程中,甚至是测试表征后才能凸显。上述三种方案在避免或最小化损失碲镉汞焦平面探测器芯片有效光敏面前提下,考虑到温度循环冲击、残余应力释放等因素,采用离子束干法刻蚀、化学湿法刻蚀等工艺[8-9]实施“减法”,在芯片表面不同位置设置图案缓冲、释放工作中残生的应力破坏,实验结果改进明显。但无论上述三种 “减法型”微加工如何精准,刻蚀工艺中仍不可避免在芯片晶面上产生破坏,引起新裂纹产生的未知风险。因此,受益于半导体微加工工艺进步,本文提出一种“加法型”技术新方案——薄膜沉积紧固带方案。

本方案实施过程是在碲镉汞焦平面探测器芯片制备工序中,选择采用一种机械附着力、硬度以及化学稳定性比较高的材料作为增强薄膜材料[10],在光敏面外的死区之间设计合适的易加工边框图案,通过光刻保护、去除,结合采用溅射方法或真空磁溅射方法、真空热蒸发方法,将薄膜沉积制备添加固化于芯片光学非感光“死区”表面。新沉积的固态膜,作为芯片温度循环应力应变抗冲击的形变缓冲紧固带。工程中可通过有限元仿真、牢固度认证实验等方法,设定合适的边框图案厚度、宽度、形状等几何参数,以及薄膜沉积温度、真空度、转速、沉积速率等工艺参数进行制备加工。考虑到芯片整体尺寸一般为几十微米,薄膜厚度一般控制在低于芯片尺寸两个数量级,如0.5 μm,紧固带可以采用复数线条、矩形带框、间隔线束框等形状,其中以封闭图案最为常见。这种方法实质上等同“(局部)贴膜保护屏幕”。

归一化探测率D*常被用于描述不同红外探测器的性能优劣,比探测率D更客观[11]。D*实质上就是探测器单位面积Ad、单位放大器带宽Δf、单位辐射功率下的信噪比。公式(1)中,NEP为等效噪声功率。探测器性能表征因子NEP是探测率D的倒数,其值越小则探测器的性能越好。

(1)

本薄膜沉积紧固带方案与未实施优化方案相比归一化探测率D*、探测器单位面积Ad、单位放大器带宽Δf、单位辐射功率下的信噪比均不发生变化。因此本方案在带来器件机械性能提升的同时,并未损害器件的电学特性。这一点而言,本方案优于现有其他技术方案。进一步结构优化,可以通过有限元法进行热应力分析来选择合适的薄膜沉积材料。表2是本文所及四种方案的比较。

表2 四种晶片表面设置应力释放图案方案比较

在大面阵探测器芯片制备工艺中薄膜沉积紧固带方案,还具有芯片表面应力监测的作用。由于诸如衬底沉淀相延伸到外延产生孔洞缺陷,这些外延缺陷将在芯片上形成坏点或团簇。工艺上HgCdTe外延材料表面不良率难以完全杜绝,因此测试表征中仍可能发现问题。薄膜沉积紧固带由于生长材料和工艺、形状不同,断裂强度也不同。若后序工艺过程中紧固带断裂,则说明膜层受应力形变过大,从而得知此时该处的应力值。文献记载的几种有限元参考模型中,芯片最大Von Mises等效应力在60 MPa上下[12]。这个应力值可以与计算预知的温度循环中HgCdTe的断裂强度阈值相比,如这个应力值比阈值高,则需调整结构设计或前序工艺参数,或需通过后续工艺调整器件应力分布,以提高器件成品率、膜层均匀性。

4 结 语

本文采用了专利文献挖掘技术,研究了在恶劣工作环境中碲镉汞焦平面探测器芯片失效的解决方案,归纳出基板刚性补强芯片、高分子材料黏附、晶片表面设置应力释放图案三种技术路线。由于微电子加工工艺越来越精细,重点研究了晶片表面设置应力释放图案的三种“减法型”思路的具体工程实现:设置应力释放点、应力释放槽和应力释放环。基于已知工程问题,本文提出“加法型”思路的薄膜沉积紧固带方案工程实现方法。这种新方法与未实施优化方案相比,在不降低器件电学特性的前提下提升了探测器芯片结构稳定性。与三种“减法型”方案相比,取得结构性能提升的同时,不引入新应力风险点。此外,新方法还带来应力实时监测预警功能,及时发现问题、调整工艺或采取规避措施以提高芯片可靠性。今后可以结合探测器芯片由“背照式”向“前照式”的发展,以及晶片材料改变、优化等因素,进一步完善优化。