基于FPGA的核磁共振成像仪通信主控系统设计

2022-09-01王松

王松

(临邑县人民医院,山东,德州 251500)

0 引言

核磁共振成像系统中的主控板既要负责与计算机的通信,又要生成相应的脉冲序列,同时还需对其他模块进行控制。因此,其性能的好坏会直接影响成像效果[1]。在对主控板进行设计时,通常将其绝大多数功能交由CPU执行,但当任务繁重时会大大增加CPU的负担,进而降低整个系统的性能[2-3]。本文所设计的主控板中数据的存储和通信由CPU处理,其余功能均由FPGA所编写的其他硬件模块来执行,这将有效提高整个成像系统的使用性能。

1 主控板的设计

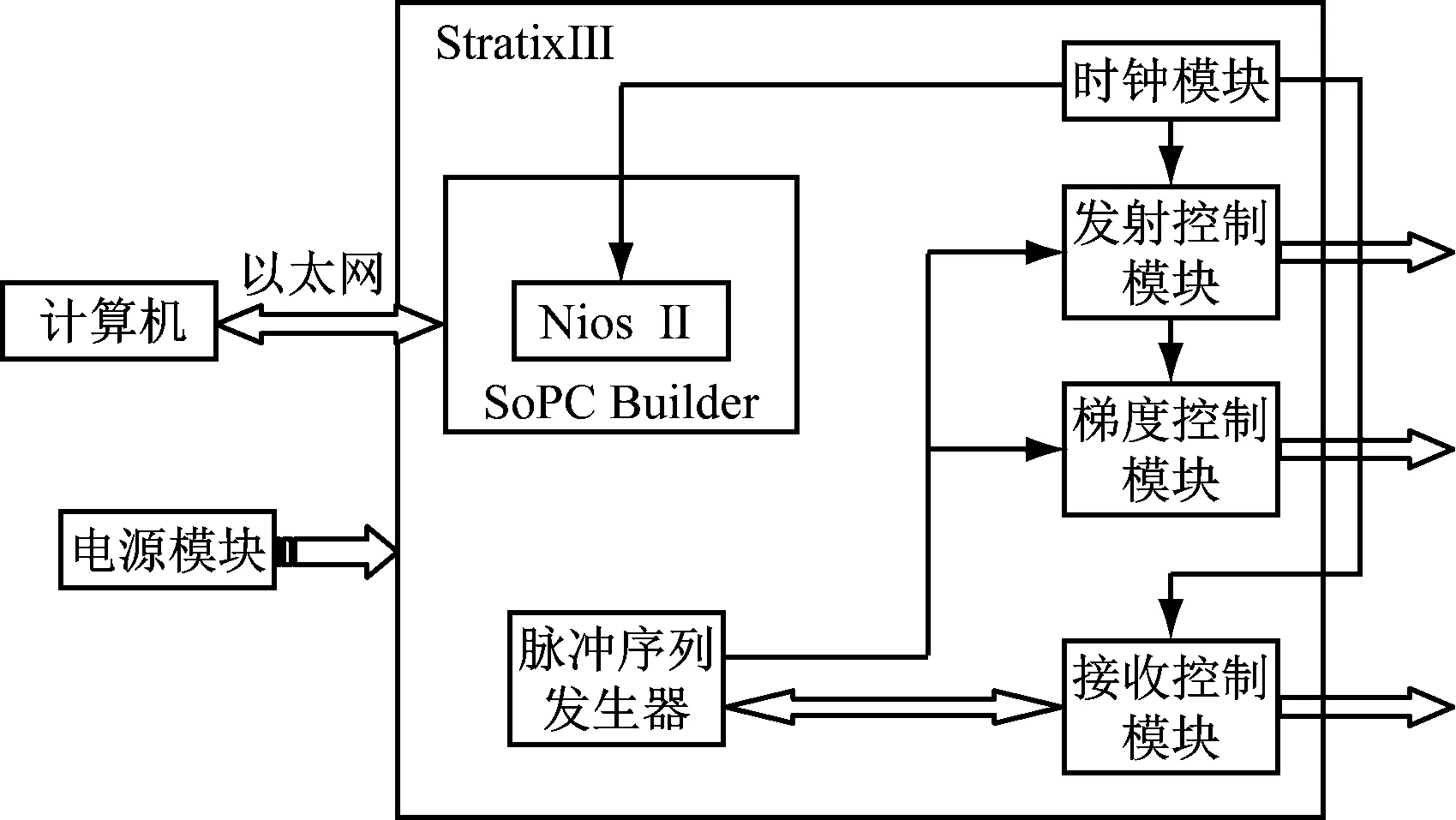

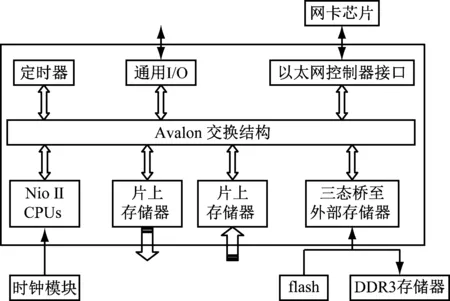

为了满足设计要求,本文选择带有性能较好的FPGA芯片的Stratix系列开发板作为主控板,其整体结构如图1所示。在对主控板进行设计时,主要分为软件设计和硬件设计。在对软件进行设计时,协处理器采用系统自带的NiosⅡ,利用SoPC Builder软件构建基于FPGA上的开发平台,具体结构如图2所示。通过相应的操作系统和协议栈,实现主控板和软件之间的数据传输和通信。将网口所传输的数据存储在RAM中,同时将所收集的数据传输给计算机进行图像处理,通过网线实现与计算机之间的通信,这样可以保证数据传输的速度和稳定性。

图1 主控板整体结构

图2 嵌入式开发平台

在对主控板进行硬件设计时,利用Verilog语言生成相应的控制模块,通过脉冲序列所生成的模块对RAM中的数据进行处理,进而实现对其他模块的控制并生成所需的脉冲序列[4-5]。本文将主控板的功能进行了明确的区分,通过对主控板进行嵌入式设计实现了与计算机之间的通信,通过相应的硬件设计生成了系统所需的脉冲序列,通过该设计可有效降低CPU的运行压力,提升整个系统的运行速度和稳定性,同时还可实现对系统多通道的扩展。

2 通信模块

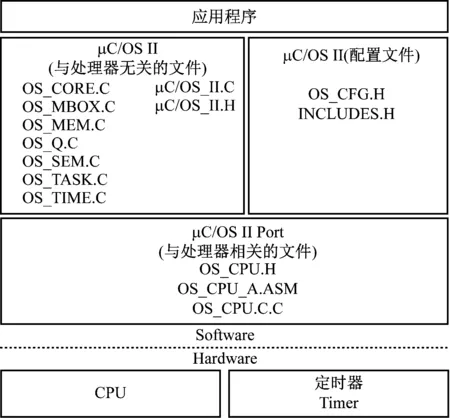

在进行嵌入式设计时,操作系统选用代码公开、移植方便且可裁剪的μC/OS-Ⅱ,其具体结构如图3所示。

图3 文件系统结构

在对其进行移植时需要对OS_CPU.C、OS_CPU_A、OS_CPU.H中与处理器相关的代码进行修改。在对OS_CPU.H进行编译时,主要对于编译器相关的数据和定义进行修改,具体代码如下[6]:

/* This is the definition for Nios II.*/

typedef unsigned char BOOLEAD;

typedef unsigned char INT8U;

……

typedef unsigned int OS_STK;

# define OS_STK_GROWTH 1/* Stack grows from HIGH to LOW memory */

在该文件中还对2个重要函数进行了宏定义,代码如下。其中,OS_ENTER_CRITICAL()和OS_EXIT_CRITICAL()分别为关中断和开中断函数。该函数是进行原子操作的重要环节,在操作时还可调用系统自带的中断函数[7]。

# define OS_CPU_SR alt_irq_context

# define OS_ENTER_CRITICAL()cpu_sr=alt_irq_disable_all()

# define OS_EXIT_CRITICAL()alt_irq_enable_all(cpu_sr)

在对OS_CPU.C进行编译时,主要对堆栈函数进行初始化,同时对系统所用到的Hook函数进行修改。在对OS_CPU.S进行处理时,主要对实现任务的启动和切换函数进行编译,这也是进行系统移植的核心工作。在编译时,主要针对以下函数:OSStartHighRdy()为优先级最高的启动运行函数;OSCtxSW()和OSIntCtxSW()分别为任务级和中断级的任务切换函数。当以上设置完成后还需对系统的时钟进行设置,对定时器的中断行为进行设置,同时还需将其与中断函数进行绑定[8-9]。

将lwIP协议栈(即TCP/IP小型协议栈)移植到本文所用的操作系统上,以实现主控板和计算机之间的通信。由于lwIP协议栈中与编译器和操作系统等相关部分的代码都是独立的且位于同一目录下(.srcarch),所以在进行协议栈的移植时只需对相应目录下的文件进行修改即可。在对与CPU或编译器相关的接口进行修改时,主要针对相应目录下cc.h和pre.h中的数据类型、存储方式等,在修改时要与之前所定义的参数保持一致。

在对操作系统相关的接口进行编译时,主要针对sys_arch.h和sys_arch.c两个文件,主要目的是实现信号量函数、消息量函数、定时器函数和创建线程的函数。本文所用操作系统中也有信号量和消息机制,对系统中的类似函数进行封装处理后即可实现所需功能。除此之外,还有几个函数需进行重新定义,其中包括消息队列结构,通过系统自身的QSQ管理模块即可实现对消息队列的管理,包括创建、删除等操作。在lwIP中每个线程都需有相应的结构队列,由于上文中已经定义了sys_timeout和sys_timeouts结构体,所以只要找到相应线程所使用的指针函数即可。

本文所采用的网络芯片为88E1111以太网收发器芯片,其具体的驱动结构如图4所示。其中,函数1主要实现对芯片的初始化,函数2主要实现对以太网数据包的读取,函数3的主要作用是在进行初始化时对以太网数据包进行发送,函数7主要是对网卡进行初始化,函数8和9的基本功能是进行数据包收发。

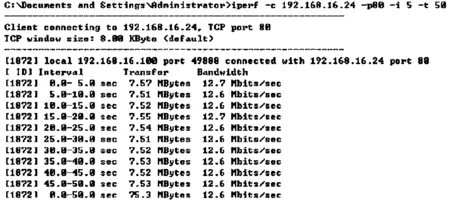

图4 底层驱动程序

当以上程序开发完毕后,对其网络通信进行测试,看所进行的移植操作是否成功。利用Ping命令和iperf软件测试相应协议的工作状态,测试结果如图5所示。观察测试结果发现,lwIP协议在μC/OS-Ⅱ运行正常,由于主控板频率较低,在一定程度上限制了网卡芯片的性能发挥[10]。通过iperf测试可发现数据传输的速率约为12.6 Mbps,完全可满足实际需要,如图6所示。

图5 测试结果

图6 50 MHz工作频率iperf测试结果

3 脉冲序列的生成

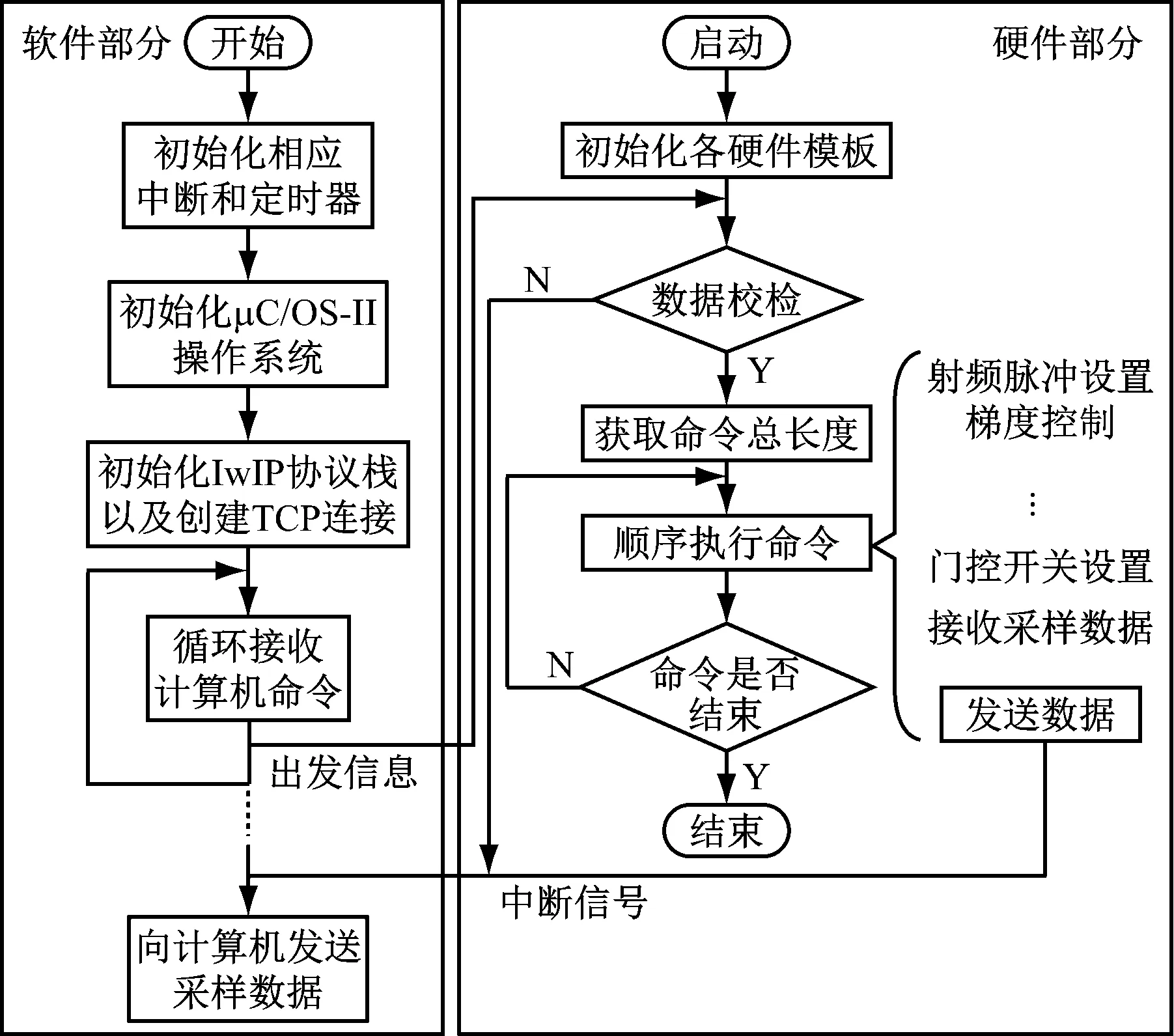

图7为整体功能实现的流程图。其中,通信模块已实现了其主要功能,后续还需主控板对数据进行处理分析并生成对应的脉冲序列,这也是本文硬件设计所需解决的主要问题。要想生成对应的脉冲序列,首先需要对硬件中的各个模块进行初始化,当软件收到相应命令后发出信号通知脉冲序列生成模块进行数据的读取,后续还需对所有的数据进行校验,以保证数据的有效性。最后得到整个命令的总长度并执行命令,根据所得命令对各个模块进行配置,进而生成相应的脉冲序列达到最终目标。

图7 整体功能实现的流程图

图8为利用Modelsim软件对硬件进行仿真的结果,观察发现其幅值和时序均达到了预期目标。图9为示波器所采集的图像结果,观察可发现测试所得结果与仿真结果基本一致,可满足最终的成像要求。

图8 硬件仿真结果

图9 示波器采集图像

4 总结

本文主要对核磁共振成像系统的主控板进行设计,通过软件实现了处理器和计算机之间的通信,利用硬件得到了系统所需的脉冲序列。通过对所设计的系统进行仿真和测试发现,通过这种设计可增加系统成像的精度和稳定性。本设计在开发过程中得到了临邑县人民医院信息中心技术人员的大力支持和帮助,特此鸣谢。