三维光子集成芯片的进展与挑战(特邀)

2022-08-29尹悦鑫许馨如丁颖智姚梦可曾国宴张大明

尹悦鑫,许馨如,丁颖智,姚梦可,曾国宴,张大明

(吉林大学电子科学与工程学院集成光电子学国家重点实验室,长春 130012)

0 引言

以光为媒介的通信系统在光纤器件上得到了广泛的应用,随着5G 网络、物联网、数据中心的提出,对短距离通信提出了更大的容量与更低的功耗的要求[1-4]。光子集成芯片(Photonic Integrated Circuits,PICs)具有高度集成化的特点,可实现复杂片上光网络、拓展通信带宽、降低通信成本[4-6]。不同的材料平台,如硅光子平台(Silicon Photonics,SiPh)[7,8]、氮化硅平台(Silicon Nitride,SiN)[9,10]、Ⅲ-Ⅴ族材料平台[11,12]、二氧化硅平台[13,14]和聚合物平台[15,16],均已实现了多种功能的光子集成芯片。例如,硅光子平台由于其高折射率差、互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺兼容的特点,是实现紧凑器件和大规模生产的光子平台。然而,受限于光刻窗口,目前可以实现的最大规模的光交叉仅为64×64[17],不能满足日益增长的通信容量与互联端口数目的需求。为了进一步提高集成光子集成芯片的集成度,拓展光子集成芯片的功能,人们将目光放在了三维光子集成芯片(Three Dimensional Photonics Integrated Circuits,3D-PICs)上[18-21]。三维光子集成芯片的概念起源于三维电子集成芯片,在集成电路中将电路进行多层堆叠,通过硅通孔(Through-Silicon-Vias,TSVs)实现层间的控制,多层堆叠的集成电路不仅可以实现高密度的集成电路芯片,TSV 的引入还可以极大降低走线的复杂度和长度,降低由于连接线所引入的功耗、延时,进而扩大通信容量带宽,降低噪声[21]。在光子集成芯片领域,通过光通孔(Through-Silicon-Optical-Via,TSOV),即层间转换器,实现多层光子器件之间的互联。层间的波导交叉相比层内的波导交叉呈现出更低的损耗和串扰,为实现更大规模光子集成器件提供了可能。除了集成度的提高,通过晶圆键合、气相沉积、旋涂、磁控溅射方式,可以实现多种材料体系光子器件的单片混合集成,对光子集成芯片功能的拓展也提供了可能,为实现片上光源、传输、路由、探测提供了可选方案。

本文将围绕近年三维光子器件的发展与应用展开讨论,包括三维光子集成芯片的起源与其优势、制备三维光子集成器件的方法、三维光子集成芯片的材料选择与发展经过,结合制备的器件与应用,阐述了三维光子集成芯片的优点以及面临的挑战。

1 三维光子集成芯片的制造方法

三维光子集成芯片的制备,要确保引入的工艺与已有的工艺兼容。以硅光子平台为例,高温工艺步骤的引入使得原本的掺杂区形成横向扩散,引起有源器件的失效,因此三维光子集成芯片的材料与工艺需要经过严格的选择与优化。到目前为止,已有的三维光子集成芯片的材料选择主要包括硅光子平台[19-32]、氮化硅[33-42]、聚合物[43-56]、Al2O3[57-61]、Ⅲ-Ⅴ族化合物[62-64]等,根据材料不同,制备工艺也有区别,目前主流的两种方案是晶圆键合方法和气相沉积方法。

1.1 键合方式

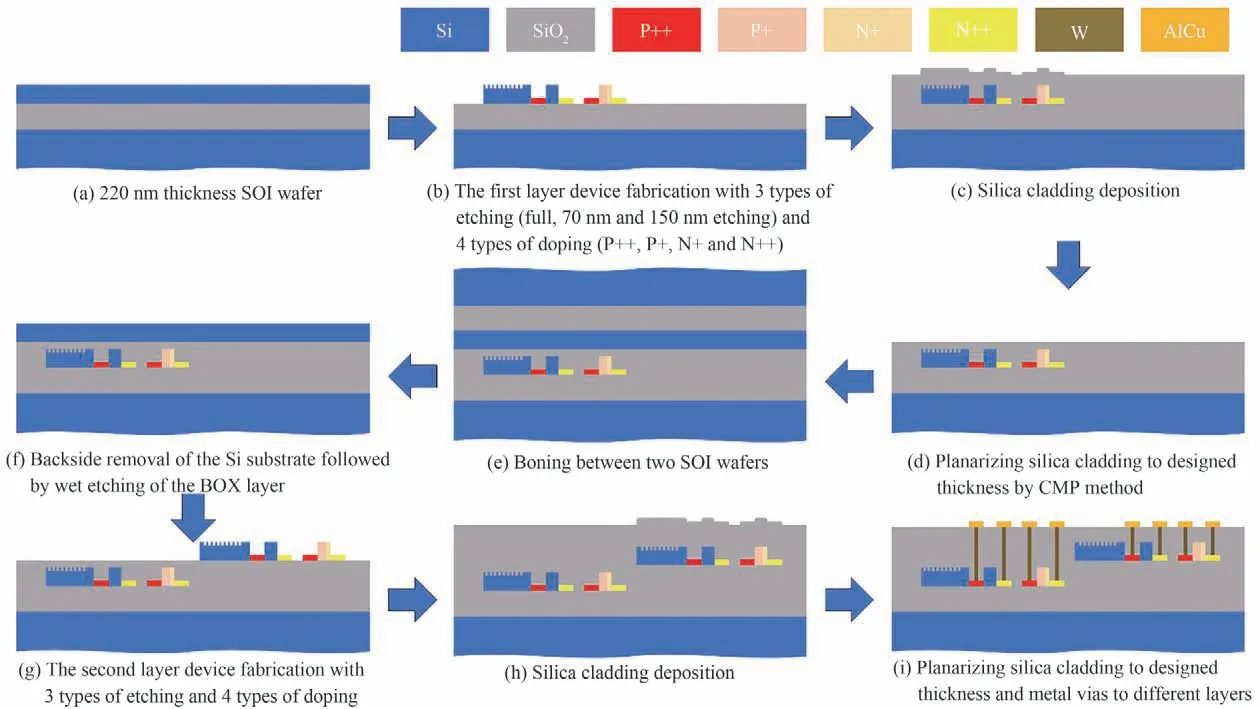

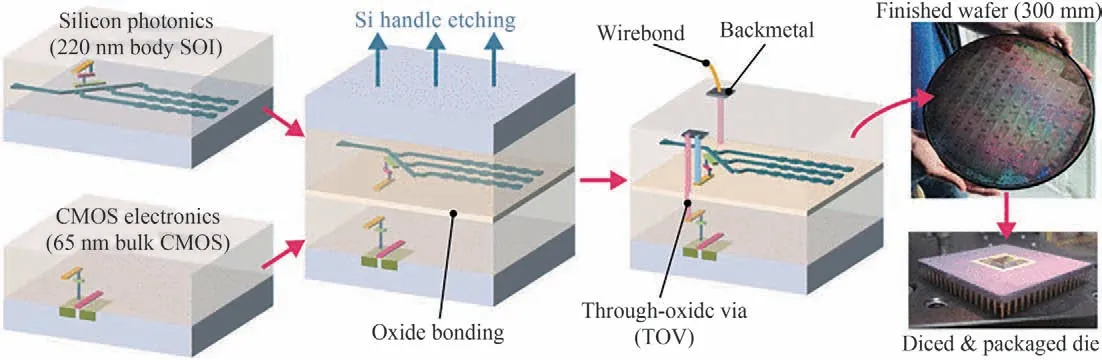

晶圆键合是指两块同质或者异质的晶圆,通过化学和物理的作用,紧密结合在一起的制备方法。在硅光子平台中,通过晶圆键合的方式制备三维光子器件的流程如图1 所示。在完成如图1(a)~(c)所示的第一层工艺之后,通过化学机械抛光(Chemical Mechanical Polishing,CMP)将二氧化硅层减薄到所需的厚度,再经过晶圆键合(图1(e)),将经过处理的另一张晶圆与第一张制备好光子器件的晶圆键合在一起,经过腐蚀方式除去硅衬底和埋氧层(Buried Oxide,BOX),如图1(f)所示。接下来在第二层硅上制备波导器件,如图1(f)~(h)。最后,CMP 磨平二氧化硅上包层到指定厚度,制备到达不同波导层的金属通孔实现控制,如图1(i)。键合的方式适用于晶圆级生产,在大规模生产、降低单元器件成本上,有显著优势。除此之外,还可以将集成电路芯片和集成光路芯片分别在不同晶圆上制备,再通过键合实现光电混合集成芯片的制备。Ⅲ-Ⅴ化合物[64]也可以通过键合的方式与硅光芯片实现单片集成,为片上光源提供解决方案。

图1 硅光子平台晶圆键合制备三维器件的流程示意图Fig.1 Overview of bonding fabrication for 3D PIC on SiPh

1.2 沉积方式

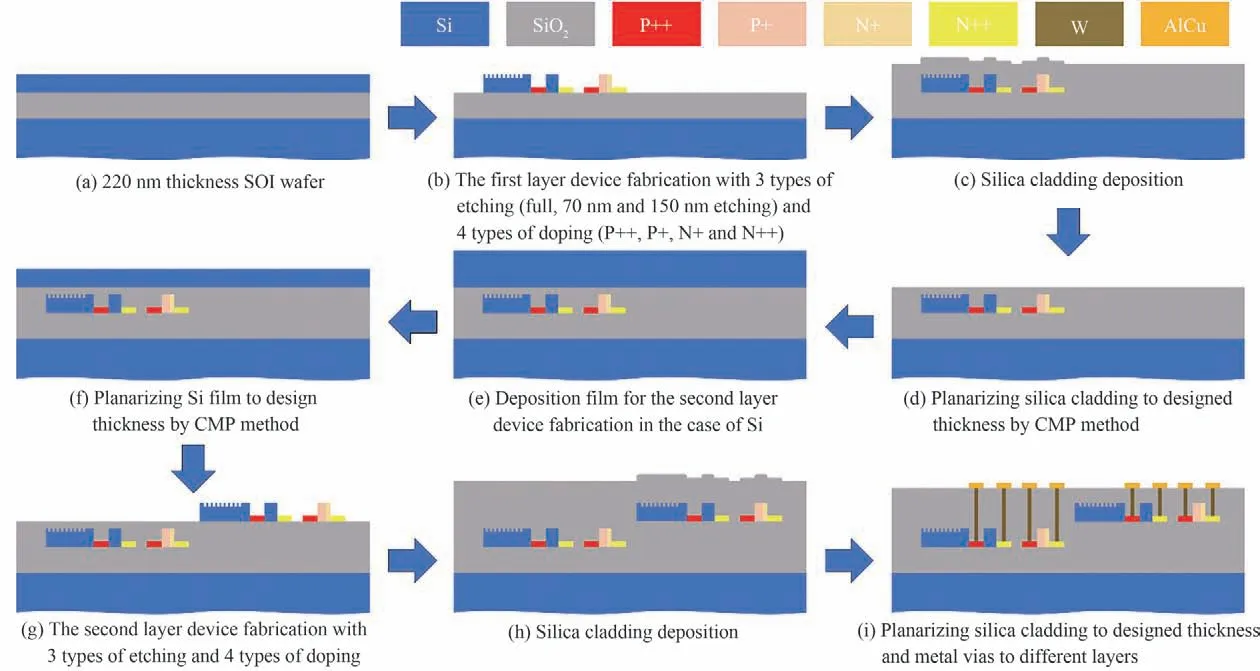

制备三维光子集成器件的气相沉积方式分为等离子体增强化学气相沉积(Plasma Enhanced Chemical Vapor Deposition,PECVD)和低压化学气相沉积(Low Pressure Chemical Vapor Deposition,LPCVD),通常该方法用于氮化硅、非晶硅(Amorphous Silicon,a-Si)和多晶硅(Polycrystalline Silicon,poly-Si)波导的制备,这些材料都可以实现在低温下沉积,制备第二层波导的过程中,对第一层器件没有影响。在硅光子平台中,通过气相沉积方式制备三维光子器件的流程如图2 所示。在完成了如图2(a)~(c)所示的第一层工艺之后,通过CMP 将二氧化硅层减薄到所需的厚度,如图2(d)所示。之后沉积用于制备第二层波导器件的薄膜如图2(e),此处以Si 材料为例,通常沉积的厚度高于设定的厚度,通过一步CMP 的工艺如图2(f),将第二层波导层抛光到想要的厚度,并且降低表面粗糙度和波导损耗。在制备第二层波导后,如图2(g)~(h),在如图2(i)中平整化上包层并制备到达不同波导层的金属通孔实现控制。

图2 硅光子平台气相沉积制备三维器件的流程示意图Fig.2 Overview of deposition fabrication for 3D PIC on SiPh

2 三维集成光子芯片的开发与应用

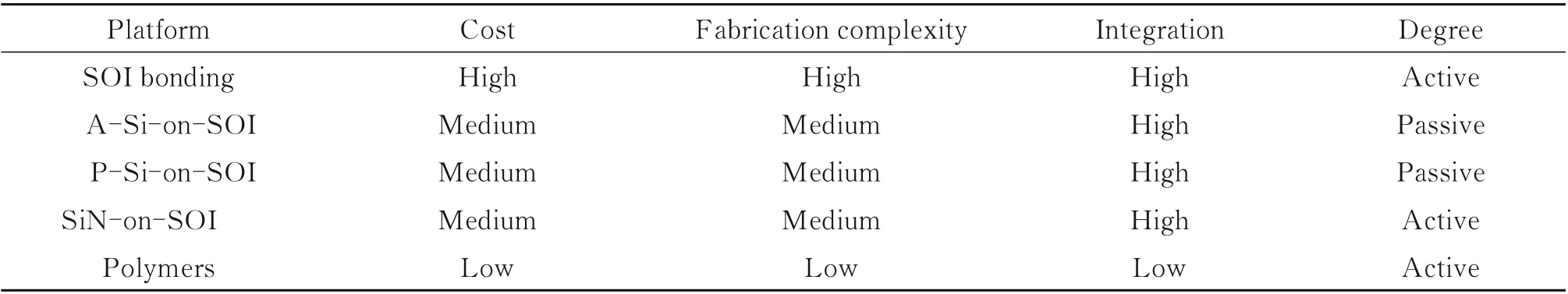

1999 年,CHU S T 等报道了三维结构二氧化硅非对称定向耦合器[65]、微环谐振器[66-68]等。受限于成本和工艺水平,制备的微环谐振器[67]的Q值(Quality Factor)仅为800。同年,GARNER S M 等在聚合物平台上,利用灰度光刻和反应离子刻蚀的方法,制备了用于三维集成的聚合物斜坡波导[69],通过垂直互连的斜坡波导制备了空间1×4 的分路器。随着硅光子学的迅猛发展,硅光子的三维集成也提上了日程,2006 年,KOONATH P 等提出了氧注入分裂(Separation by Implantation of Oxygen,SIMOX)制备三维硅光子芯片[70],然而该方法需要~1 300 ℃的高温退火,形成二氧化硅包层和治愈硅波导,使得硅中的掺杂完全失效,因此该方法仅可用于多层无源光子芯片的制备。实际上,光网络中必然存在光路由、光调制等器件,多功能、高灵活度、高度集成化的光子芯片是亟待解决的问题。如表1 所示,目前比较成熟的三维光子集成平台包括晶圆键合平台、非晶硅平台、多晶硅平台、氮化硅平台、聚合物平台,由于材料不同,每种平台有自己的优点和缺点。本节将介绍面向三维光子集成芯片工艺平台的发展情况和本身独特的优势及缺点。

表1 三维光子集成芯片平台进展Table 1 Progress of 3D photonics integrated circuits

2.1 单晶硅三维集成光子芯片

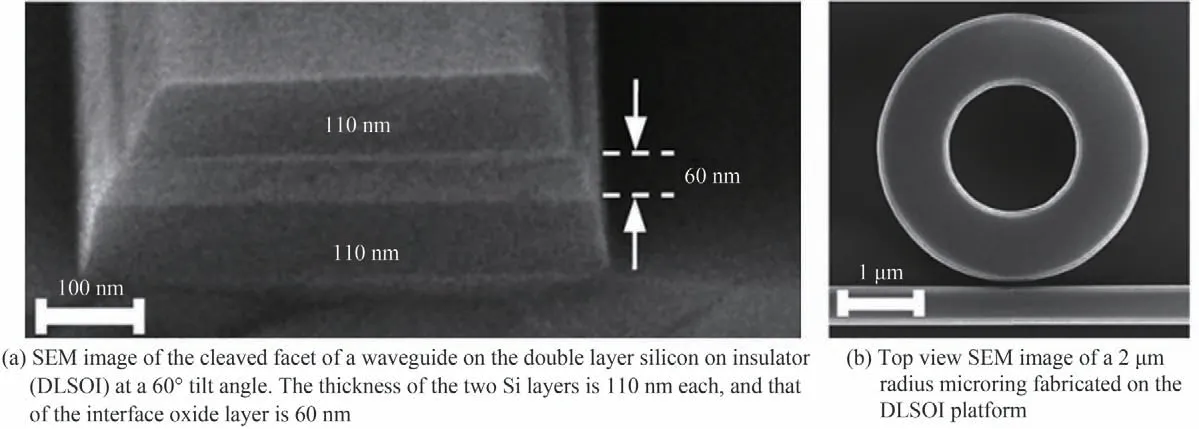

单晶硅材料具有优秀的光学、电学特性,是大规模光子集成的候选者。通过沉积法制备多层单晶硅三维光子集成芯片时,需要超过1 000 ℃的高温退火,使得有源器件失效,晶圆键合的方法可以在低温下制备单晶硅的三维集成,晶圆级加工工艺易于实现大容量生产,对降低单元器件的成本、芯片的产业化有显著作用。2014 年,乔治亚理工学院的ADIBI A 团队,实现了基于键合工艺的双层Si 波导器件,基于键合工艺开发了双层绝缘体上硅(Double-Layer Crystalline Silicon on Insulator,DLSOI)平台[22]。该工艺首先将SOI 的顶硅层减薄到110 nm,再沉积30 nm 厚的高质量二氧化硅层,将两片经过上述工艺的SOI 片键合在一起,实现DLSOI 器件的制备,层间距为60 nm。图3(a)是通过键合方式制备的双层SOI 器件的截面扫描电子显微镜(Scanning Electron Microscope,SEM)图。图3(b)是半径为2 μm 的双层SOI 微环谐振器的俯视图,与直波导是临界耦合的状态。在该实验中,分别制备了半径为2 μm 和20 μm 的微环谐振器,其中2 μm 半径的微环谐振器的Q值可达25 000,20 μm 的微环谐振器的Q值可达3.5×105。

图3 DLSOI 微环谐振器SEM 照片[22]Fig.3 SEM image of microring resonator on the DLSOI platform[22]

2019 年,加州大学伯克利分校和麻省理工学院的合作团队报道了通过晶圆键合工艺制造三维集成光学相控阵列(Optical Phase Array,OPA)[23]。分别在不同制造精度的工艺线上制备光学相控阵列和驱动,再通过晶圆键合的方式,制备了三维光电混合芯片,避免了单片制备光电混合芯片时,由于器件尺寸、工艺条件不同引入复杂工艺程序的问题。制备的工艺流程如图4 所示,光芯片、电芯片分别制备之后再通过晶圆键合,实现三维集成,通过穿孔互联的方式,实现驱动对OPA 的直接控制,最后进行切片、封装,实现单片三维光电混合集成OPA 的制备。该OPA 可以实现18.5°×16°的2D 扫描。阵列规模可以拓展到125 个端口,孔径尺寸达0.5 mm×0.5 mm,波束宽度达0.15°×0.25°,平均每个通道实现π 相位变化的功耗为20 mW。

图4 单片三维异质集成OPA 的工艺流程图[23]Fig.4 Overview of the 3-D heterogeneous integration platform used to construct the single-chip OPA[23]

晶圆键合可用于三维光子集成器件、光电混合集成器件的制备,实现单晶硅的多层堆叠,除此之外,还可用于Ⅲ-Ⅴ族材料与SOI/SiN 晶圆的键合[71,72],实现片上光源的加工。晶圆键合是CMOS 工艺兼容的晶圆级别加工方式,可以实现大规模、高容量的生产制造,很大程度降低单元器件的成本,实现商用需求。然而晶圆键合需要高昂的设备成本和开发成本,高精度的晶圆对准也非常具有挑战性,这限制了晶圆键合的推广。

2.2 非晶硅、多晶硅

低损耗的氢化非晶硅(Hydrogenated Amorphous Silicon,a-Si:H)可以在低于300 ℃的环境沉积,通过调整沉积条件,可以实现非线性系数的自由调节,a-Si 也用于多层堆叠的芯片互连和三维光子集成芯片的制备[24-26]。

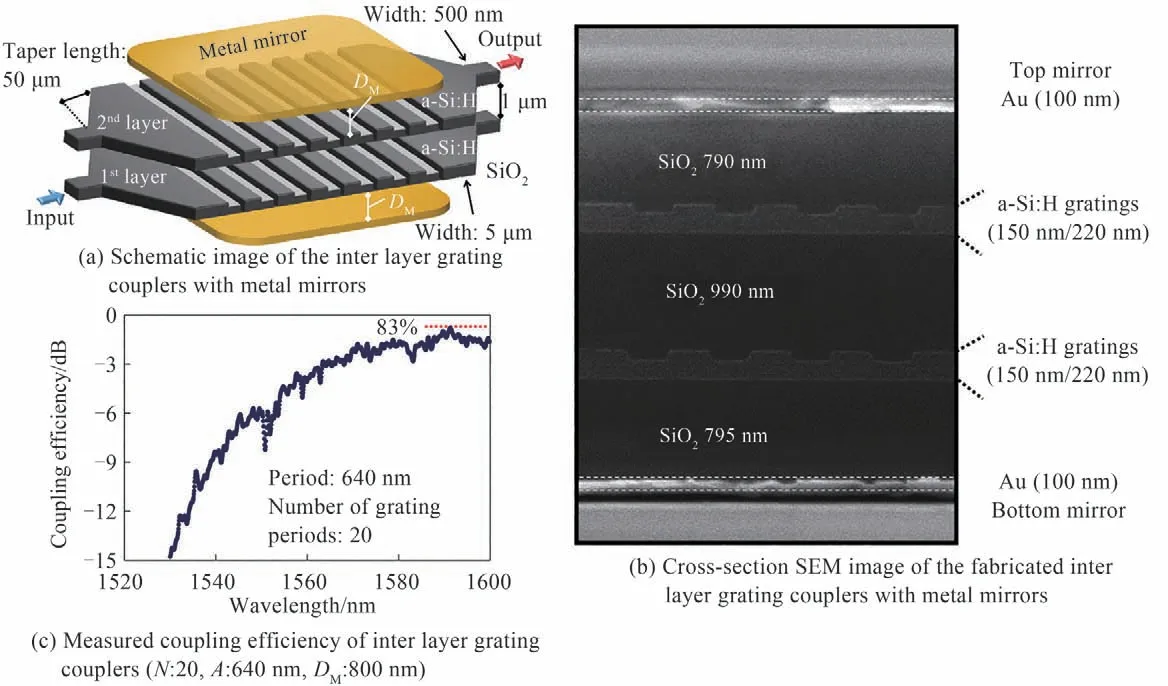

层间距是三维光子集成芯片的重要参数之一,层间距越大意味着层间波导交叉之间的串扰越小,但会导致层间转换器尺寸增大。2014 年,东京工业大学的KANG J H 等提出了一种双层光栅型的层间转换器[24],其结构示意图如图5(a)所示,为了在较大层间距的情况下,实现紧凑的高效层间耦合器,在两层耦合光栅的上下两侧引入了两层金属反射膜,通过优化尺寸,光栅区宽度为5 μm,每层波导厚度为220 nm,刻蚀为70 nm,光栅占空比为50%,周期为640 nm,耦合区共20 个周期单元,金属反射镜距离最近的波导800 nm,层间距为1 μm。制备的层间耦合截面示意图如图5(b)所示,测量结果如图5(c)所示,在1 590 nm 处最大的耦合效率达到了83%。采用金属反射膜与光栅型的层间耦合器,在较大的层间距实现了结构紧凑的高效层间转换,该层间转换器的长度仅为~12.8 μm,在层间距为1 μm 时,定向耦合器型层间转换器很难实现如此紧凑的尺寸。

图5 光栅型高效层间耦合器[24]Fig.5 Grating based interlayer transition[24]

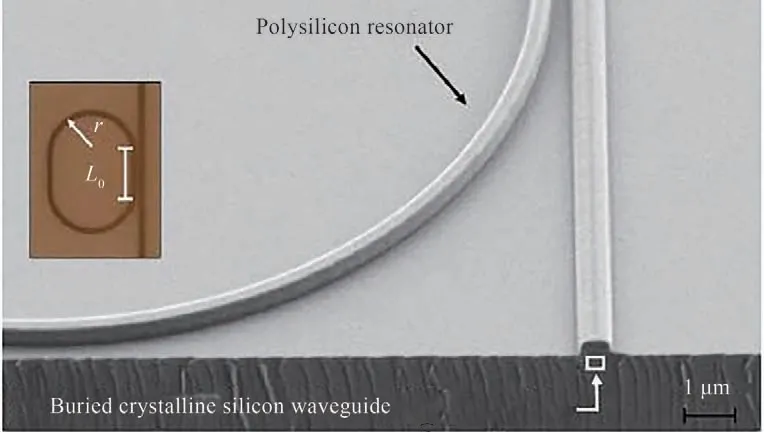

虽然a-Si具有低损耗、可调谐非线性系数的特点,但是较低的热光系数和几乎没有的电光效应使得有源器件的制备无法实现。人们将目光转向了多晶硅(Polycrystalline Silicon,poly-Si),poly-Si相比a-Si具有更加优良的迁移率特性,低温沉积的制备工艺使得用poly-Si 制备多层光子器件成为了可能[27-29]。2006 年,LIPSON M 团队报道了用于三维集成光网络的多晶硅微环谐振器[27],该器件的制备过程是首先生长了一层非晶硅薄膜,在N2中,经过600 ℃的退火形成多晶硅薄膜,再经过1 100 ℃的高温退火,进一步降低了多晶硅的损耗,实现了Q值为20 000 的微环谐振器的制备,表明当前损耗为18 dB/cm。根据上述工艺,在已经制备好波导的SOI 晶圆上,制备低损耗单晶硅微环谐振器,结构如图6所示,最终测得临界耦合的谐振峰Q达到了4 000。

图6 多晶硅跑道型微环耦合进入单晶硅波导的SEM 图,插图定义了跑道型微环半径r 和耦合区长度L0[27]Fig.6 Cross section SEM of polysilicon racetrack resonators coupled to crystalline silicon waveguides before oxide cladding. Inset shows the definition of r and coupling length L0[27]

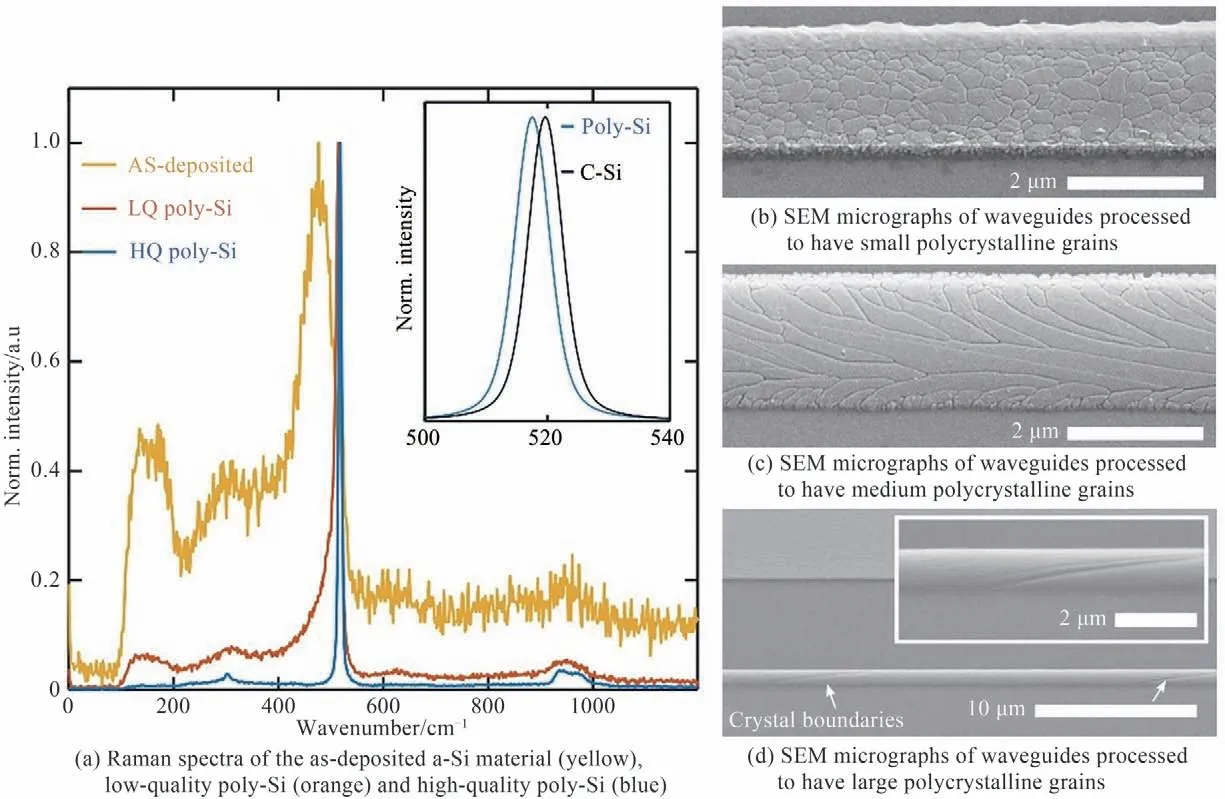

但是1 000 ℃的高温退火与CMOS 工艺并不兼容,激光退火制备多晶硅是一个更加有效提高迁移率的方法,通过激光退火制备的多晶硅兼具低损耗和高迁移率的特性,并且该工艺后端兼容,在三维光子集成制造领域具有重大前景[30-32]。2019 年,南安普顿大学的FRANZ Y 等通过激光退火工艺制备了低损耗的多晶硅波导[30],a-Si 经过455 nm 的激光进行激光退火处理,原始a-Si 与不同处理条件的a-Si 拉曼光谱图如图7(a)所示,经过激光退火的a-Si,已经形成了明显的多晶硅的吸收峰,插图与c-Si 进行对比,说明在230 mW 激光功率下,0.1 mm/s 扫描生成的多晶硅其拉曼光谱与单晶硅几乎一致。在不同激光功率下制备的多晶硅如图7(b)~(d)所示,通过优化激光功率,高质量的多晶硅基本看不到晶粒与晶界。通过截断法测试得到230 mW 激光功率制备的多晶硅损耗仅有5.31 dB/cm。激光退火制备多晶硅波导具有低损耗、高迁移率的特性,非常适合用于三维光子集成芯片的制备,但是激光退火工艺对激光的匀光性有极高的要求,为了实现晶圆级加工,稳定的扫描系统也需要被开发,这些问题一旦被解决,激光退火的方案将有很大的潜力和应用市场。

图7 激光退火加工波导的拉曼光谱和SEM 图[30]Fig.7 Raman spectra and SEM micrographs of poly-Si waveguide after laser crystallized[30]

2.3 SiN 三维集成光子芯片

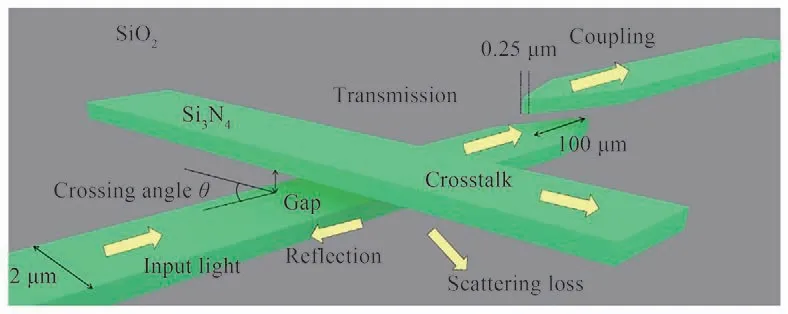

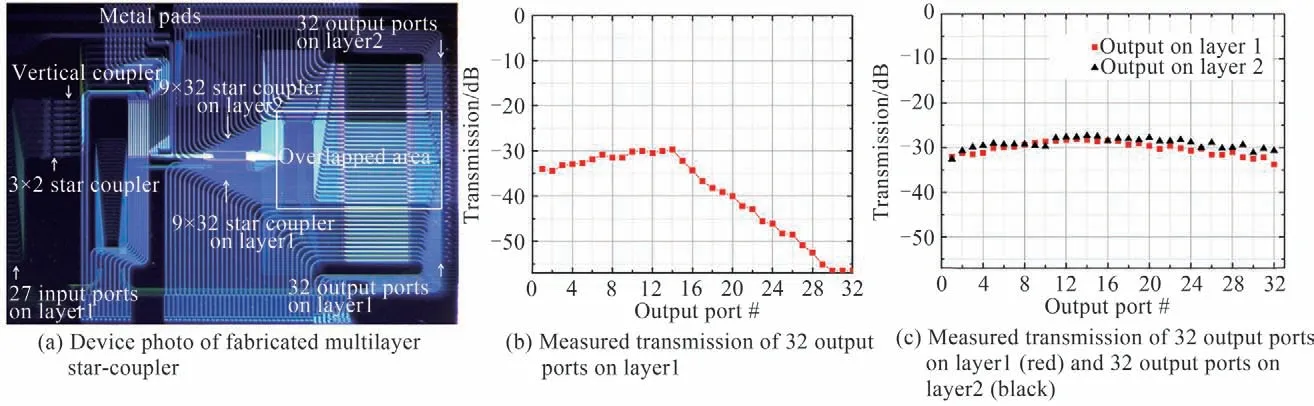

SiN 从400 nm 可见光波段到2 350 nm 中红外波段都展现出很低的传输损耗(0.1 dB/cm)[9,10]。不仅如此,SiN 还展现出良好的非线性效应,在通信波段不存在双光子吸收和自由载流子吸收效应,因此被广泛用于片上非线性研究[73,74]。SiN 材料表现出更高的工艺容差,且可通过PECVD 或LPCVD 制备,与CMOS 工艺兼容。SiN-on-SOI 三维集成工艺兼容了SiN 和Si 平台两种材料平台的优势,是很多科研平台都在开发的一种方案。2015 年,YOO S J B 团队提出了基于SiN 的三维光子集成平台[36],通过多次沉积SiN 制备了损耗低、结构紧凑的多层光子器件。该多层光子器件的结构示意图如图8 所示,光在底层传输的过程中,会在空间上遇到第二层波导,此时会产生反射、散射、透射,进入到第二层的光称为串扰,当光进入耦合区之后,会进入第二层传输,实现了层间信号的通信。为了实现高效、紧凑的层间转换,需要降低层间距,但是随着层间距的减小,层间交叉也会引入更大损耗和串扰,为了平衡两者,层间距选择为700 nm,层间转换器选择了绝热型定向耦合器,耦合区从2 μm 宽的波导通过线性锥形结构转换为0.25 μm,层间转换器长度为100 μm。对制备的器件进行测试,在中心波长1 550 nm 处,层间转换器的损耗为0.01 dB,90°层间交叉的损耗为0.167 dB,层间串扰低于-52 dB。图9(a)展示了基于上述SiN 三维光子集成平台的多层光子集成芯片。在该多层光芯片中,27 个输入端口耦合进入了9 个3×2 耦合器,并分别连接进入了分布在两层的9 ×32 的星型耦合器。通过优化多层设计,实现了部分重叠的设计,器件尺寸从原来的单层80 mm2缩小到了40 mm2。图9(b)为层间距为300 nm 时,输出传输口从#15 到#32,每条路径上多层交叉的个数从1 个增加到18 个,使得每个输出端口功率降低了2 dB,最终导致信道之间的传输功率最大大于25 dB。这说明较小的层间距将会引入很大的层间损耗。图9(c)为层间距为800 nm 的两层32 个端口的输出光功率,信道间的功率差别约为5 dB,因为层间交叉引入的损耗很小,所以认为功率差主要来自星形耦合器部分。

图8 包括绝热型垂直耦合器和波导交叉的多层光子平台结构示意图[36]Fig.8 Schematic of multilayer platform including tapered vertical coupler and waveguides crossing[36]

图9 制备的多层星型层间耦合器及其测试结果[36]Fig.9 Fabricated multilayer star-coupler and its test results[36]

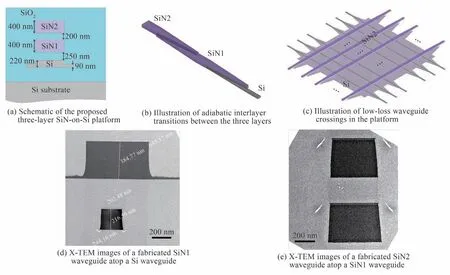

尽管SiN 展现出超低损耗的无源特性,但是较低的热光效应和几乎没有的电光特性,使得该材料在有源器件的制备领域严重受限,因此人们提出了SiN-on-Si 的三维集成光子芯片方案,在SOI 的基础上,第二层制备低损耗的SiN 波导,该平台可以综合Si 波导的高效电光、热光的调制能力,与SiN 波导低损耗的传输特性。2017 年,多伦多大学的SACHER W D 等提出了三层SiN-on-Si 的三维光子平台[37]。如图10(a)所示,中间层(SiN1)为最底层(Si),与最顶层(SiN2)提供了一个传递层,通过该方法,在250 nm 间距的两层间实现高效层间转换,而在850 nm(250+400+200)间距的两层实现低损耗的层间交叉,如图10(b)~(c)所示。图10(d)~(e)分别是在Si 层波导之上制作SiN1 层波导和在SiN1 层波导上制备SiN2 层波导的截面透射电子显微镜照片(Cross-section Transmission Electron Micrographs(XTEMs)。通过显微镜照片可以看出Si层、SiN1 层、SiN2 层的波导宽度分别为217 nm、385 nm 和385 nm,Si 层与SiN1 层、SiN1 层与SiN2 层的层间距分别为305 nm 和204 nm。制备器件的尺寸基本与设计相符。在TE 偏振下,该平台在1 480~1 620 nm 波段进行测试与表征。通过截断法得到Si 层到SiN1 层的层间转换损耗<107 mdB,SiN1 层到SiN2 层的层间转换损耗<69 mdB;层间交叉的最低损耗达到了0.28 mdB。该平台的提出对于实现光子大规模集成具有指导意义。

图10 三层SiN-on-Si 平台结构示意图及其端面显微镜照片[37]Fig.10 Schematic of the proposed three layer SiN-on-Si platform and its X-TEM images[37]

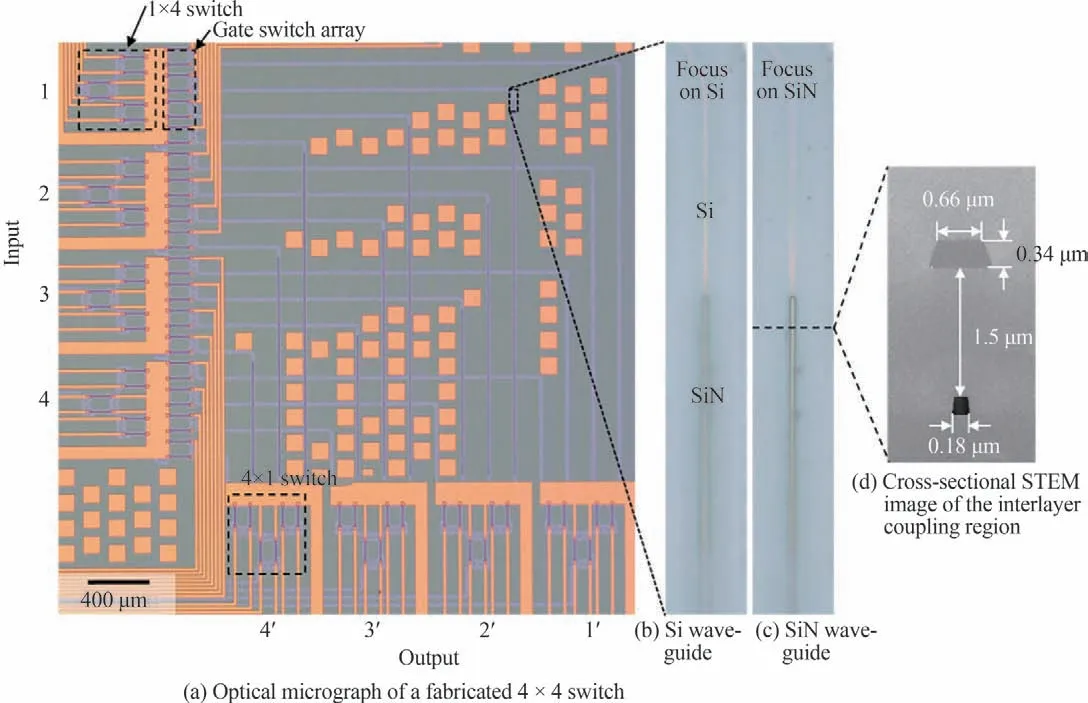

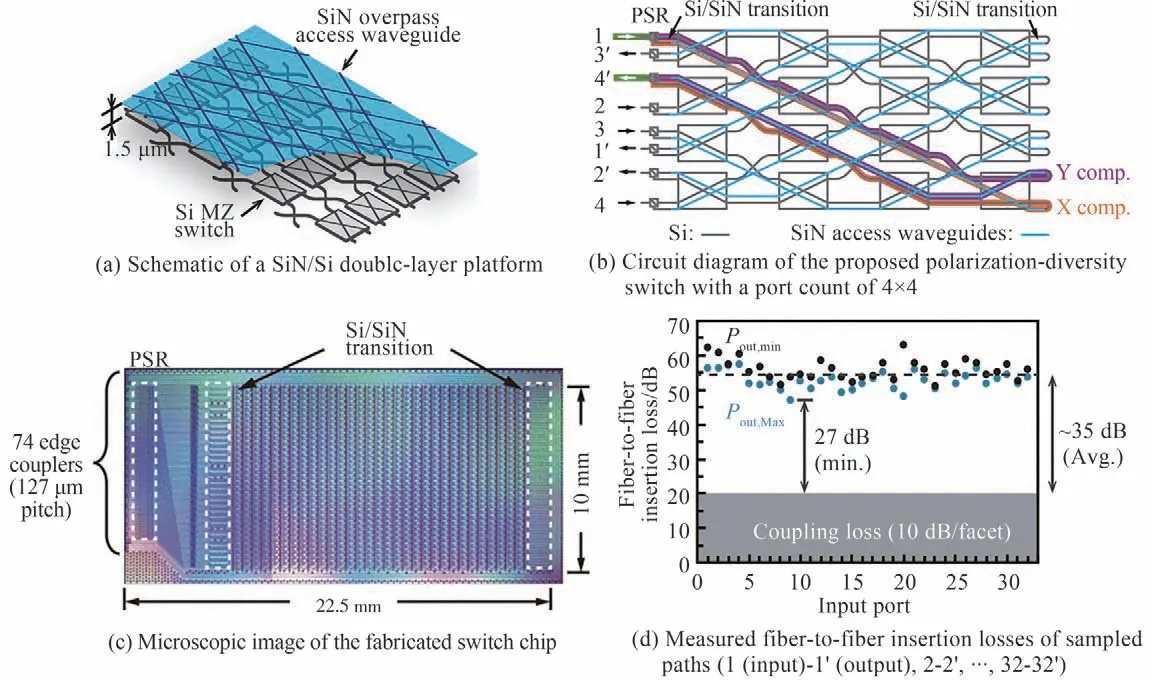

在SiN-on-Si 平台上,日本国立产业技术综合研究所的研究人员开发了多种双层光交叉阵列[38,39]。2017 年,提出并制备了双层Switch & Select(S&S)光开关[38]。图11(a)是基于SiN-on-Si 双层平台的S&S 架构的显微镜照片,光交叉规模为4×4,该架构的特点是每条路径上的波导交叉个数会相差很多,在单层SOI 晶圆上制备时,由于波导交叉损耗较大,每条路径上的非均匀性变得十分显著,当规模逐渐扩大,非均匀性进一步提高,最终导致光交叉无法工作。将该架构应用在SiN-on-Si 的多层平台上,以层间交叉取代层内交叉,可以极大降低波导交叉引入的损耗和非均匀性,从而制备更多端口、更大规模的光开关。图11(b)(c)是该器件的层间耦合结构器,图11(d)为层间耦合结构的截面示意图,层间距达到了1.5 μm,最终制备的双层器件,在C 波段,层间耦合结构(Si→SiN→Si)的损耗<1 dB,层间波导交叉损耗<0.005 dB,而层内的损耗通常在0.023~0.2 dB 范围内。对该4×4 规模的光交叉进行测试,结果表明光纤到光纤平均损耗约为12 dB,其中包括耦合损耗4.2 dB,片上Si 波导损耗约1 dB,根据路径不同,SiN 波导的损耗为0~10 dB,层间耦合结构的损耗为1 dB,层间交叉的损耗可以忽略不计(最多的路径9 个层间交叉,小于0.05 dB),开关的串扰低于-50 dB。最后该工作进一步将规模拓展至16×16 和32×32,在C波段16×16 的串扰水平低于-45 dB,如果采用优化的门开关结构,在32×32 的规模下串扰低于-50 dB也可以实现。

图11 双层S&S 架构4×4 光交叉的显微镜照片[38]Fig.11 Optical micrograph of a fabricated S&S 4 × 4 switch[38]

同样是基于SiN-on-Si 双层平台,文献[39]中提出了路径无重复的偏振分离插损路径无相关(Pathindependent Insertion-loss,PILOSS)架构,架构是在单层SOI 晶圆上提出的[75],为了实现完全无阻塞,PILOSS 架构本身会空余一组端口,造成了大量的开关冗余。在该架构中引入偏振分离的概念,两组端口分别传输TE、TM 两种偏振,使通信容量扩大一倍,而在单层晶圆上,为了避免路径重复,需要复杂的布线与尺寸的扩大,将该架构移植在SiN-on-Si 双层平台上,SiN-on-Si 双层光子平台示意图如图12(a)所示,通过第二层SiN 波导的引入,大幅降低了芯片的尺寸与布线的复杂性,层间交叉的损耗远低于层内交叉的损耗,使得提高该架构的规模成为可能。该4×4 规模的路径无重复的偏振分离PILOSS 架构的示意图如图12(b)所示,在同样的波长下,SiN 上层波导和Si 下层波导分别连接偏振分离旋转器(Polarization Splitter-Rotator,PSR)的两端,其中PSR 对准TE 模没有作用,会将经过PSR 的TM 模转换成高阶TE 模,并通过锥形波导与定向耦合器转换成基模在波导中传输。图12(b)将输入端口1 到输出端口4’做了标注。光从输入端口1 输入,经过PSR 转换TE 基模,并分别进入X 和Y 路径。原本TE 模式(X 路径)的光经过PSR,会通过层间转换器进入SiN 层传输,到达光交叉右端时,再次转换进入Si 层传输。原本TM 模式(Y 路径)经过PSR 转换成TE 基模,进入Si 波导层传输,到达右侧的层间转换器之后转移进入SiN 层传输,最后两束光再次进入输出端口4’的PSR,将X(Y)路径的光转换成TM(TE)模进行传输。该器件在8 寸SOI 晶圆上制备,SiN 层通过PECVD 沉积制备,图12(c)为制备的32×32 光交叉的显微镜照片。对芯片的插损进行了表征,如图12(d)所示,测量了32 条路径的光纤到光纤损耗,分别是输入端口1 到输出端口1’,输入端口2 到输出端口2’等32 条光路,平均损耗为35 dB,最低损耗为27 dB,包括双端光纤耦合损耗共10×2=20 dB,输入输出端模板转换器与PSR 连接损耗共0.6×2=1.2 dB,输入输出端PSR 损耗共计3×2=6 dB,Si 光交叉损耗为6.1 dB,层间转换器损耗为1.6 dB,SiN 波导损耗8.5 dB,SiN 波导交叉产生的损耗0.06×64=3.8 dB。平均偏振相关损耗为3.5 dB,最低偏振相关损耗为0.32 dB。从输入端口30 到输出端口31’共经过了29 个马赫曾德尔(Mach-Zehnder,MZ)光开关、30 个Si 交叉和64 个SiN 交叉,对该端口最大串扰为-8.8 dB,最小串扰为-3.7 dB。在22.5 mm×10 mm 的尺寸上,实现了32×32 规模的光交叉,同样的架构,在单层SOI 上,在7 mm×10 mm 的尺寸上仅可以实现8×8 规模的光交叉,该芯片纤到纤损耗为50.9 dB±3 dB,每个端口的耦合损耗都是10 dB。其损耗远大于多层光交叉,规模远小于多层光交叉,由此可以验证,三维集成在规模拓展和功能拓展方面具有明显的优势。

图12 路径无重复的偏振分离PILOSS 架构开关示意图、实物图及其测试结果[39]Fig.12 Circuit diagram,microscopic image and the measured losses of the proposed polarization-diversity PILOSS switch[39]

2.4 聚合物

聚合物光波导器件成本低、光学性能良好、制备工艺简单,仅通过旋涂、光刻、刻蚀即可完成制备,在低于200℃的条件下,可实现器件的加工,因此使用聚合物材料制备三维光子集成芯片具有明显的优势,近年有大量的相关报道[44-53]。除了传统的光刻工艺外,聚合物还可以应用于激光直写制备三维光子器件当中,对于扩展器件的功能和提高制备的灵活性有极大帮助[54-56]。

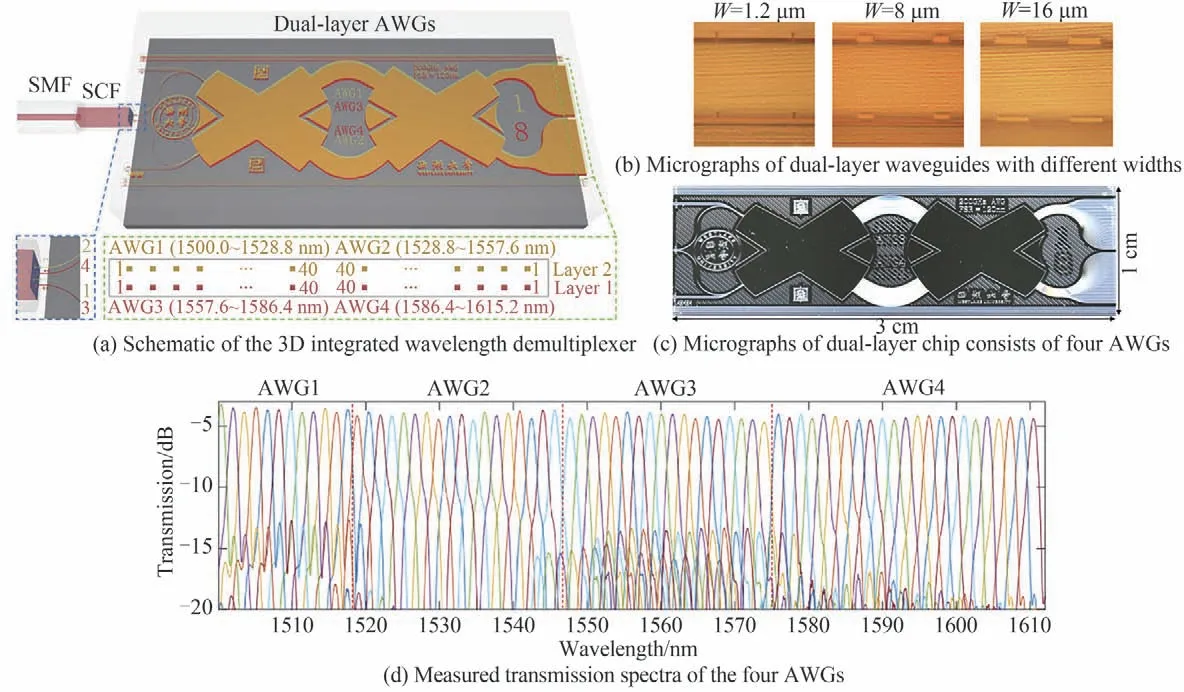

当层间间距进一步扩大时,多层器件之间可以完全避免干扰,独立传播。2021 年,西湖大学ZHANG Ziyang 团队提出了一种三维集成波导波分复用器[47],结构示意图如图13(a)所示,单模光纤(Single Mode Fiber,SMF)连接进入自制的1 分4 方形光纤(Square-Core Fiber,SCF),层间距达到了33.3 μm,通过SCF分光,分别进入双层的4 个阵列波导光栅(Array Waveguide Grating,AWG),如图13(a)左下放大图所示。每个AWG 可以覆盖75 个通道,在该设计中,引出来40 个通道,最终只有18 个通道会拿来构建波分复用器,通过该方法可以提高通道的均匀性,每个使用的通道的中心波长表示在图13(a)右下放大图中。AWG 被设计工作在4 个不同的中心波长,器件材料为ZPU 系列的聚合物材料,芯层尺寸为3 μm×3 μm。图13(b)为制备的不同宽度的双层波导的显微镜图,图13(c)为制备的三维集成波导波分复用器的显微镜俯视图,芯片尺寸仅为1 cm×3 cm。测量得到72 个端口的输出波长如图13(d)所示,器件覆盖了从1 500 nm 到1 612 nm,共112 nm 的波长,器件插损从3.26 dB 变化至4.65 dB,变化量最大为1.4 dB。三维集成的波分复用器覆盖波长范围大,通道数目多,结构远比单个AWG 紧凑。

图13 三维集成波导波分复用器[47]Fig.13 3D integrated wavelength demultiplexer[47]

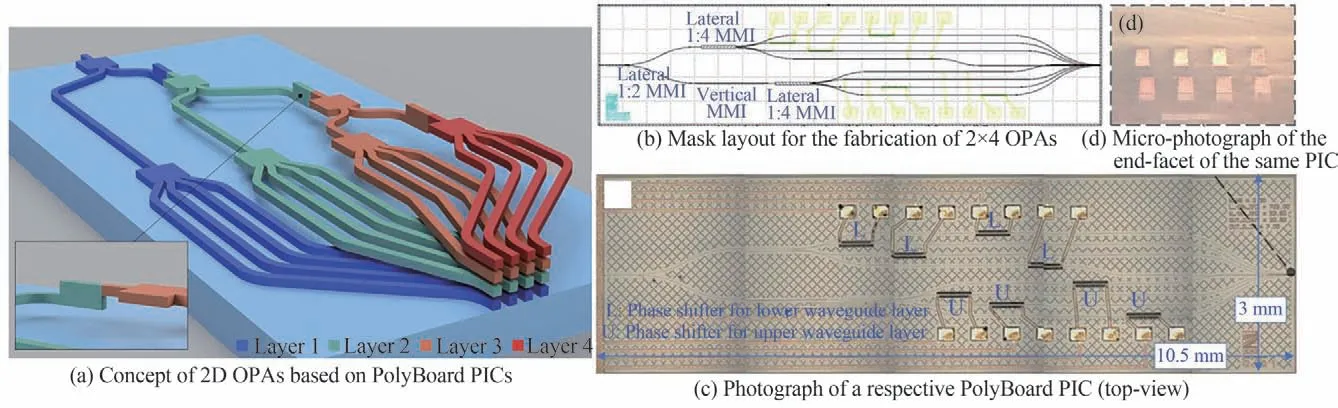

OPA 的二维扫描有两种方案,一种是采用一维线性排列天线,在一个维度上通过调节相邻天线相位差改变发射角度,实现扫描,在另一个维度上,通过改变天线部分的有效折射率(例如输入不同波长、不同偏振模式、采用多个不同周期的光栅),从而改变发射角度实现扫描;另外一种方案是采用二维排布天线,通过改变每个天线之间的相位差实现扫描。在端耦合系统中,想实现二维排列的端发射天线,必然采用三维集成的方案。2021 年,RAPTAKIS A 等首次提出了一种基于三维集成结构的聚合物二维OPA[48],在理论、实验上验证了概念的提出。图14(a)为基于三维集成结构的聚合物二维OPA 结构示意图,端面发射端规模为4×4,规模可以进一步拓展为8×8、16×16、32×32。在该三维集成平台中,采用了多模干涉器的层间转换器,该结构可以在较大层间距的情况下,实现高效耦合,缺点是需要重复的旋涂、刻蚀工艺,比较复杂。在仿真上,利用场等效原理对于平台的单模波导进行建模发现,在单波长1 550 nm 下,波导产生的波束宽度预期为12.7°。对于间距为6 μm、端口数为4×4 的OPA,最大转向角为14.0°,其中主瓣比任意栅瓣至少高出3 dB、6 dB 和10 dB的角间隙预期分别为10.8°、7.6°和2.8°。在实验上,该工作实现了2×4 OPA 的制作与测试,图14(b)~(d)展示了2×4 OPA 的版图、制备器件的俯视图和截面显微镜图。该器件的输出端水平距离为10 μm,垂直距离为7.2 μm。当输出端水平距离为10 μm 时,半波宽(Full Width at Half Maximum,FWHM)为2.1°× 5.8°。实现π的相位变化上层波导需要16 mA 的电流,下层需要20 mA 的电流。实验的结果与仿真结果一致。

图14 基于三维集成结构的聚合物二维OPA[48]Fig.14 2D OPAs based on PolyBoard PICs[48]

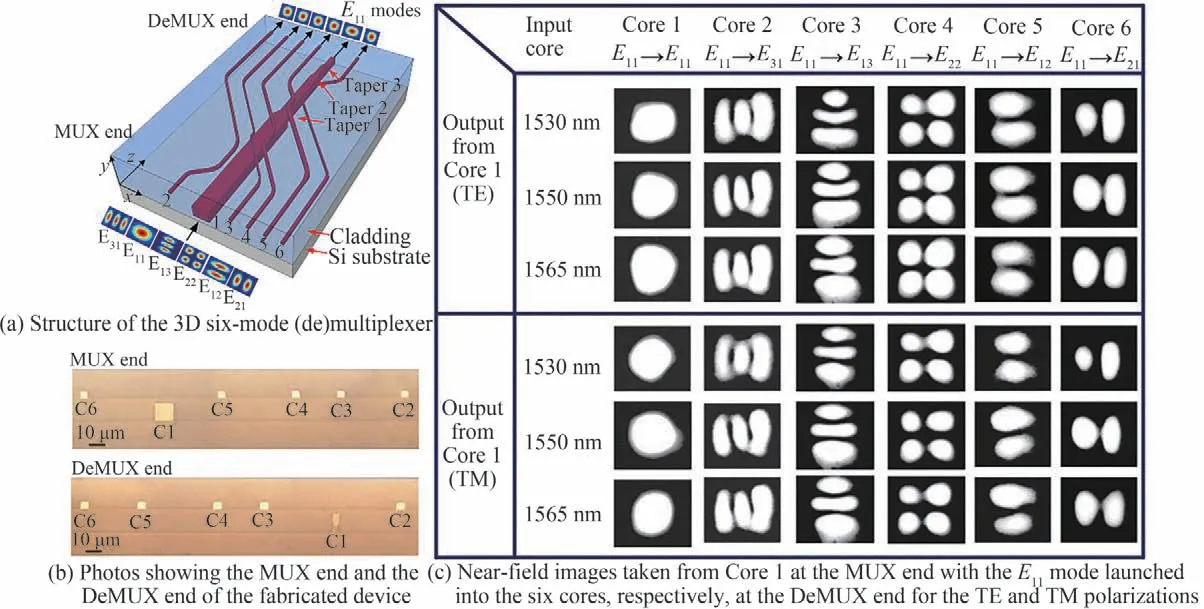

模分复用技术是进一步提高通信容量的又一关键技术,然而在同层的波导器件只能实现水平方式的模式扩展,为了实现更多模式,以及垂直高阶模的拓展,需要水平或者垂直的定向耦合器结构[44,50],由于波导位置的限制,复用模式的个数会受到限制,为了增加模式的复用/解复用,2018 年,香港城市大学CHIANG K S团队提出了一种只有垂直定向耦合器结构构成的三维聚合物模分复用器[51],耦合器分布在不同层,在芯层尺寸、位置上可以完全不受约束,其结构示意图如图15(a)所示,波导分布在两层,波导1 是一根由三根锥形波导连接的少模波导,第二层波导包括波导2~6 共5 根单模波导,通过锥形波导调整少模波导的宽度,满足定向耦合器之间模式匹配与剥离多余的残余高阶模。该器件可以实现6 个模式的复用与解复用,模式包括E11、E21、E12、E22、E31和E13。该器件还可以拓展实现更多模式之间的复用/解复用。该器件采用EpoCore 和EpoClad 作为波导的芯层和包层,制备的模分复用器的复用、解复用端如图15(b)所示。将E11模式的光在解复用端分别耦合进入波导1~6,在复用端观测波导1 的近场光斑,记录在图15(c)中,可以观测到明显的模式改变,改变输入光波长和偏振,依然可以观测到明显的模式改变。

图15 三维六个模式复用解复用器[51]Fig.15 3D six-mode(de)multiplexer[51]

3 结论

三维光子集成芯片通过多层光子器件的堆叠,突破了二维平面集成的限制,提高了光子芯片的集成度,拓展了光子芯片的功能。目前比较成熟的三维光子集成平台,由于材料不同都有自己的优点和缺点。SOI晶圆键合可以制备多层有源光子器件、光电混合集成芯片,但是开发成本、设备成本、芯片制造成本都相对较高;A-Si-on-SOI 和P-Si-on-SOI 是可以低温沉积制备的三维硅光子平台,集成度很高,但是a-Si 的迁移率很低,无法制备有源器件,p-Si 的损耗很大,无法大量采用p-Si 互连,因此两种平台都处于无源器件的制备阶段;激光退火处理a-Si 制备p-Si 可以有效地降低波导损耗、提高迁移率,但是激光的均匀性和晶圆加工的能力仍需要探索;SiN-on-SOI 是目前比较成熟的三维集成平台,在多家科研院所均有代工,但是SiN 只能实现无源器件的替代,并不能实现有源器件的制备;聚合物平台制备成本较低,三维集成的工艺简单,但是受限于芯包折射率差,器件尺寸是在几个微米级别,集成度远低于硅光子平台。除了几个普遍的三维集成平台外,还有基于晶圆键合的Ⅲ-Ⅴ族材料、溅射掺铒离子Al2O3等三维集成器件,其目的或是实现片上光源,或是实现片上光放大,在三维集成平台上,实现了多种功能的拓展。总结来说,三维光子集成不仅提供了一种提高集成度的方案,更提供了多种材料单片混合集成的可能,实现片上功能的拓展。片上光源、高性能调制器、光交叉、光探测器实现单片集成是必然的趋势,三维光子集成芯片的研发将为实现多功能、多材料体系、高密度的光子集成芯片提供一种极有可能实现的平台。