一种基于重构的FPGA远程更新方法

2022-08-26周骏,宋凯,沈洋,丁逊

周 骏,宋 凯,沈 洋,丁 逊

(中国船舶集团有限公司第八研究院,南京 211153)

0 引 言

近年来FPGA远程更新多采用ARM、CPLD等微处理器辅助方式实现[1-4],上位机通过网络通信接口将新程序发送给微处理器,并由微处理器写入非易失性存储器中。FPGA配置的加载由微处理器通过I/O口模拟FPGA配置信号时序,将新程序加载到FPGA中,完成更新。在雷达应用中,FPGA承担复杂的信号处理算法,需要大量逻辑实现,将远程更新逻辑与用户业务逻辑耦合在一起会大量占用业务可使用的逻辑资源。本文提出一种基于重构的FPGA远程更新方法,将Flash芯片分成远程更新程序区域和用户业务逻辑区域,通过ICAP原语与IPROG命令实现远程更新程序和用户业务逻辑的跳转加载。在远程更新程序中完成Flash用户业务逻辑区域配置文件的更新与维护,在完成更新后,跳转至用户业务逻辑,实现不断电远程更新程序的目的。

1 工作原理

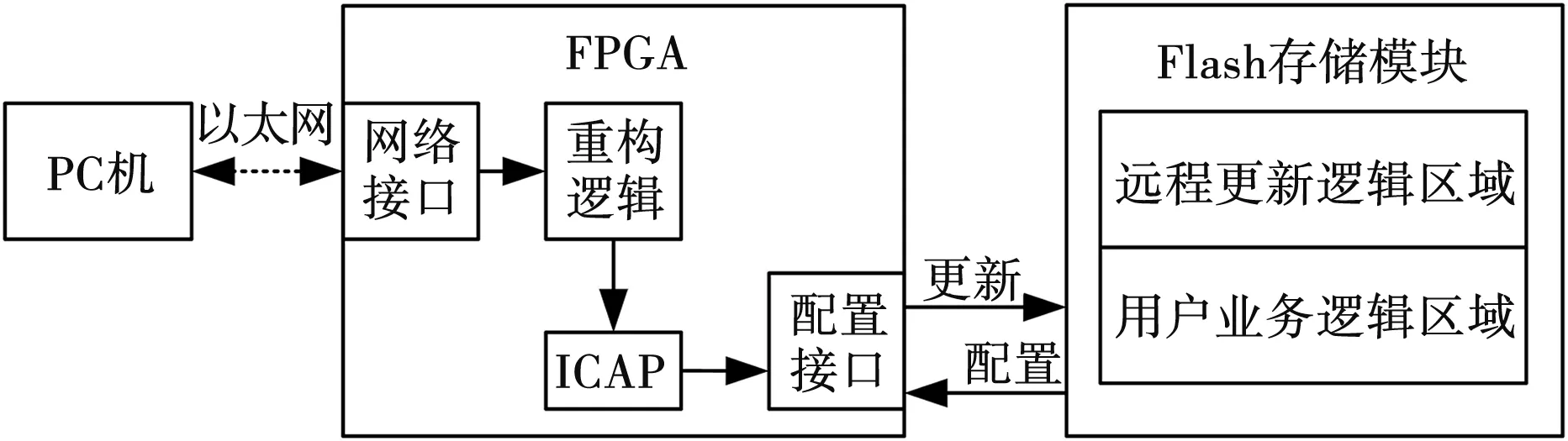

基于重构的FPGA远程更新功能依靠网络通信功能和FPGA的MultiBoot能力[5],其中MultiBoot功能是指FPGA在不断电的情况下,可以重新加载Flash中不同地址的配置文件,实现FPGA整片逻辑重构。将Flash按照最大配置文件大小分成用户业务逻辑区域和远程更新逻辑区域两个区域:前者存储用户业务程序,后者存储远程更新程序。所有配置程序均包含重构模块,重构模块通过将配置区域Flash地址写入ICAP原语并发送IPROG命令的方法,实现FPGA整片逻辑重构。

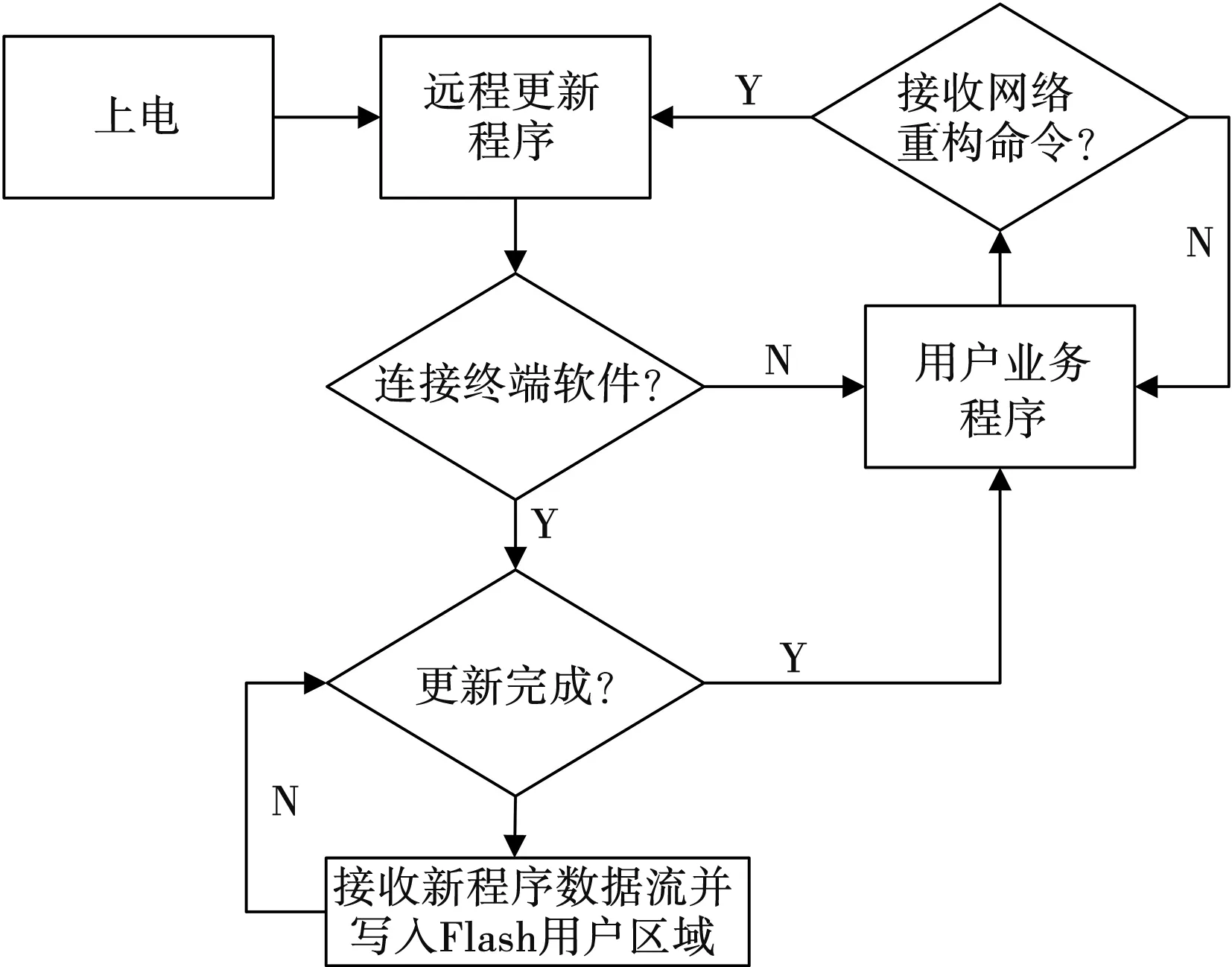

远程更新程序逻辑由重构模块、MicroBlaze系统以及运行于Microblaze系统上的嵌入式程序构成,可采用TCP/IP协议接收上位机传输的FPGA新配置,并写入Flash用户业务逻辑区域,实现配置文件的远程更新,完成后再重构加载用户业务程序即可。由图1所示的工作原理可以看出,FPGA通过网络接口模块和一个简单的状态机以及ICAP原语完成用户业务程序和远程更新程序的切换,由于两个配置逻辑文件完全独立,可以使产品具备远程更新功能的同时不占用用户业务逻辑资源。

图1 远程更新工作原理框图

2 设计实现

2.1 硬件架构

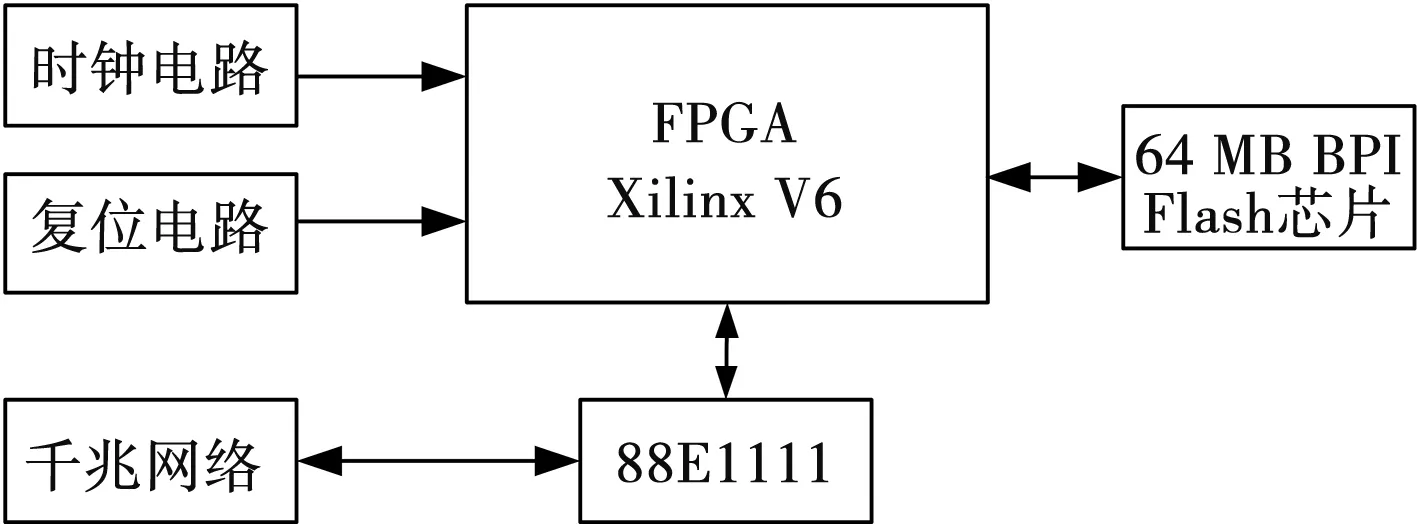

2.1.1 硬件设计

为了满足低成本、小型化需求,系统硬件采用单片FPGA处理模块、Flash芯片、网络芯片构成,其硬件框如图2所示。FPGA选用Xilinx公司的Virtex 6芯片,该芯片有充足的逻辑资源、DSP资源和RAM资源,满足导航雷达复杂信号处理的需求,同时该芯片内置专用加载模块,支持MultiBoot功能。网络接口芯片采用88E1111,Flash选择Mircon公司的JS28F512P30,存储64 MB,满足存储两个bin文件的需求。在本系统中,远程更新逻辑与用户业务逻辑共用相同网络通信链路,避免了网络交换芯片的使用。

图2 远程更新硬件框图

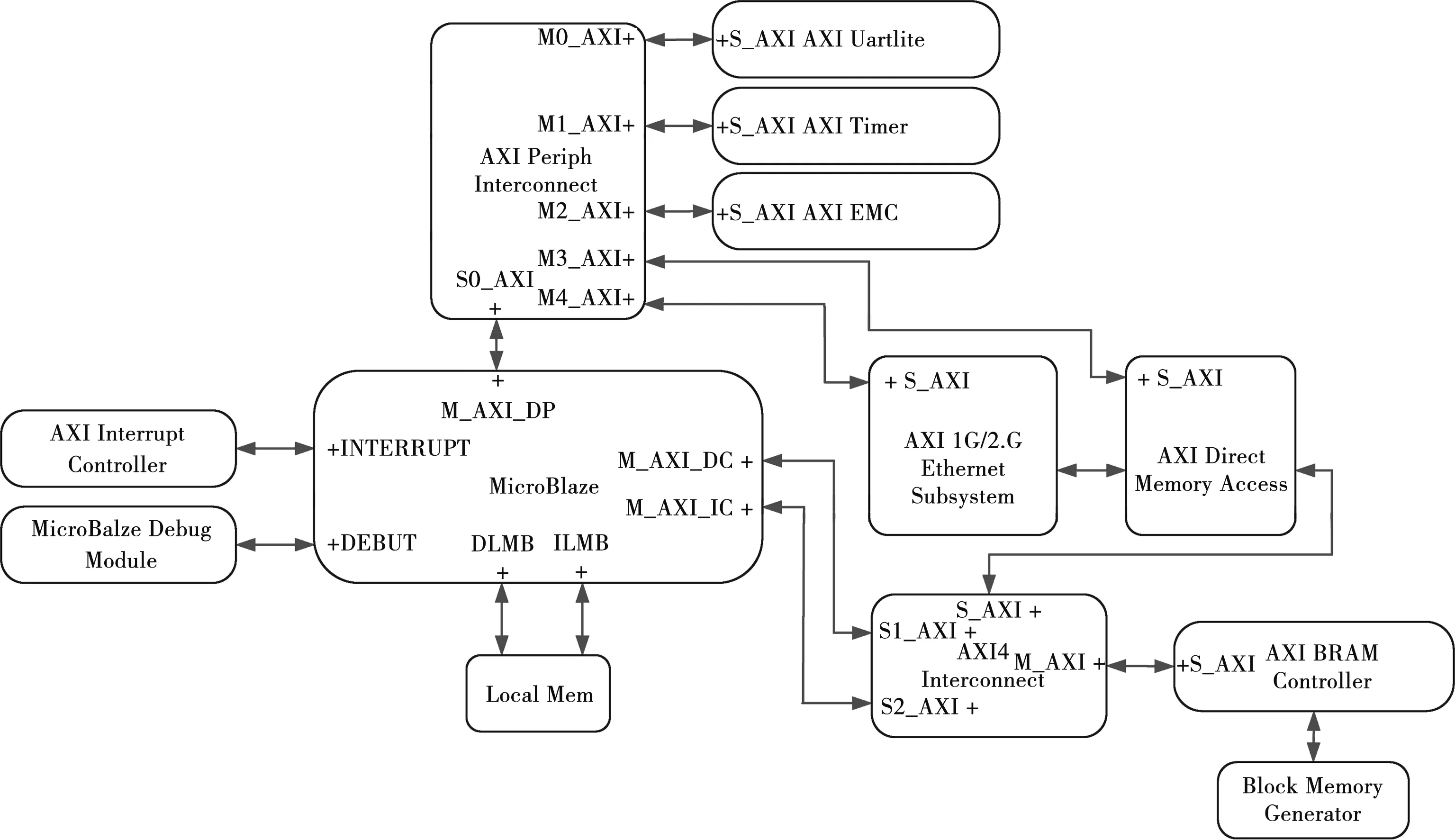

2.1.2 嵌入式软核设计

远程更新逻辑需要实现网络协议通信及Flash芯片控制,系统采用构建MicroBlaze嵌入式软核来替代传统方法中的ARM芯片。MicroBlaze系统设计如图3所示,外设方面包括网络接口模块、Flash控制模块、定时模块、调试模块、中断管理模块、存储模块等,其中由于本系统无DDR3芯片,为了给嵌入式程序提供足够的运行空间,通过AXI总线将一个片内BlockRAM模块连接到MicroBlaze的M_AXI_DC和M_AXI_IC端口充当缓存。

图3 远程更新MicroBlaze系统框图

2.2 软件设计

2.2.1 重构模块

用户业务逻辑和远程更新逻辑均有重构模块,该模块利用FPGA的Multiboot功能可以不断电加载Flash中不同区域FPGA配置文件,完成整片FPGA重构。当收到重构跳转命令后,重构模块状态机向ICAP原语写入内部加载逻辑指令序列,将重构区域Flash地址填入加载起始地址寄存器(WBSTAR)中,并写入IPROG控制指令完成重构加载。

重构跳转逻辑如图4所示。设备上电时,FPGA默认加载远程更新程序,如果在一定时间内无法连接上位机,则跳转至用户业务程序,否则等待上位机操作;当FPGA跳转至用户业务程序后,如果接收网络重构命令,通过重构模块将远程更新逻辑区域的Flash地址写入ICAP原语,并发送IPROG命令,FPGA将从远程更新逻辑区域地址开始加载远程更新逻辑,实现FPGA由用户业务逻辑向远程更新逻辑的重构。当FPGA重构为远程更新逻辑时,通过TCP/IP协议连接上位机服务器,接收由上位机发送的新用户业务逻辑bin文件数据流,写入用户业务逻辑区域,实现远程更新功能。当完成更新时,远程更新逻辑将再次利用ICAP原语,使FPGA从用户业务区域加载更新后的程序,完成不断电用户业务程序更新。

图4 重构模块原理流程图

2.2.2 嵌入式内核程序设计

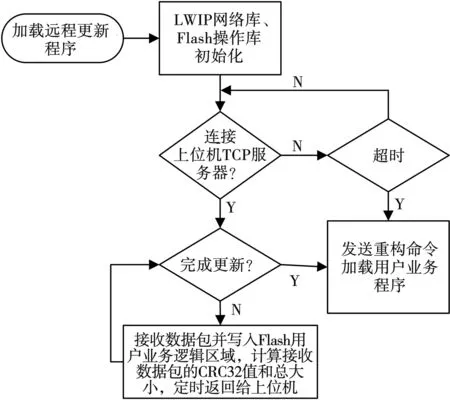

嵌入式内核程序运行于FPGA构建的MicroBlaze嵌入式软核内,其设计基于FreeRTOS操作系统,并运行LWIP网络协议栈,实现TCP/IP通信。嵌入式内核程序流程如图5所示:首先完成Flash操作库和LWIP网络库初始化,然后连接指定IP的TCP服务器。如果在一定时间内无法连接,则对重构模块发送命令跳转至用户业务模块。如果连接成功,将等待上位机操作。当需要更新程序时,上位机软件通过TCP协议发送新的用户业务程序数据包给嵌入式内核程序,嵌入式内核程序接收数据包,并写入Flash中的用户业务逻辑区域,将接收到的数据包CRC32校验值和写入的Flash数据包总大小返回给上位机程序。当上位机完成新程序文件发送,并接收到正确的CRC32校验值和数据包大小时,认为更新完成,发送重构命令给嵌入式内核程序,实现新用户业务程序的加载。

2.2.3 上位机程序设计

上位机采用MFC设计,通过TCP/IP协议与嵌入式内核程序进行通信,主要完成创建更新TCP服务端,UDP重构命令发送,用户文件读取等功能。当FPGA重构为远程更新逻辑时,嵌入式内核程序将主动连接上位机的TCP服务端。在嵌入式内核程序连接服务器成功后,上位机读取本地用户更新文件,并发送给嵌入式内核程序实现更新。更新完成后,上位机发送UDP重构命令,实现FPGA由远程更新逻辑跳转至用户业务逻辑;当FPGA重构为用户业务逻辑时,上位机软件发送UDP重构命令,FPGA收到命令后重构为远程更新逻辑,并实现用户业务逻辑更新。

图5 嵌入式内核程序流程图

2.2.4 更新失败处理

本文方法将Flash区域划分为用户业务逻辑区域和远程更新逻辑区域,其中后者起始地址为0,使FPGA上电默认启动区域。当对用户业务逻辑区域进行更新时,系统出现断电、断网等突发情况,导致用户业务逻辑更新失败,此时并没有操作远程更新逻辑区域的配置文件;当系统重新上电时,FPGA默认加载远程更新逻辑,可以继续实现对用户业务逻辑的更新,可见采用远程更新逻辑和用户业务逻辑分离设计的方式有较高的可靠性。

3 试验结果

为了验证本文方法,以一型导航雷达信号处理板卡为硬件平台,该平台采用Xilinx V6芯片,编写了远程更新程序和雷达信号处理程序。由于系统的小型化,没有采用DDR芯片,远程更新程序使用FPGA芯片内部Block Ram作为MicroBlaze程序运存,消耗17 203个寄存器、17 316个查找表以及296个RAMB36E1,其中使用的存储资源约占整个芯片存储资源的27%,而用户业务程序中使用的重构模块仅使用了31个寄存器和70个查找表。可以看出,本文方法大大减少了远程更新功能对用户业务逻辑的占用。采用本文方法对15 MB大小的bin文件进行远程更新仅需40 s,较采用JTAG下载线方式有明显优势。由于采用TCP协议传输文件流时,协议本身具备校验和重发机制,因此本文方法可靠性较高,能为采用单片FPGA的小型化系统提供远程更新功能。

4 结束语

本文基于重构的FPGA远程更新方法利用FPGA的MultiBoot功能,实现远程更新程序和用户业务程序的分离式设计,减小远程更新功能对资源的占用,不需要设计额外微处理芯片电路进行辅助,同时与用户业务程序共用相同的网络链路,利于设备小型化、低成本设计。目前该方法已应用于雷达产品,为其提供了稳定可靠的远程更新功能。