一种通用无线电监测主控板设计

2022-08-23无锡华普微电子有限公司沈小波郝国锋诸骁

无锡华普微电子有限公司 沈小波 郝国锋 诸骁

针对无线电监测设备的多制式、小型化、便携式及低功耗等要求,设计了一种小型化多制式通用无线监测主控板。该系统采用软件无线电思想,以ZYNQ系列片上系统(System on Chip, SoC)作为主控单元,采用可编程射频芯片AD9361为射频收发单元核心,开发了系统处理软件和测试软件,最后进行了系统收发功能实验验证。结果表明,该系统可以稳定可靠的接收无线电信号,可应用于民用无线电监测、军用小型无人机以及单兵设备,具有极大的商用价值以及军用价值。

随着无线通信技术快速的发展,各类无线电通信业务应用日益广泛,无线电监测系统作为监测和管理无线电的重要设备,得到了长足发展。传统监测系统具有体积大、制式和频段单一、不易携带、不便装备于小型化特殊装备等缺点。目前新体制无线电监测系统已经得到应用,大多是采用将无线电信号变频至中频信号范围,在模数转换之后,通过FPGA或DSP进行数据处理,最后传输至PC机实施信号分析。市场现存的新体制无线电监测设备也存在诸多缺点,如德国的罗德史瓦兹公司推出的几种无线监测系统,由于价格昂贵限制其广泛应用。相对于国外的无线电监测系统,国内的无线电监测系统架构大多是传统测量技术的无线电监测系统,虽然价格上具备一定优势,但是国产的无线电监测系统产品系列还不够完善,技术上还不够成熟,与主流产品相比性能差距较大,国产系统目前不能完全满足国内的无线电监测要求。

针对目前无线电监测系统存在的诸多问题,本文设计了一种基于软件无线电技术,以可编程射频芯片AD9361和SoC为处理核心的通用无线电监测主控板,通过可编程配置技术,实现对现有的多种通信制式信号的接收。

1 总体方案设计

本文设计的通用无线电监测主控板是基于软件无线电的思想建立的硬件平台,主要包括:天线接口、信号调理电路、射频收发控制器、SoC控制器、驱动软件及应用软件几部分,无线监测主控板的系统框图如图1所示。主控板由射频收发器接收空间无线电信号,经过信号滤波、A/D转换等操作后将转换后的数字信号传递给SoC,SoC对数字化信号进行处理,得到基带信号后进行信号处理算法,最终分析出无线电信号特征。

图1 系统硬件框图Fig.1 System hardware block diagram

2 系统硬件设计

无线电监测主控板的硬件平台由射频电路、基带处理电路、接口电路、时钟电路和电源电路组成。基带处理电路部分采用SoC作为主控处理器,通过数字数据接口同时完成对发射信号的编码调制和对接收信号的解调解码,并完成对数据的分析和处理。

2.1 主处理器模块

主处理器模块采用控制器芯片是XC7Z045-2FFG900I。该芯片是Xilinx公司推出最新一代Zynq-7000系列可编程SoC芯片,集成了ARM Cortex A9和Kintex-7系列FPGA。FPGA与ARM之间通过片内高速AXI总线完成数据交换,与较传统的硬件处理平台相比具有数据传输延时低、数据率高、开发流程简单等特点。另外,片内的两个高速的ARM处理器核,每个处理器核的运算速度均可达到2.5 DMIPS/MHz,运行频率最大800MHz,内置USB2.0接口、CAN2.0接口、SPI接口、UART接口以及PCI-e、高速以太网接口等外部接口;片内Kintex-7系列FPGA逻辑资源丰富,为快速的并行处理提供支撑。选用的SoC芯片可以极大的提高系统性能、降低开发难度、缩短开发时间。

2.2 射频电路

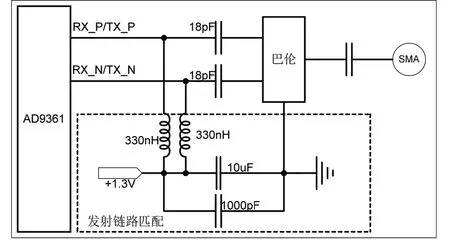

选用AD9361作为射频电路的核心模块,外部通过巴伦、匹配电路等器件进行信号调理,通过SMA连接天线进行信号接收与发射,一个通道的射频电路硬件架构如图2所示,其中虚线部分是发射部分电路,作为接收端使用时不再需要虚线内部电路。

图2 部分射频电路硬件架构Fig.2 Part of RF circuit hardware architecture

AD9361采用零中频架构、小尺寸及超低功耗设计。芯片频率覆盖范围70MHz~6000MHz,支持最新的标准通信协议,全面兼容现有的通信制式。芯片内部具有自动/手动增益控制、正交误差和直流偏置校准功能。AD9361具备可配置数字接口,基带处理电路通过软件配置实现对芯片控制,提高了系统的灵活性,简化了处理器模块的算法的设计。因此,选用高集成度的射频芯片AD9361,极大的降低了硬件成本,缩短了研发周期,这为小型化、低功耗的多制式的无线监测系统设计提供极大的便利性。巴伦选用型号为TCM1-63AX+,是一款表贴射频变换器,具有优越性能,其工作频率范围为10MHz~6000MHz,可以覆盖的70MHz~6000MHz全频段。把巴伦应用在接收端时,实现非平衡信号向平衡信号转换,应用在发射端时相反。匹配电路作用在于驱动发射信号功率和降低射频信号泄露。

2.3 电源及时钟电路

系统电源采用DC-12V输入,电源电路提供工作电源种类为5V、3.3V、2.5V、1.8V、1.5V、1.3V、1V和0.75V。采用2片四路输出的DC-DC模块LTM4644为数字电路部分提供电源,模拟电路部分由LDO模块ADP1755提供稳定可靠的电源。印制板上应使用足够的去耦电容以保证供电电源性能。整个系统时钟信号包括:AD9361参考时钟40MHz和SoC系统工作时钟33.333MHz和延时校准时钟200MHz。其中SoC系统工作时钟和延时校准时钟通过普通有源晶振产生;AD9361参考时钟在器件内部生成所有数据时钟、采样时钟和本振,因此参考时钟的频率稳定性决定了AD9361采集精度。考虑设计成本,设计采用了40MHz晶体谐振器作为AD9361参考时钟,通过启动芯片内部的温度传感器和数字控制晶振功能,结合软件校准算法,保证采集频率精度控制1KHz以内。

3 系统软件设计

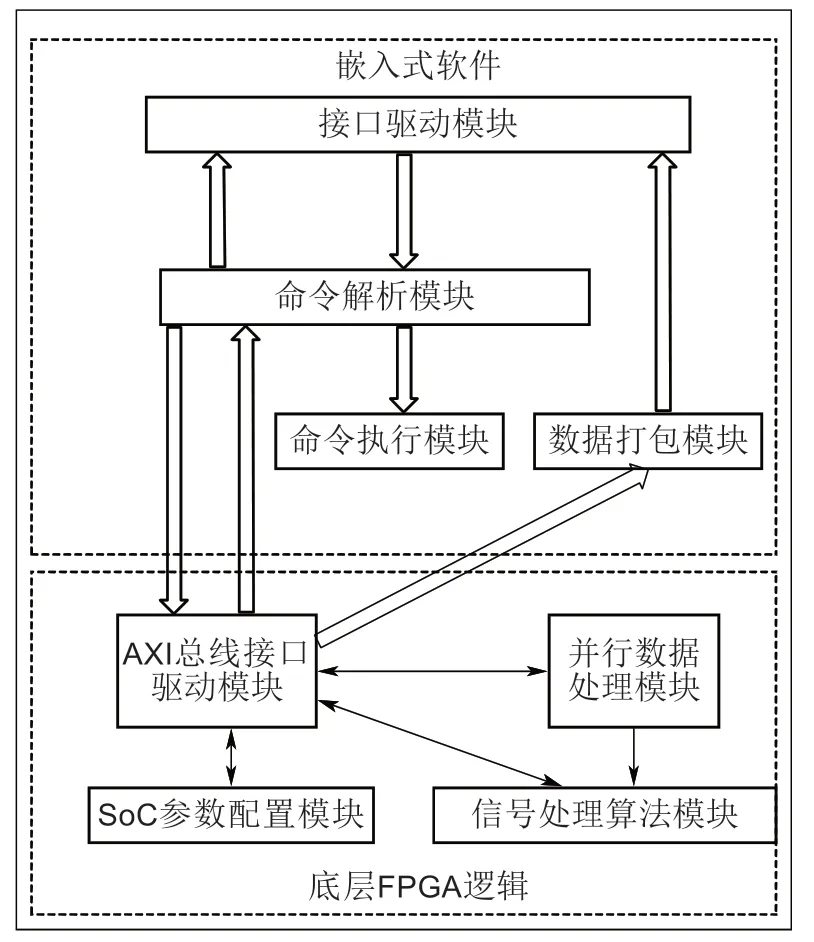

无线监测主控板的系统软件框图如图3所示。软件主要包括嵌入式软件和底层FPGA逻辑两部分。ZYNQ系列SoC包括处理系统(Processing System,PS)和可编程逻辑(Programmable Logic,PL)两部分,其中PS部分包含了最高可运行在1GHz的双Cortex-A9核,PL部分包含FPGA逻辑单元和DSP资源。本设计使用Xilinx公司提供的Vivado开发套件进行开发,Vivado主环境完成底层FPGA逻辑设计,即PL端自定义IP核开发;SDK软件辅助环境完成嵌入式软件设计,即PS端的设计软件设计。

图3 系统软件框图Fig.3 System software block diagram

3.1 嵌入式软件设计

在PS端搭建了嵌入式Linux操作系统,嵌入式软件在Linux下使用C语言进行开发,采用系统内丰富的接口驱动、协议栈等进行程序开发,同时通过调用API函数实现寄存器的配置选择,降低软件的开发难度。主要完成AD9361初始化和功能配置、底层FPGA逻辑模块控制以及系统命令解析和转发等功能,嵌入式软件主要包括:接口驱动、命令解析、命令执行和数据打包等模块。接口驱动模块实现以太网接口驱动、TCP/IP协议栈,串口驱动以及SPI接口驱动功能;命令解析模块接收网口和串口下发的指令信息,并将命令解析后分发到嵌入式软件内部、AD9361和底层FPGA逻辑模块,命令解析模块接收到上报状态信息后发送至接口驱动模块;命令执行模块接收到命令解析模块下发的命令后在嵌入式软件内部执行相关命令操作;数据打包模块能接收并行数据处理模块转发的ADC采集的原始数据和信号处理算法模块转发的信号表数据,通过预设的数据传输格式进行数据打包发送至接口驱动模块。

3.2 底层FPGA逻辑设计

底层FPGA逻辑主要完成自定义IP核设计,采用Verilog-HDL语言和Block Design设计实现。主要包括SoC参数配置、AXI总线接口驱动、并行数据处理以及数字信号处理算法等模块。AXI总线接口驱动模块:调用开发软件提供的IP核AXI4-Stream,在IP核内部封装好自定义程序,用于和PS端的嵌入式软件进行通信;并行数据处理模块:主要包括通道寄存器映射、公共寄存器映射、数据训练、延时校正、数据接收、直流偏置校准、IQ校正和数据发送等功能;信号处理算法模块:包括数据预处理、FFT算法、信号表发送等功能。

4 系统测试与验证

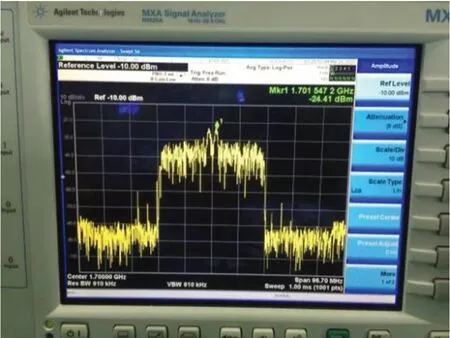

本文根据系统设计指标,开发了无线监测主控板,系统具备4通道收发能力,能同时监测4部无线信号,覆盖70MHz~6000MHz频段范围,最大56MHz接收带宽,接收灵敏度可达-105dBm,主控板尺寸仅为φ80mm,重量小于100g,功耗不足10W,本文采用LTE-TDD制式20MHz带宽信号分别对监测系统的收发功能进行测试。发射的射频信号在频谱仪显示的频谱波形如图4所示。

图4 发射频谱波形Fig.4 Emission spectral waveform

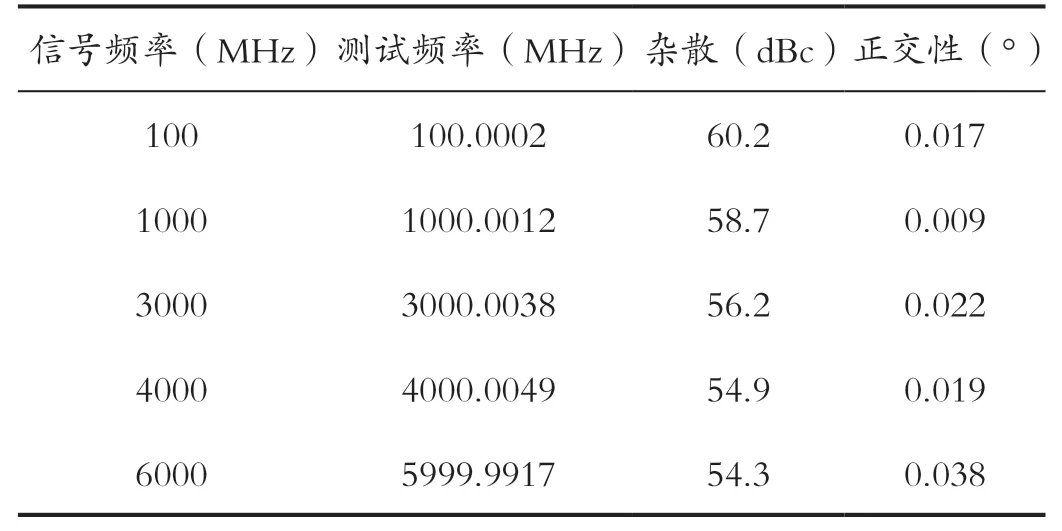

通过试验测试,通用无线电监测主控板技术指标如表1所示,满足系统指标需求。

表1 主控板技术指标Tab.1 Technical specifications of the main control board

5 结论

本文设计的基于软件无线电的思想,采用SoC和AD9361作为主控芯片的无线监测主控板可实现多制式无线电监测功能。具有成本低、易携带、功耗低等优点。由于其系统的易扩展性,该系统可进一步应用在通信侦察和干扰、简易频谱仪、便携式信号源等方面,具有广泛应用前景。