基于FPGA的数字时钟设计

2022-08-11黄明霞许泽恩张海强包龙生

黄明霞,许泽恩,张海强,包龙生

(沈阳建筑大学交通工程学院,辽宁 沈阳 110168)

在科技飞速发展的今天,最具代表性的时间装置是数字时钟。摆和摆轮游丝的创造,把时间误差从分级减小到秒级。石英晶体振荡器的应用,创造了时间精度更好的石英电子钟。再之后是单片机的应用,把时间在误差上从分级减小到1/600万秒。刘晓萌[1]以单片机、温度传感器、液晶显示屏、时钟芯片等硬件,用C语言编程实现了数字时钟的设计。叶飞[2]以单片机STC89C51为核心,结合相关的外围电路实现了数字时钟设计。韩雷等[3]利用组合逻辑电路和时序逻辑电路将数字钟小时计数器设计成12进制,并在NI Multisim软件下模拟仿真。许亚迪等[4]以555定时器、74系列集成芯片配合各种逻辑门设计了数字时钟。刘颖杰等[5]利用EDA技术,在Quartus II环境下采用自顶向下的设计方法实现了数字时钟。

数字时钟是通过电子技术实现显示时、分、秒的计时装置,与传统的石英表、机械表、手表及其他类表相比,具有精准性、易读性,并且具有更长的使用年限。数字电子钟以小巧、质量轻、高精准度、易制作、稳定性强等优点,在各领域都有着广泛的应用。从日常生活中的电子表,到信号灯、火车站、飞机场等公共场所。基于上述分析,笔者利用EDA技术在FPGA的基础上使用Verilog硬件描述语言实现数字时钟设计;叙述了分频的原理和数码管的工作原理,通过代码和伪代码描述了各模块的实现过程,然后对分频模块和计数校时模块进行了功能仿真。经功能验证无误后,在顶层模块例化并连接各个模块后编译,编译成功;最后,在FPGA开发板上调试验证。研究表明:在对数字时钟系统进行功能仿真和调试的过程中出现的错误,可以通过计算机在软件上修改和优化;Verilog硬件描述语言与具体电路无关,大大减少了设计所需要的时间,提高了设计的效率;Verilog硬件描述语言是EDA技术的重要组成部分,可用于数字电路与系统的描述、模拟和自动设计,而且Verilog语言与具体的电路无关,通过QUARTUSII的开发环境,可以降低设计所需的时间,提高设计效率。

1 编程软件及语言介绍

1.1 FPGA简介

FPGA的英文全称为Field Programmable Gate Array,即可编程门阵列。它是在PAL、CPLD的基础发展而来。相比于复杂可编程逻辑门阵列而言,FPGA中有更丰富的寄存器资源。由于它高密度、高性能的特征,在通信产业、电子产业、医疗机构、军工业等各个领域有着广泛的应用,并且有以下几个优点:①电路运行速度快:FPGA是通过对电路编程生成逻辑电路来实现功能,处理器是串行执行的,而FPGA是并行执行,因此运行速度要高于其他处理器;②可靠性高:FPGA都是经过专门验证的半定制通用器件,因此有较高的可靠性;③成本很低:因为使用FPGA可以不用修改电路板来修改逻辑电路,而且相比于ASIC再开发的费用也很低;④易于维护和升级:FPGA芯片中可以存储多个配置文件实现多种电路功能,还可以通过网络进行远程配置,这些特性使得FPGA易于维护和升级。

1.2 Verilog HDL 语言的简介

硬件描述语言(HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。利用这种语言,数字电路系统的设计可以从顶层到底层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统;然后,利用电子设计自动化(EDA)工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表;再用专用集成电路ASIC或现场可编程门阵列FPGA自动布局布线工具,把网表转换为要实现的具体电路布线结构。

1.3 Quartus II的设计流程

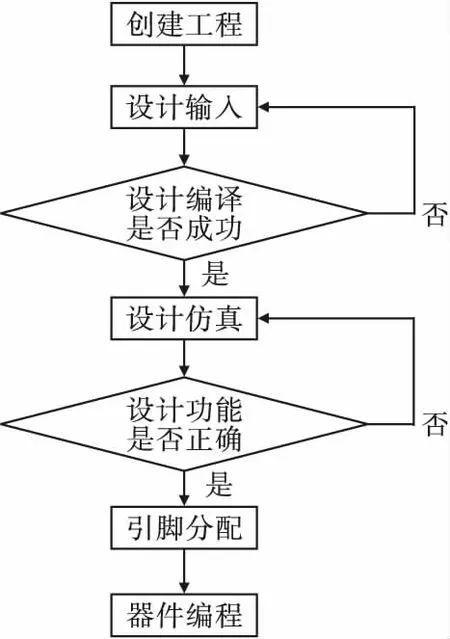

Quartus II的设计流程主要包括工程创建、设计输入、设计编译、设计仿真、分配引脚和下载编译等[6],如图1所示。

图1 Quartus II的设计流程图Fig.1Design flow chart of Quartus II

(1)创建工程:Quartus II每次只进行一个项目,并将项目信息保存在同一文件夹中。双击Quartus II图标→【File】/【New project Wizard】→在【Family】和【Available devices】中选择芯片系列和型号→选择第三方EDA工具→完成。

(2)设计输入:新建工程以后就可以设计输入。Quartus II有多种设计输入方法,如模块输入法、Core输入法、EDA设计输入法、原理图输入法和文本输入法。其中普遍使用的是原理图输入法和文本输入法。

(3)编译项目:Quartus II软件的编译器包括多个独立模块,各模块可以单独运行,也可以【Processing】/【Start Compilation】全编译。

(4)设计仿真:完成编辑和编译等步骤以后,可以用Quartus II自带的仿真功能对编写的代码进行仿真,也可以使用第三方仿真软件Modelsim仿真软件进行仿真,测试其波形。

(5)引脚分配:引脚分配是把编写的输入输出信号,固定到指定的芯片的管脚上去,为了将编写设计好的东西下载到芯片上去,方便验证和测试。

(6)器件编程:把设计好的文件下载到开发板的芯片上去。

2 数字时钟各模块的设计

数字时钟主要的功能是计时,把时间显示出来。笔者设计的数字时钟有三个模块,分频模块、计数校时模块、译码显示模块。采用自顶向下的方法设计并完成各个模块[7-14],使数字时钟具有正常计数及校时的功能。

2.1 整体模块

顶层模块是将各子模块连接成一体并实现其功能的模块,如图2所示。

图2 顶层模块图Fig.2Diagram of the top-level module

该模块的各个端口说明如下。

分频模块:把输入信号50 MHz晶振频率分频成1Hz时钟信号。

计数校时模块:把分频成1 Hz的信号当做输入信号,每经过一个时钟脉冲进行一次计数,可以调时、调分、调秒。

译码显示模块:把计时数据通过数码管显示出来。

输入信号:

clk_50 MHz:开发板晶振频率50 MHz;

RST:时钟复位信号;

zhuangtai:工作模式控制信号,模式定义为:00表示正常计数,01为调小时,10为调分钟,11为调秒钟;

UP:调校模式加1的调节信号;

DN:调校模式减1的调节信号。

输出信号:

clk_1Hz:把50 MHz分频得到的1 Hz时钟信号;

shi[7:0]:“时”数据;

fen[7:0]:“分”数据;

miao[7:0]:“秒”数据。

2.2 分频模块

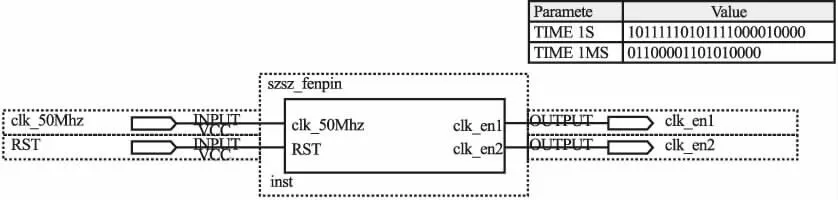

开发板的晶振频率为50 MHz,而计数校时模块和译码显示模块运行需要1 Hz和1 kHz的时钟信号,所以需要分频来得到合适的频率。为了确保计数精准,对50 MHz时钟信号进行50 000 000次计数,分频产生1Hz的时钟信号。1 kHz的信号则需要计数50 000次,模块图如图3所示。

图3 分频模块Fig.3Diagram of the frequency division module

2.3 计数校时模块

计数校时模块是数字时钟系统的主要模块,它会根据输入的信号改变时钟的工作状态,数字时钟流程图如图4所示。

图4 计数校时模块流程图Fig.4Flow chart of the counting and timing module

计数校时模块的基本思想:首先判断输入信号是否有复位信号,若有则将所有信号清零,否则进入状态选择。若输入信号为zhuangtai=2′b01,判断UP信号是否为1,是则小时位加1,否则再判断DN信号是否为1,是则小时位减1,否则正常计数。若输入信号为zhuangtai=2′b10,判断UP信号是否为1,是则分钟位加1,否则再判断DN信号是否为1,是则分钟位减1,否则正常计数。若输入信号为zhuangtai=2′b11,判断UP信号是否为1,是则秒钟位加1,否则再判断DN信号是否为1,是则秒钟位减1,否则正常计数。计数校时模块如图5所示。

图5 计数校时模块Fig.5Diagram of the counting time module

输入信号:

RST:复位信号;

clk_1 Hz:1 Hz时钟信号;

zhuangtai:工作模式的控制信号,模式定义为00表示正常计数,01为调小时,10为调分钟,11为调秒钟;

UP:加1的校时信号;

DN:减1的校时信号。

输出信号:

shi[7:0]:“时”数据;

fen[7:0]:“分”数据;

miao[7:0]:“秒”数据。

2.4 显示模块

数字时钟的七段数码管一般由8个发光二极管组成,并通过动态扫描的方式在8个数码管上显示时间。原理图如图6所示,其中7个细长的发光二极管组成数字显示,另外一个圆形的发光二极管显示小数点。发光二极管的阳极连在一起称为共阳极数码管,阴极连在一起称为共阴极数码管。对于共阴极数码管,根据需要显示的数字0、1、2、3、4、5、6、7、8、9,点亮对应哪几段发光二极管。

图6 七段数码显示原理图Fig.6The display schematic diagram of seven-paragraph digital

依据以上原理设计显示模块,模块图如图7所示。时钟信号、复位信号、时、分、秒数据作为输入信号,七段数码管段选的输出和显示时、分、秒的十位数和个位数选择的位选作为输出信号。再另设两个寄存器变量cnt_scan和cnt,用来对输入的时钟信号进行计数和对位选信号进行计数。定义sel为位选变量显示数码管的位选信号,通过寄存器变量sel_r给数码管的位选送出信号。定义seg为段选变量显示数码管的段选信号,通过寄存器变量seg_r给数码管各个段选送出信号。位选扫描先判断是否有复位信号,若有给sel_r赋值8′b0,若没有则逐个显示对应位置的数码管。定义寄存器变量seg_r_miao1、seg_r_miao2、seg_r_fen1、seg_r_fen2、seg_r_shi1、seg_r_shi2为时、分、秒的十位和个位数。段选驱动首先判断是否有复位信号,若有则给对应的时、分、秒的寄存器变量赋值8′hff,否则给对应的十位数和个位数赋值段码显示16进制值。

图7 译码显示模块Fig.7Diagram of the decoding display module

2.5 外设硬件电路

2.5.1 时钟电路

所有的频率都是从晶振上分频而来的,晶振可以分为有源和无源[15]。无源晶振需要外部的设备影响才能产生震荡信号。有源晶振则是完备的振荡器,所以在FPGA开发板上采用有源晶振。有源晶振有四只引脚,是一个完整的振荡器,器件内部除了石英晶体外,还有晶体管和阻容元件。输出端串接100Ω和0Ω电阻,以方便时钟电路调试,图8所示为时钟电路原理图。

图8 时钟电路原理图Fig.8The schematic diagram of clock circuit

2.5.2 复位电路

电源是整个模块和各个模块正常运行及工作的基本保障,如果电源设计不合理,将导致整体模块和各个模块的无法正常工作。

大多数复位电路的设计都是采用低电平有效的方式,有些单片机则是高电平有效的方式。多数的复位电路可以分为芯片复位和阻容复位。芯片复位比阻容复位稳定,阻容复位则比芯片复位更容易发生抖动。常用的复位芯片有MAX708S/706S系列和IMP811。芯片复位有高、低电平复位方式,阻容复位只有低电平复位方式,但价格低廉且体积小,其原理图如图9所示。

图9 复位电路原理图Fig.9The schematic diagram of reset circuit

3 系统调试及运行结果分析

3.1 编译结果

FPGA的主控芯片选择Altera公司推出的EP2C5T144C8-FPGA开发板(简称EP2C5开发板)。EP2C5开发板是Cyclone II系列EP2C5T144C8芯片作为核心处理器进行设计的,主要向广大的高校相关专业学生、电子爱好者、科研单位的开发设计人员,同时比第一代EP1C6等芯片的设计上、内部的逻辑资源上都有很大的改进,而且价格被广大客户所接受,具有较高的性价比。

对顶层模块和各子模块进行编译[16-19],编译成功。编译结果如图10所示,总逻辑元件(Total logic elements)256个,总组合功能(Total combinational)240个,专用逻辑寄存器(Dedicated logic registers)132个,总寄存器132个。

图10 编译结果Fig.10The compiled result

在调试之前,需要检查硬件是否连接正确,确认接口和开发板的下载口的连接,确认接地线、电源线的连接,数码管的显示是否正常。

3.2 分频模块和计数校时模块仿真

3.2.1 分频模块仿真

分频模块的功能是把数字时钟系统的50 MHz时钟输入信号分频为1 kHz和1 Hz的时钟信号。该模块主要由4个always块组成,分别实现时钟信号的计数和使能信号的输出。以下Verilog代码主要描述分频1Hz时钟信号的实现过程,仿真图如图11所示。

图11 分频模块仿真图Fig.11Simulation result of the frequency division module

分频模块的设计采用时钟使能的设计方法。50 MHz时钟输入信号和复位信号为clk_50 MHz和RST。对于分频1 Hz的时钟信号,可以定义一个寄存器变量cnt1用于计数,每经过一个clk_50 MHz时钟信号的上升沿cnt1计数一次,当cnt1计数到49 999 999时输出1 Hz使能信号clk_en1,同时cnt1清零。分频1 kHz信号同理。

3.2.2 计数校时模块仿真

计数校时模块具有计数和校时的功能,以24小时为一个周期不断的循环计数。该模块主要由3个always块组成,分别实现秒钟、分钟和小时的计数。仿真图如图12所示。

图12 正常计数的仿真图Fig.12Simulation result of normal count

为了方便观察仿真图,将时钟分频参数改成TIME_1S=5。也就是说cnt1计数到4时输出1Hz的使能信号clk_en1。由仿真图可知,每当使能信号clk_en1经过时,数字时钟就会加1计数;若计数状态处于23:59:59,秒再进行一次计数,则对应时、分、秒的显示全部清零,并从零开始重新计数。

在数字时钟正常计数时,若接收到调时、调分或调秒信号时,会调整相对应的时间。仿真图如图13~15所示。

图13 调整小时仿真图Fig.13Simulation results of adjusting the hour

图14 调整分钟仿真图Fig.14Simulation results of adjusting the minute

图15 调整秒钟仿真图Fig.15Simulation results of adjusting the second

由仿真图可知,在数字时钟正常计数过程中,不论使能信号clk_en1是否到达,只要检测到输入信号就会立即调整时间。当zhuangtai信号为1时,若UP信号为1,则对应小时位shi加1,若DN信号为1,则对应小时位shi减1。zhuangtai信号为2时,若UP信号为1,则对应分钟位fen加1,DN信号为1,则对应分钟位fen减1。zhuangtai信号为3时,若UP信号为1,则对应秒钟位miao加1,若DN为1,则对应秒钟位miao减1。

3.3 调试结果

待显示模块可以正常运行后,再对计数模块进行调试,如图16所示。

图16 计数调试Fig.16Diagram of counting debugging

4 结 论

(1)笔者使用Quartus II软件时的设计是采用自顶向下的方法,对分频、计数校时、译码显示模块用Verilog HDL 语言进行编程并仿真验证其正确性。各子模块的代码在Modelsim下编译通过,由仿真图可见实现了数字时钟的基本功能;在Quartus II上调出各模块的框图,设整体模块为顶层模块,并综合编译、分配引脚、编译成功后在FPGA开发板上进行调试验证,调试结果基本符合设计要求。

(2)在设计过程中需要尽早查找发现错误并修改,以免发生重复设计;FPGA的开发板,可以实现各种数字产品的功能,提高了检查的效率,体现了在利用FPGA开发数字产品时的优越性。