基于STM32 的数字正交锁相放大器设计

2022-08-06李胜铭苏子粱吴振宇卢湖川

李胜铭, 苏子粱, 吴振宇, 卢湖川

(大连理工大学创新创业学院,辽宁 大连 116024)

0 引 言

遇到微弱信号或信噪比较低的信号时,锁相放大技术能以较高的灵敏度检测出所需的信号,因而是许多仪器仪表的信号处理方法[1-3]。微处理器系统中,使用数字信号处理(DSP)技术实现的锁相放大技术较模拟方式能显著提高测量稳定度及抗噪声能力,降低系统成本,适合作为智能仪表的信号检测方案[4-6]。本文以STM32 微处理器为例,设计了数字锁相放大器,并以交互方式展示数字锁相放大器工作效果与指标参数。

1 总体设计方案

为体现数字正交锁相放大器对信号幅值与角度的分辨能力,系统中设计了一个音频产生与接收装置,通过测量经空气传输的音频信号在不同距离下衰减与相移,从而探究噪声对信号的干扰。在此基础上,系统通过蜂鸣器产生固定频率方波信号,验证数字正交锁相放大器的频率选择特性。

如图1 所示,系统以STM32 微处理器为核心,由微处理器完成音频信号接收与产生,通过带触摸功能的TFT显示屏完成人机交互。其中,驱动蜂鸣器发生的方波信号在空气中传播后通过驻极体麦克风采集,经前级放大输入到微处理器中。微处理器对输入信号进行数字正交锁相放大,得到信号各频率分量的幅值与相位,并通过显示屏显示。为定量测量系统性能,采用将待测的正弦波信号源与噪声信号叠加,通过选择开关选通的方式,从而与产生的参考信号比较评估数字锁相放大器的性能。

图1 系统设计框图

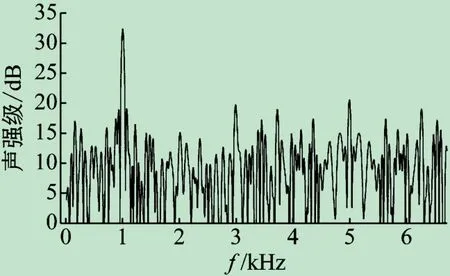

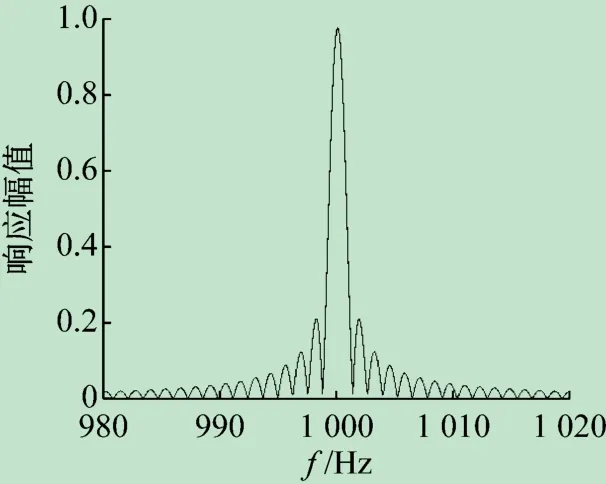

设计中,使用1 kHz方波驱动蜂鸣器发声,方波信号与外界噪声叠加后有着复杂的频谱,如图2 所示。因为频率分量丰富,常规办法难以对有效信号进行提取与测量。

图2 1 kHz方波驱动蜂鸣器发声信号频谱图

2 系统硬件设计

2.1 主控制器

主控制器选用STM32F767IGT6 微处理器,其为带DSP和FPU的高性能ARM Cortex-M7 内核,工作频率可高达216 MHz[7]。其内置模数转换器(A/D)模块,拥有18 个定时器,可以在不使用外部器件的情况下完成信号采样、方波输出等任务。片上的浮点处理器(FPU)也有助于快速完成相关的信号处理运算。

2.2 显示屏

为充分显示信号图形数据,系统显示屏采用分辨率为800 ×480 的LCD-TFT 面板。显示屏显示的信号为输入信号的幅值、相位以及微处理器片上A/D采样的波形,以便观察输出信息与排查故障。显示屏包含一片由GT911 芯片控制的电容触摸屏,用于人机交互,从而调整系统工作参数。

2.3 音频采样及蜂鸣器电路

音频采集需要频率范围宽、高保真且小体积的电-声换能器,驻极体麦克风的性能优异,符合系统音频采集设计要求。驻极体麦克风的输出电阻较高,一般在内部集成有阻抗变换电路(常由场效应管组成),经阻抗变换后输出电阻小于2 kΩ[8]。为保证驻极体麦克风内部电路正常工作,需要提供偏压(常采用偏置电阻的方式)。

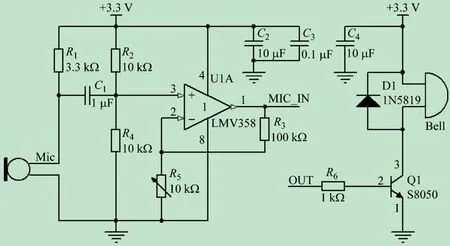

如图3 所示,R1为驻极体麦克风偏置电阻。系统中使用LMV358 芯片构成正向比例放大器,从而实现麦克风信号放大。为使得输入信号满足STM32 微处理器A/D模块的量程范围,C1进行隔直,R2与R4构成偏置电路,使得信号可以输入微处理器中供下一步处理。放大电路的倍数由R3与R5决定,其中R5采用可变电阻,因此调整此电阻可改变放大器的增益。

图3 音频采样与蜂鸣器电路图

音频信号的发生通过有源蜂鸣器实现,其使用S8050 三极管构成的开关电路驱动,并在蜂鸣器上反向并联二极管以快速释放反向电流。为便于检验锁相放大器的抗噪声性能,蜂鸣器使用方波信号驱动。

3 算法及程序设计

3.1 数字正交锁相放大器设计

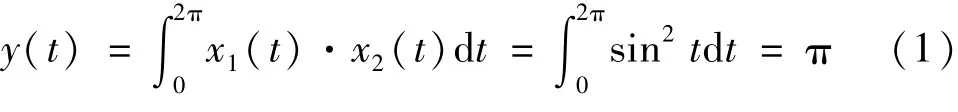

锁相放大使用互相关检测原理实现信号的检测[9-11]。锁相放大器包含两个输入,其中一个为同频同相参考信号,而对于正交锁相放大器,其功能上包含两个锁相放大器,因此需要两路正交的参考信号。对于与参考信号同频同相的输入信号x1(t)与x2(t),在1 个周期内,其积分不为零,

而对于不同频率的信号,在足够长时间的积分后,其值趋向于零。此为三角函数正交性,因此可以将不同频率信号区分。

由于噪声的带宽一般较宽,而锁相放大器等效于一个窄带滤波器,噪声经过处理后其功率降低,使得信号的信噪比提高。以常见的低通白噪声为例,若其噪声功率谱密度为Sni,带宽为Bni,则输入噪声均方值

若系统的功率增益为G,带宽为Be,可得其输出噪声均方值

设信号输入电压为Usi,输出电压为Uso,则有:

根据式(2)~(4)即可求得信噪改善比(SNIR):

由式(5)可知,信噪改善比取决于噪声带宽和系统带宽之比。系统带宽越小,信噪改善比越好。而锁相放大器的带宽可以做到小于1 Hz,因此其抗噪效果是数字带通滤波器难以达到的。考虑到锁相放大器参考信号与待测信号在频率上需要严格同步,因此系统中使用内部时钟源并进行时钟同步[12]。

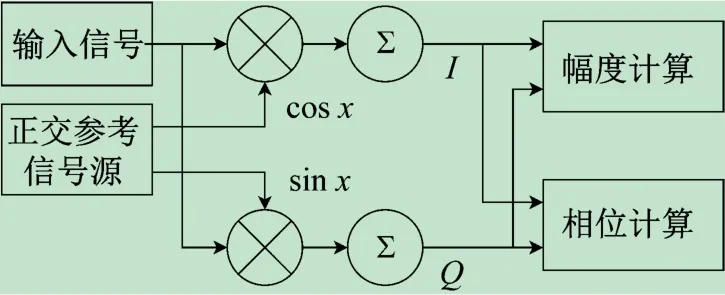

对于数字信号处理系统,使用乘加的系统结构,计算输入信号与参考信号的乘积,并积分得到最终结果,能大幅降低计算量,得到更好的性能[13-15]。对于正交锁相放大器,将同相输出I与正交输出Q分别进行计算,对于已知的输入信号频率fn与采样频率fs有:

对于输入信号的幅度与相位,可分别通过下式计算:

可知系统输出与输入信号幅值相关,而与初始相位、噪声无关。由于arctan 函数值域仅为(-π/2,π/2),为求得四象限角度,系统中使用C 语言库头文件math.h中atan2 函数,其取值

即可得知输入信号在参考频率处的幅度与相位,并使得无用信号与绝大部分噪声因互相关为零而被滤除。其在微处理器上的实现结构如图4 所示。

图4 数字正交锁相放大器实现结构框图

系统中,微处理器产生频率为1 kHz方波,并使用100 kS/s采样速率采样,若要求数据刷新时间小于1 s,积分点数应控制在1 ×105点以内,并为缓冲区大小的整数倍。系统采用长度为512 点的缓冲区,采用99 840 点积分,从而兼顾数据刷新速度同时,使得采样信号带宽足够窄。对此锁相放大器设计的频率特性进行仿真,如图5 所示,此时系统具有优异的选频能力,半功率带宽为0.46 Hz。

图5 数字锁相放大器的频率响应

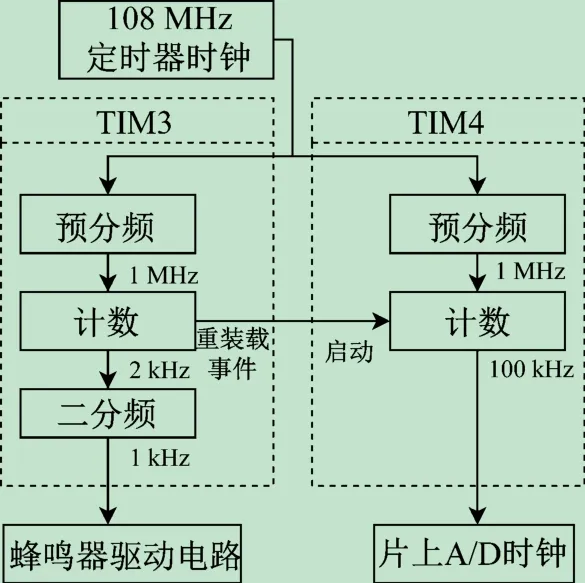

3.2 程序设计

为保证系统内部参考信号与蜂鸣器输入信号初始相位同步,使用2 个定时器产生所需信号。其中定时器4(TIM4)用于模数转换器触发,定时器3(TIM3)用于输出方波,使用定时器同步功能,使得两个定时器有同样起始值。定时器同步设计如图6 所示。

图6 定时器同步结构图

为减少对处理器占用,模拟信号采样使用直接存储器访问(DMA)方式。DMA 单次传输512 个采样点作为1 个数据帧,并使用双缓冲方式使得DMA传输与数据计算同步进行。在微处理器处理1 帧数据时,DMA可直接控制系统总线,采样并传输下1 帧的数据,通过交换2 个缓冲区的功能,实现计算资源利用最大化。

在软件实现上通过编写DMA 传输完成回调函数,并通过计数变量实现计算点数的处理,使用全局变量保存计算的中间结果,DMA传输完成回调函数流程如图7 所示。

图7 DMA传输完成回调函数流程图

数字正交锁相放大计算中,包含大量的三角函数计算,如何加速三角函数计算是效率优化的重点,对于固定的计算,可以利用函数表解决[16],而函数表会限制待测频率与采样速率。系统中使用ARMCMSIS-DSP专用库,利用函数表进行线性插值处理,能产生任意频率的参考信号且速度可调整,提升了程序的通用性。

3.3 实验流程设计

实验流程设计如下:①连接系统电路,编译并烧录代码。②将示波器通道连接蜂鸣器引脚,观察输出波形,确认波形正常,程序工作。③将信号发生器接入示波器另一通道,调整信号发生器频率以保证其与微处理器输出频率相位一致。④选择正弦波信号源作为输入信号,改变信号幅度,并调整噪声源输出幅度,记录系统测量结果。⑤测量完成且确认系统工作正常后,将麦克风、蜂鸣器接入系统。⑥观察并记录麦克风与蜂鸣器距离变化对系统示数的影响。

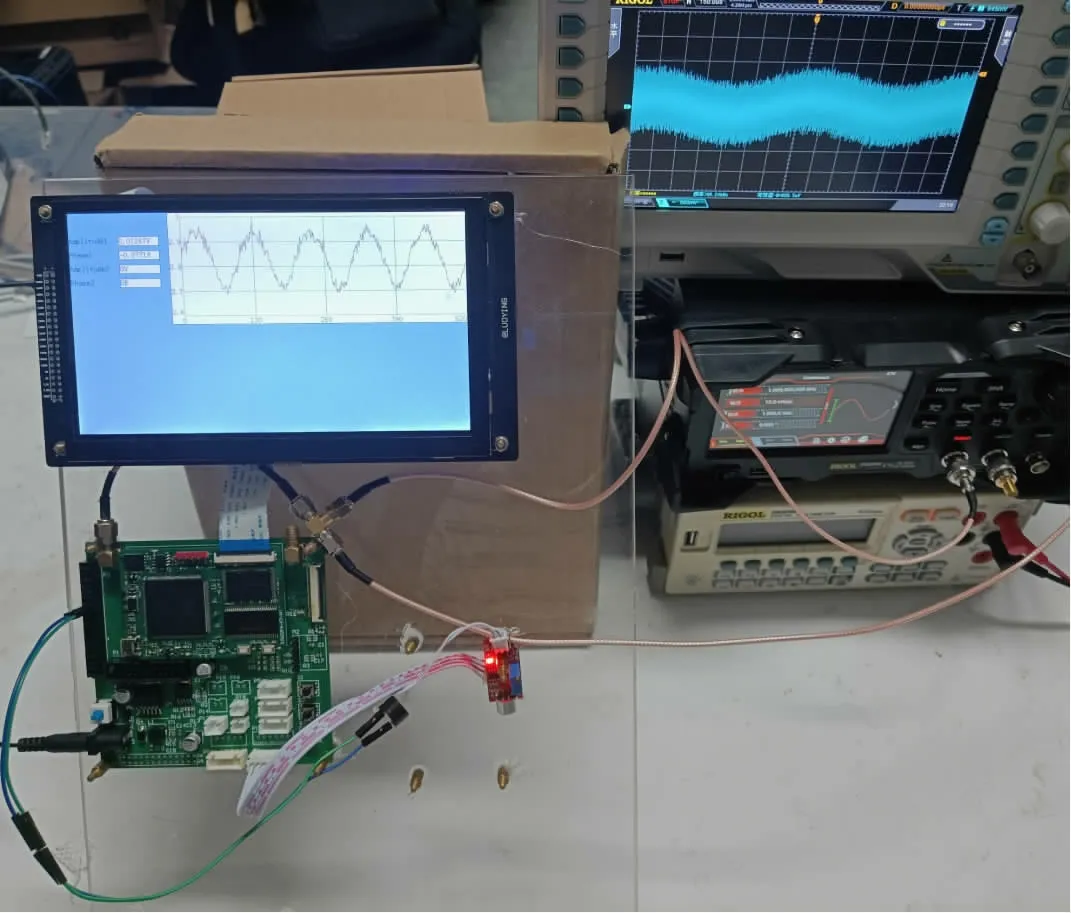

4 系统实物测试

在仿真基础上,制作的实物如图8 所示,其可实时显示测量信号的幅度及相位,并绘制显示模数转换器采样得到的数据。通过移动蜂鸣器可看到接收信号幅

图8 基于STM32的数字正交锁相放大器实物

度及角度均发生变化,并可以此推断麦克风与蜂鸣器的距离。

实验过程中,可以改变麦克风前级放大器增益,或将实验装置置于不同声音环境中观察实验现象。

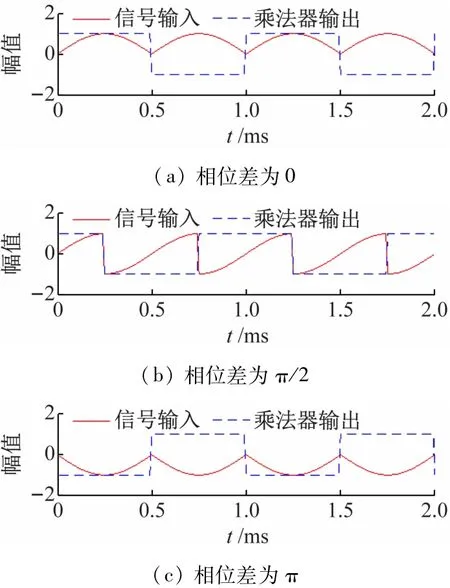

为便于观测系统工作状态是否正常,接入1 kHz激励信号,将锁相放大器乘法器后、积分器前的内部信号通过数模转换器(D/A)输出,并通过示波器显示。图9 为输入信号与内部参考信号相位差分别为0、π/2、π时内部乘法器输出。

图9 输入信号与内部信号不同相位差时波形

进行Matlab 仿真的结果如图10 所示,其与实测波形相似,输出信号与激励信号相位的差异为数据处理产生的延时,可见内部参考信号发生器及乘法器均正常工作。

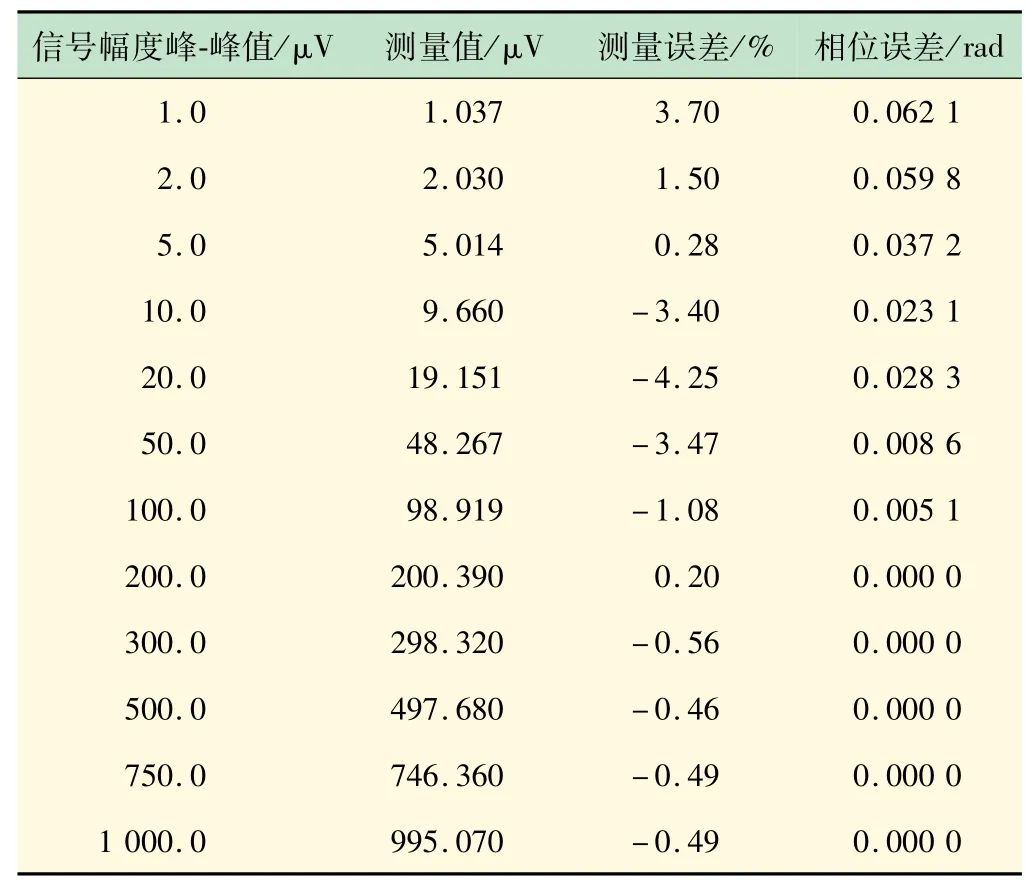

通过测量正弦信号输入幅度误差及相位误差评估所设计锁相放大器性能。此时将噪声源关闭,在系统输入端串联放大倍数为60 dB 的前级放大电路,改变正弦波信号源的幅度,观察并记录数据(见表1)。得到的正弦信号幅度误差于相位误差如图11、12 所示。

由表1 及图11 可知,幅度检测的误差能控制在5%以内。由图12 可知,在激励电压1 μV 以上,相位误差小于0.06 rad。值得注意的是,系统中3 V 参考电压下工作的12 bit A/D的化误差为0.4 mV,而前级放大输入端的输入电压仅为4 μV。可得知数字正交锁相放大器可用于小信噪比的信号处理场合,尤其适合相位测量相关应用。

图10 内部信号不同相位差时仿真图

表1 正弦小信号检测表

图11 正弦信号幅度误差

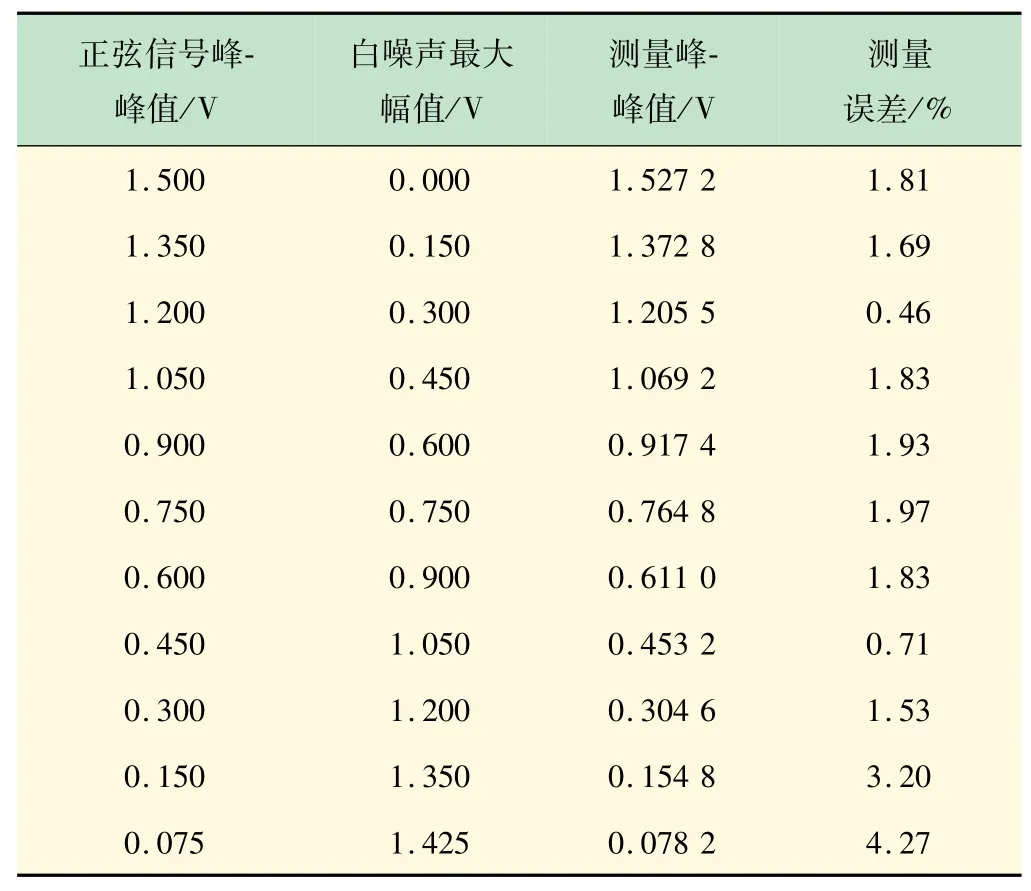

系统抗噪声性能测量,通过信号发生器提供按比例混合的同频率正弦信号及均匀白噪声输入系统,记录读数与输入信号混合比例关系,测量前通过示波器将信号发生器的频率校准到微处理器输出频率。在0% ~95%范围内混合正弦信号与均匀白噪声,记录并整理系统输出结果如表2 所示。

图12 正弦信号相位误差

表2 噪声影响记录表

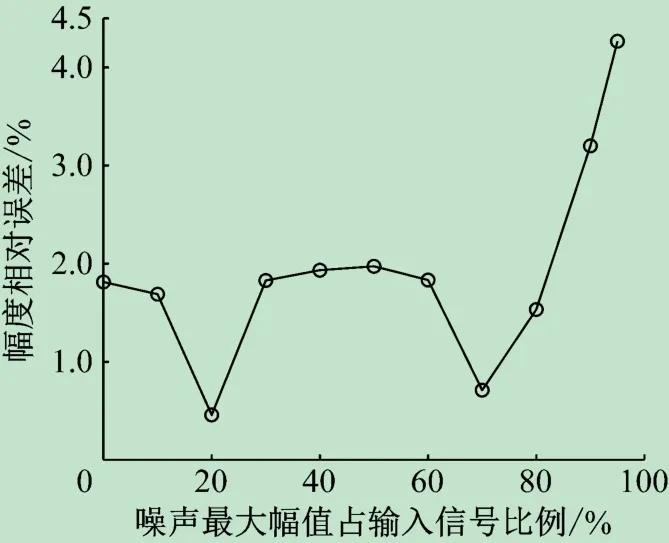

系统噪声影响下所测量的幅度误差如图13 所示。

图13 噪声影响下幅度误差

由图13 可知,系统在噪声幅度为系统输入信号的95%时,幅度测量误差最大,为4.27%。因此,在强噪声环境下所设计的数字正交锁相放大器依然对信号有很强的分辨能力。

5 结 语

本文设计了基于STM32 的数字正交锁相放大器,通过理论分析与实验测试验证了该锁相放大器的性能。在嘈杂环境下,肉眼难以分辨波形时,该锁相放大器仍可分离出所需的信号。在教学实践活动中,可让学生直观感受数字锁相放大器性能,从而进一步设计提升指标与扩展应用场景。