一种应用于FPGA的低功耗控制方法

2022-08-02李晓龙陈琳谢林峰

李晓龙,陈琳,谢林峰

(四川九洲电器集团有限责任公司,四川绵阳,621000)

1 FPGA功耗组成

FPGA的功耗由静态功耗与动态功耗组成。静态功耗是FPGA配置完成后,所有供电轨道与电路引脚的漏电流形成的功耗。加入空bit后,该bit设置所有的相关管脚为高阻态,即可完成FPGA静态功耗的测试。动态功耗与具体的设计相关,由供电水平、消耗的逻辑、电路开关率与布线资源决定。本文以降低FPGA的动态功耗为目标,选取典型的通信信号处理电路作为逻辑设计,在此基础上探讨动态功耗降低方法。

2 逻辑电路设计框图

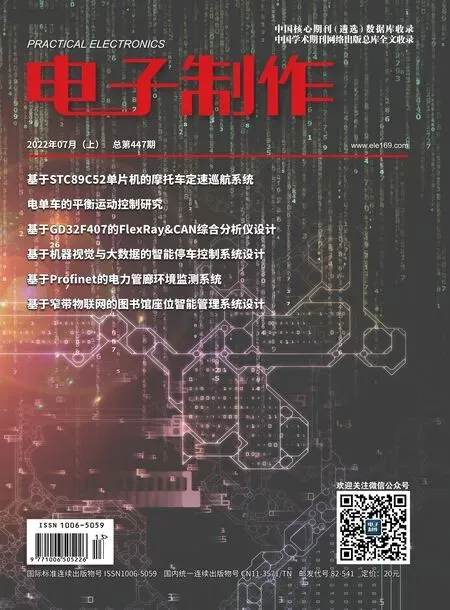

通信信号处理逻辑电路从功能上划分可分为发射、接收、控制三大部分,其中发射电路主要包括扩频模块、编码模块、DDS控制模块,接收电路主要包括DDC模块、解码模块、解扩模块、相关峰判断模块、解调模块、数据上报模块。发射、接收两大部分电路分时工作,因此,发射、接收两大部分电路可设计时钟使能接口,由控制电路产生使能信号,按照一定的时序控制发射/接收电路。具体如图1所示。

图1 逻辑电路设计框图

3 接收电路信号处理

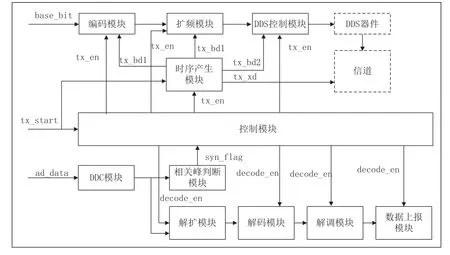

按照数字接收的处理流程:数字下变频→同步→解调→解码→上报数据,AD送出的数字信号,经过上述流程,采取流水线结构,即可实现数据的实时接收、解码。为了降低接收电路的动态功耗,进一步分解接收电路的工作状态:

数字下变频、同步过程处于实时接收状态,即数字下变频模块(DDC)、相关峰判断模块实时工作;

解扩、解码、解调、上报数据过程处于受控状态,即经过数字下变频模块与相关峰判断模块处理后,若能正确同步,则使能解扩模块、解调模块、解码模块、数据上报模块,若无法正确同步,解扩模块、解调模块、解码模块、数据上报模块则继续处于休眠状态。

控制模块接收同步标志syn_flag,产生一定宽度的高脉冲使能信号decode_en,控制后续处理电路的状态,此时,发射电路部分处于休眠状态。各模块功能如下所述:

(a)ad_data为模数转换器ADC采样所得的数据,其采样频率一般与FPGA的主要工作频率相同;

(b)通过并行接口与FPGA相连,将ad_data送至FPGA;

(c)DDC模块接收ad_data,经过数字下变频、数字滤波将ad_data下变频至基带;

(d)DDC模块一直处于工作状态,采取流水线结构,将处理后的数据送至相关峰判断模块;

(e)相关峰判断模块采用本地产生的扩频码与原始基带数据作滑动相关,实时计算相关后的能量值;

(f)相关峰判断模块一直处于工作状态,将实时计算得到的能量值与同时计算的动态门限值作比较,根据比较结果与峰值判断条件共同录取相关峰;

(g)若录取到的相关峰个数满足一定的条件,如peak_num>n(n可 取4,6,8)个,则判定同步成功,输出同步标志syn_flag;

(h)控制模块接收syn_flag标志,根据当前工作状态,输出decode_en信号;

(i)解扩模块在decode_en信号有效前,一直处于休眠状态,当decode_en信号有效后,则立即工作,接收DDC模块输出的数据段基带信号,使用本地产生的扩频码进行相关,并将相关后的结果送至解调模块;

(j)解调模块在decode_en信号有效前,一直处于休眠状态,当decode_en信号有效后,进行BPSK解调,并将解调后的信号送至解码模块;

(k)解码模块在decode_en信号有效前,一直处于休眠状态,当decode_en信号有效后,则开始对数据段基带信号进行解码;

(l)数据上报模块在decode_en信号有效前,一直处于休眠状态,当decode_en信号有效后,则按一定格式组织解码后的数据,完成数据上报。

接收电路信号处理如图2所示。

图2 接收电路工作流程图

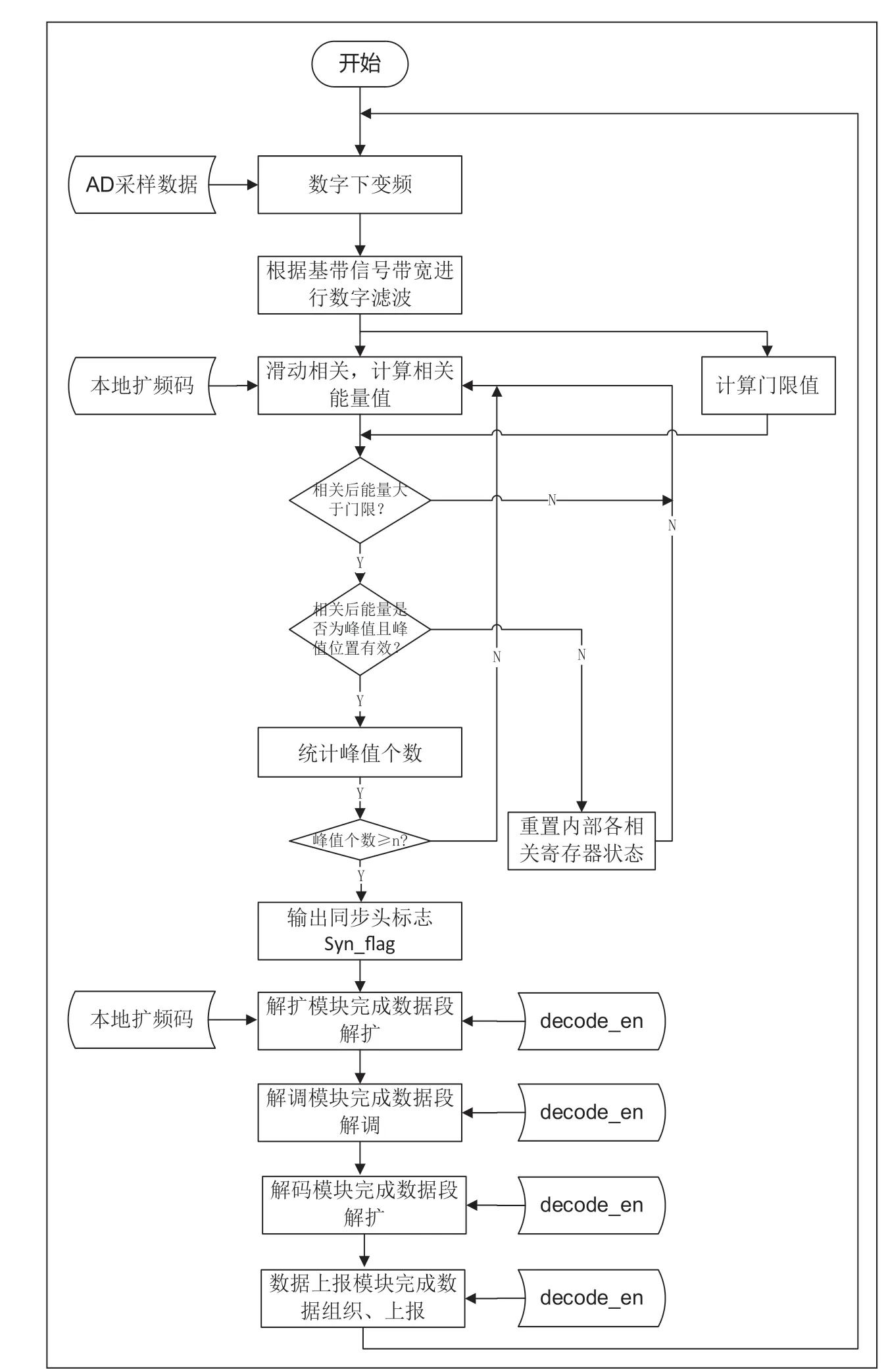

4 发射电路信号处理

依据电路分时工作的特性,发射电路的工作状态切换受到接收电路的信号处理的影响。当接收电路正确解码且组织好一定数据后,发射电路开始正常工作,其余时间,发射电路处于休眠状态,即编码模块、扩频模块、DDS控制模块、时序产生模块的时钟使能信号tx_en无效。各模块功能如下所述:

(a)base_bit为原始基带数据,采用串行方式输入进编码模块进行编码;

(b)编码模块、扩频模块、时序控制模块、DDS控制模块在时钟使能信号tx_en有效前,一直处于休眠状态,当时钟使能信号tx_en有效后,则切换至工作状态;

(c)编码模块主要完成原始数据的编码,加入错误校验信息bit,增强纠错能力,编码方法采用卷积编码;

(d)扩频模块依据参数产生扩频码,并综合扩频码与卷积编码信息bit,完成扩频;

(e)编码后的基带信息bit上变频至中频采用数字频率合成的方法,依靠DDS器件(典型如AD9954)完成上变频与BPSK调制,DDS主要寄存器说明见第3节;

(f)DDS控制模块完成DDS器件状态设置、参数配置,并将编码后数据信息送入DDS器件,完成BPSK调制与上变频;

(g)时序控制模块则完成发射时模块工作、信道发射支路使能信号的控制,如tx_bd1、tx_bd2、tx_xd信号的置位。

发射电路信号处理流程图如图3所示。

图3 发射电路工作流程图

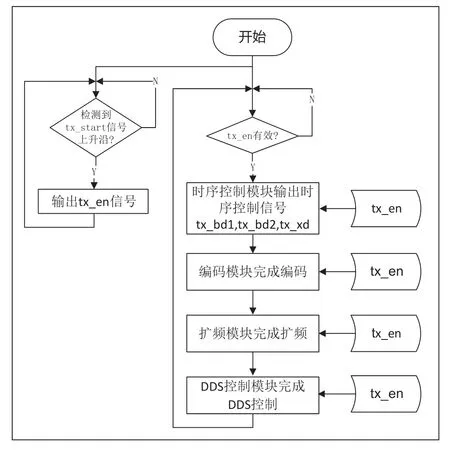

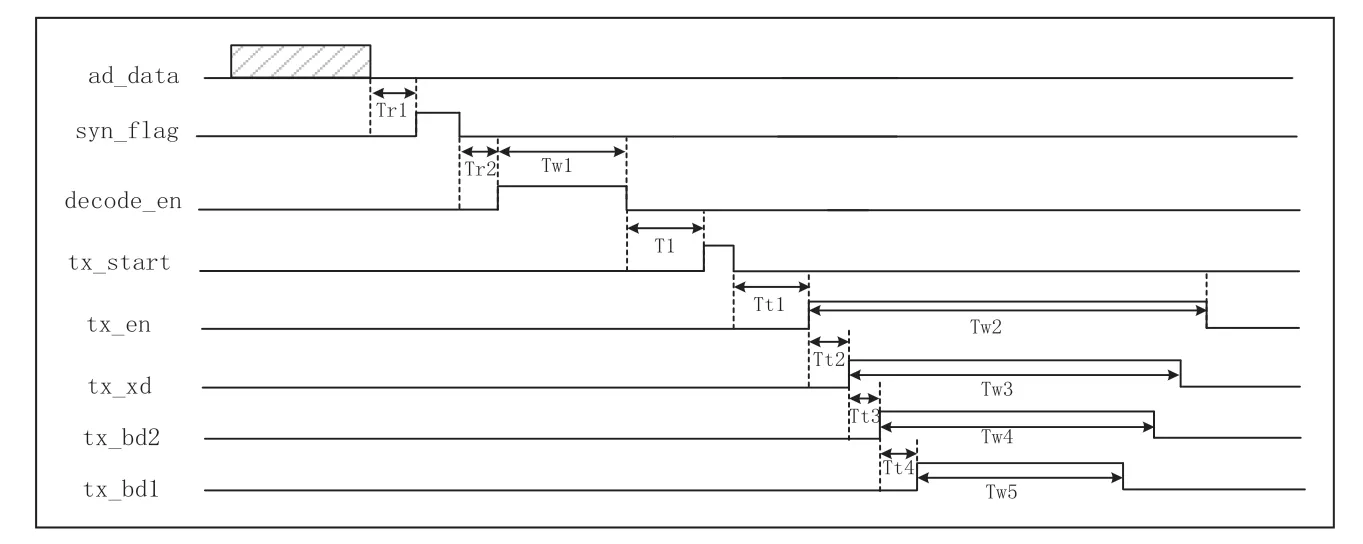

信号时序图如图4所示。

图4 信号处理使能信号时序图

其中Tr1为接收到ad_data到生成同步头标志syn_flag的处理时间,Tr2为生成decode_en的处理时间,Tw1为decode_en信号有效的时间,其在同步后接收数据时间段一直有效。T1为接收/发射转换所需时间,Tt1为发射开始信号到tx_en信号有效的处理时间,Tw2为发射使能信号tx_en有效的时间,其在发射时间段一直有效。Tw3为信道发射支路使能信tx_xd号有效时间,其宽度略小于Tw2,在发射时间段一直有效。Tw5为tx_bd1信号有效时间,其宽度等于发射时间段,Tw4为DDS器件工作使能信号tx_bd2有效时间,其宽度略大于Tw5时间,Tt4为预留的DDS器件的响应时间。Tt3+Tt4为预留的信道响应时间。

5 AD9954控制

AD9954是由ADI公司研发的一款低功耗、高性能直接数字频率合成器。其内部集成14位高性能DAC,内部最大时钟频率为400MSPS,具备多种模式,支持相位调制、频率调制等工作模式,其配置包含内部VCO配置、频率字、相位设置等方面,相关寄存器控制说明如下所示:

(1)CFR1寄存器主要实现模式控制等内部控制指令,为 实 现BPSK调 制,可 置 位“RAM Enable”,“OSK Enable”等控制bit,使能内部RAM与开启OSK调制;

(2)CFR2寄存器主要完成内部VCO配置与AD9954输出的幅度控制。使用内部VCO生成系统工作时钟时,“REFCLK Multiplier”设置倍频系数,此时需注意VCO工作频段。当VCO工作在100MHz至250MHz时,“VCO Range”设为0,当VCO工作在250MHz至400MHz时,“VCO Range”设置为1。输出的幅度值由“Amplitude Scale Factor Register”控制;

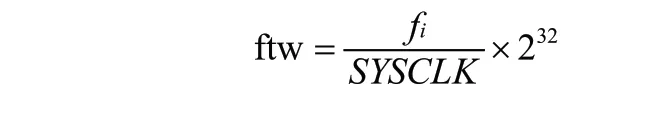

(3)FTW0寄存设置输出信号的频率,可根据输出信号的频率与公式计算FTW0寄存器值。计算公式为:

(4)由AD9954实现BPSK的具体思路为:采用RAM模式,RAM空间0存储相位值“0”,RAM空间1存储相位值“π”。当FPGA输出bit 0时,器件内部的相位偏移模块“PHASE OFFSET”选择RAM0的数据,即相位值“0”。当FPGA输出bit 1时,“PHASE OFFSET”选择RAM1的数据,即相位值“π”,从而实现输出信号相位的快速切换,切换时间为24个系统时钟周期,相关寄存器为RSCW寄存器,BPSK需要切换的相位为2个,因此,仅需要配置2个RSCW寄存器RSCW0,RSCW1。

(5)设置RSCW0的RAM起始地址与结束地址,“Ramp Rate”设为0。设置RSCW1的RAM起始地址与结束地址,“Ramp Rate”设为0。

(6)按步骤(5)设置的地址向RAM写入相位数据,即相位值“0”写入0,相位值“π”写入“0x80000000”。

(7)存储相位值的RAM0,RAM1由相对应的管脚PS0控制,即当PS0为0时,选择RAM0的数据,当PS0为1时,选择RAM1的数据,从而实现相位切换。

作为发射支路上实现上变频的部件,AD9954同样具备功耗控制接口。有寄存器与管脚控制两种方式控制DDS的工作状态。配置寄存器CFR1的“Digital Power Down”、“Comp Power-Down” 与“DAC Power-Down”bit,即可完成对器件内部数字电路、比较器与DAC的电源控制。也可采用置高“power down”管脚的方式。使用“power down”管脚,可断电器件绝大部分电路。基于本文所涉及的应用场景,最小化动态功耗,采用管脚断电的方式,即在未发射的常态,置高power down管脚,使其处于休眠状态。

6 结束语

经实践证明,该方法能很好的完成通信信号处理,对性能没有影响,能够大幅度降低系统动态功耗。软件全部采用verilog HDL语言进行编写,具有较强的通用性、扩展性和可移植性,同时适用于绝大多数FPGA。对于使用FPGA作为处理核心的通信设备,该功耗控制方法具备一定的借鉴意义。