用于电流舵数模转换器中的静态校准技术

2022-07-30张宏泽

张宏泽 唐 路, 2

(1.东南大学 微电子学院, 南京 210096)(2.东南大学 信息科学与工程学院, 南京 210096)

数模转换器DAC (Digital-Analog Converter)被广泛应用于各种场合,承担着数据转换的重要作用。在许多典型应用下,DAC的性能很大程度上影响了系统整体的性能。不同架构的DAC具有不同的优缺点:电阻分压型DAC线性度良好,但是芯片面积大;二进制加权DAC能节省芯片面积,但是线性度不好;脉宽调节DAC以数字电路为主,一定程度上减小了对模拟电路的依赖,单调性较好,但是很难具有高分辨率;Sigma-Delta型DAC适用于低速高精度场合,但是结构较为复杂。在众多架构的DAC中,电流舵DAC的结构决定了其速度快精度高的特点,因此被广泛应用于高速高精度场合。

电流舵DAC通常由一组电流源和相应的开关组成,差分的开关根据输入的数字信号将电流输出到正相输出端或者反相输出端,每一个输出端的输出可以看作是多组电流的累加,输出的电流可以看作随输入信号变化的阶梯信号,从而达到数字信号转换成模拟信号的功能。电流舵DAC中不同电流源之间存在失配,尤其在高精度的场合,电流源MOS管尺寸大、数量多,电流源阵列面积也会随之增大,造成电流源之间的系统性失配误差大大增加,严重影响DAC的静态性能。

在模数转换器的教材中,极少有关于电流舵DAC的内容,学生可以根据本文更好地了解电流舵DAC的相关知识,并能加深对数字校准的理解。基于此校准方案,电流源MOS管的尺寸可以大大缩小,既减小了整体芯片面积,又优化了系统性失配误差,使校准之后DAC的静态性能有明显的改善。

1 电流舵DAC的原理和静态误差分析

1.1 电流舵DAC的工作原理

电流舵DAC由一组权重不同的电流源以及与其对应的开关组成,根据输入数字码的不同,不同权重的电流源向正相端或者反相端输出电流,从而完成信号的转换。根据输入译码方式的不同可分为二进制译码结构、温度计译码结构和两者相结合的分段式译码结构。参考文献[1]表明,二进制译码结构简明直观,且开关数量少。缺点是随着DAC精度的提高,其电流源之间的失配会急剧增加,导致其性能大幅下降,不适用于高精度场合;温度计译码结构很好地解决了二进制译码结构失配大的问题,但缺点是需要开关个数多,且可能存在较大的毛刺。

提出的校准算法应用于一款14 bits,100 Msps的电流舵DAC中,该电流舵DAC采用了二进制译码和温度计译码相结合的分段式译码结构,分段比为6:4:4,其中高6位为温度计译码结构,转换为63位温度计码后每一位控制大小为256ILSB的高位电流源;次高4位为温度计译码结构,转换为15位温度计码后每一位控制大小为16ILSB的电流源;低四位为二进制译码结构,每一位依次控制大小为8ILSB,4ILSB,2ILSB,1ILSB的电流。文献[2]详细介绍了分段式结构的优点,该结构对两种译码结构的优缺点进行了折中。

1.2 电流舵DAC的静态误差分析

许多误差影响着电流舵DAC的性能,根据对DAC性能影响的不同,主要可分位静态误差和动态误差,本文着重对电流舵DAC静态误差进行分析。

静态误差主要表现在不同输入码情况下,输出单位电流幅值的偏差,它会影响整体系统的线性度。静态误差主要分为两大类,一类是系统性失配误差,另一类则是随机性失配误差。

系统性失配误差主要包含各类的梯度误差,如温度随位置的梯度变化、与工艺相关的参数随温度变化等,文献[3]详细介绍了各类梯度误差对静态性能的影响,过大的芯片面积将会大大增加系统性失配误差,从而导致DAC性能的恶化。

随机性失配误差表现为电流源不能精确复制单位电流,主要受工艺偏差的影响,可能会导致晶体管尺寸、氧化层厚度、阈值电压等参数出现偏差,从而导致电流源之间的失配。文献[4]介绍了随机性失配误差对DAC性能的影响。

公式(1)为参考文献[5]提出的电流失配与MOS管相应参数的模型,其量化了失配与各参数的关系。

(1)

Aβ、AVT为受工艺影响的参数,由(1)式可知,INL有较大的随机性,参考文献[6]提出良率的概念,并引入模型:

(2)

其中C为正态分布积累函数的反函数,良率达到百分之百时,C取值为3.2,如不加入校准算法,每个电流源应满足14位精度,即(2)式中的N=14,代入可得:

(3)

结合具体的工艺参数,可得:

(4)

14 bits电流舵DAC中含有16384个电流源,如果每个电流源按照14位精度去设计,考虑到MOS管面积和走线面积,仅电流源阵列的面积就将至少达到30 mm2,这将会给系统性失配误差带来巨大的影响。

2 静态校准技术

2.1 静态校准技术的思路

综上所述,高精度DAC要求极大的电流源MOS管尺寸,大的MOS管尺寸意味着大的面积,随着面积增大系统性失配误差将严重恶化DAC性能。参考文献[7]提出一种静态校准技术,应用在这一款14位的电流舵DAC中。在校准随机性失配误差的同时,MOS管尺寸也可以大大减小,从而减小了系统性失配误差,从两方面提升了系统的静态性能。

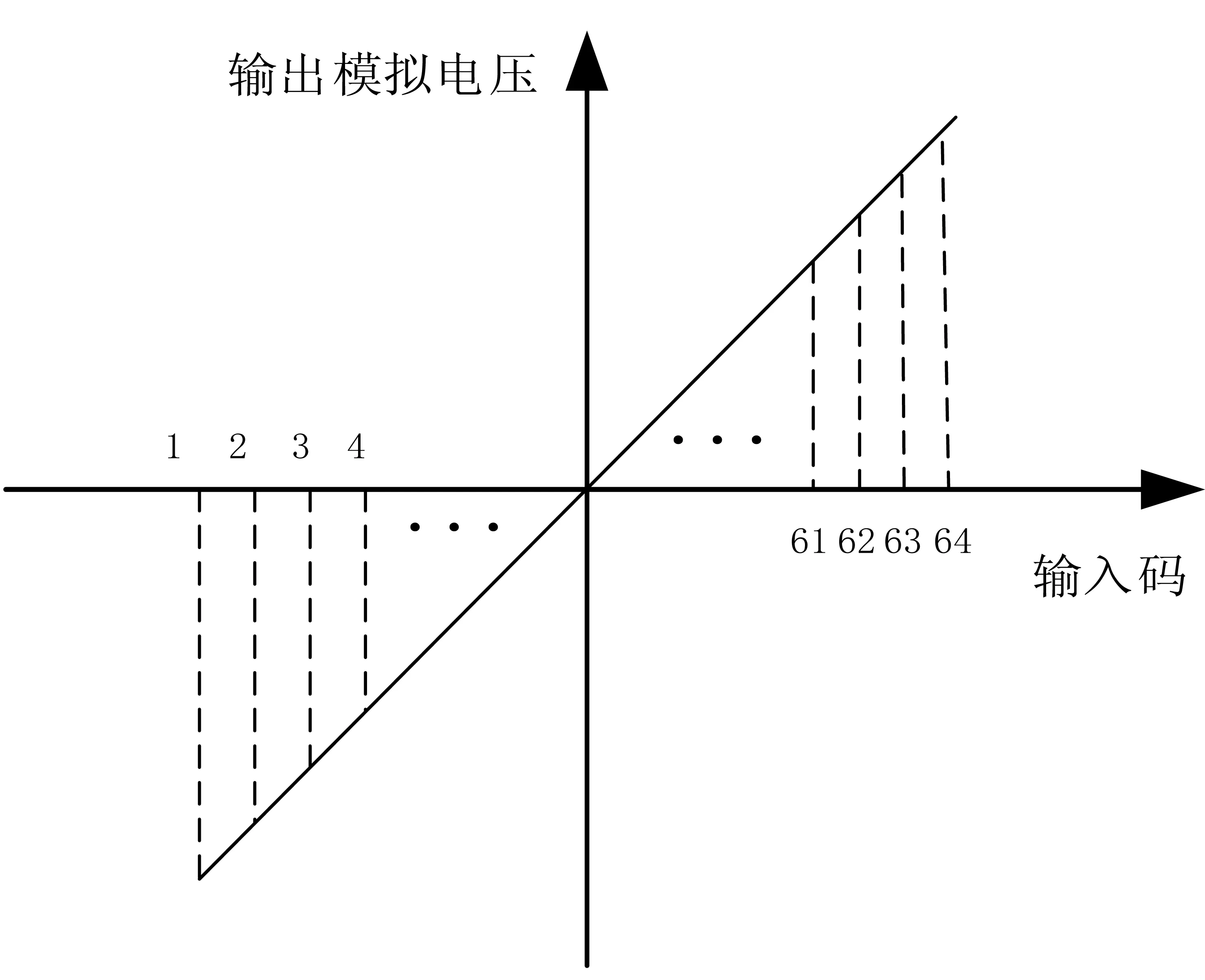

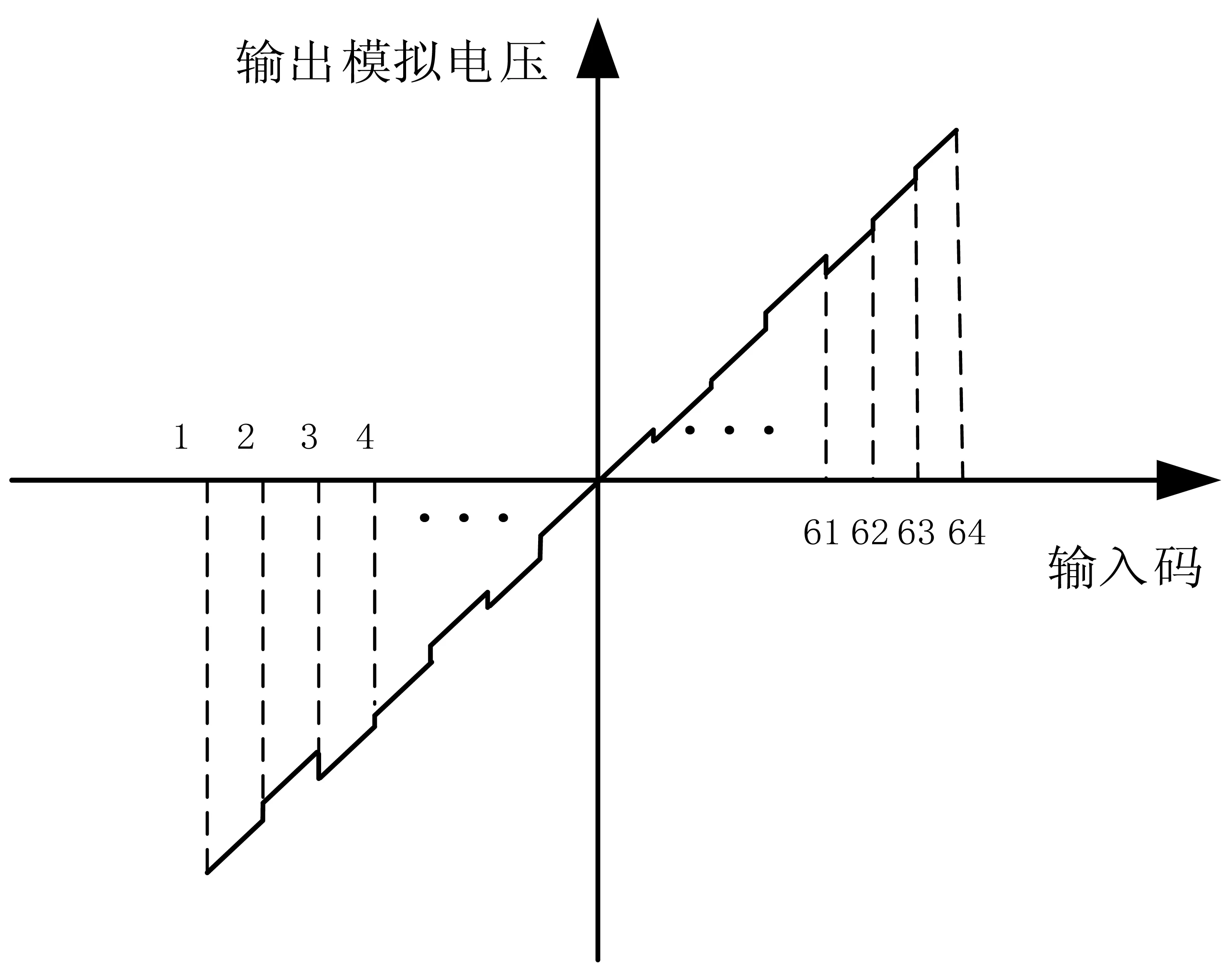

在此高精度电流舵DAC中,高位电流源(MSB)所产生的电流值为单位电流的256倍,引入了极大的失配。通常在电流舵DAC中,高位电流源为主要的误差来源。如图1所示,理想的传递曲线斜率恒定,输出模拟电压随输入数字信号变化均匀变化。图2为实际传递曲线,考虑了电流源之间的失配,高位电流源的失配最大,对DAC静态性能影响最为严重。

图1 理想传递曲线

图2 实际传递曲线

因此,提出一种校准思路:将整个DAC的单位电流源尺寸以8位精度的标准来确定,可以确保低8位的电流满足8位的精度要求,高6位的MSB电流则通过校准来达到14位的精度。即保证图2中63段曲线每一段的斜率相同,再通过校准消除相邻两段曲线的电压差,最终逼近图1的曲线。由于电流源MOS管尺寸按照8位精度去设计,根据(3)、(4)式可以得到单位电流源面积为8.45 μm2,面积缩小了近30倍,大大减小了系统性失配误差。

2.2 静态校准技术的具体实现

采用外加一个8位校准DAC的方法去对高位MSB进行校准,即在DAC的差分输出端跨接一个差分输出的校准DAC。检测出主DAC的差分输出电压与理想电压的差值,其中理想电压根据低位电流源的实际ILSB得到,ILSB为单位电流。通过改变校准DAC的输出,从而得到一个与理想输出电压逼近的差分值。其中8位校准DAC每一位的电流依次为16ILSB,8ILSB,4ILSB,2ILSB,1ILSB,0.5ILSB,0.25ILSB,0.125ILSB,校准范围为(-31.875ILSB—31.875ILSB),即图2中,63段曲线中任意一段曲线只要与理想电压值之间的差值在这个范围内,都能有效校准。

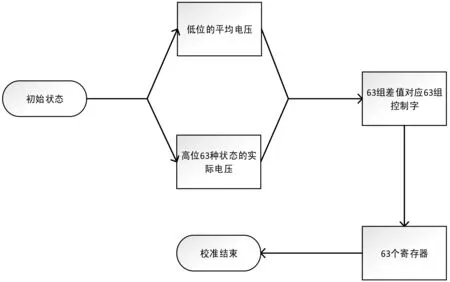

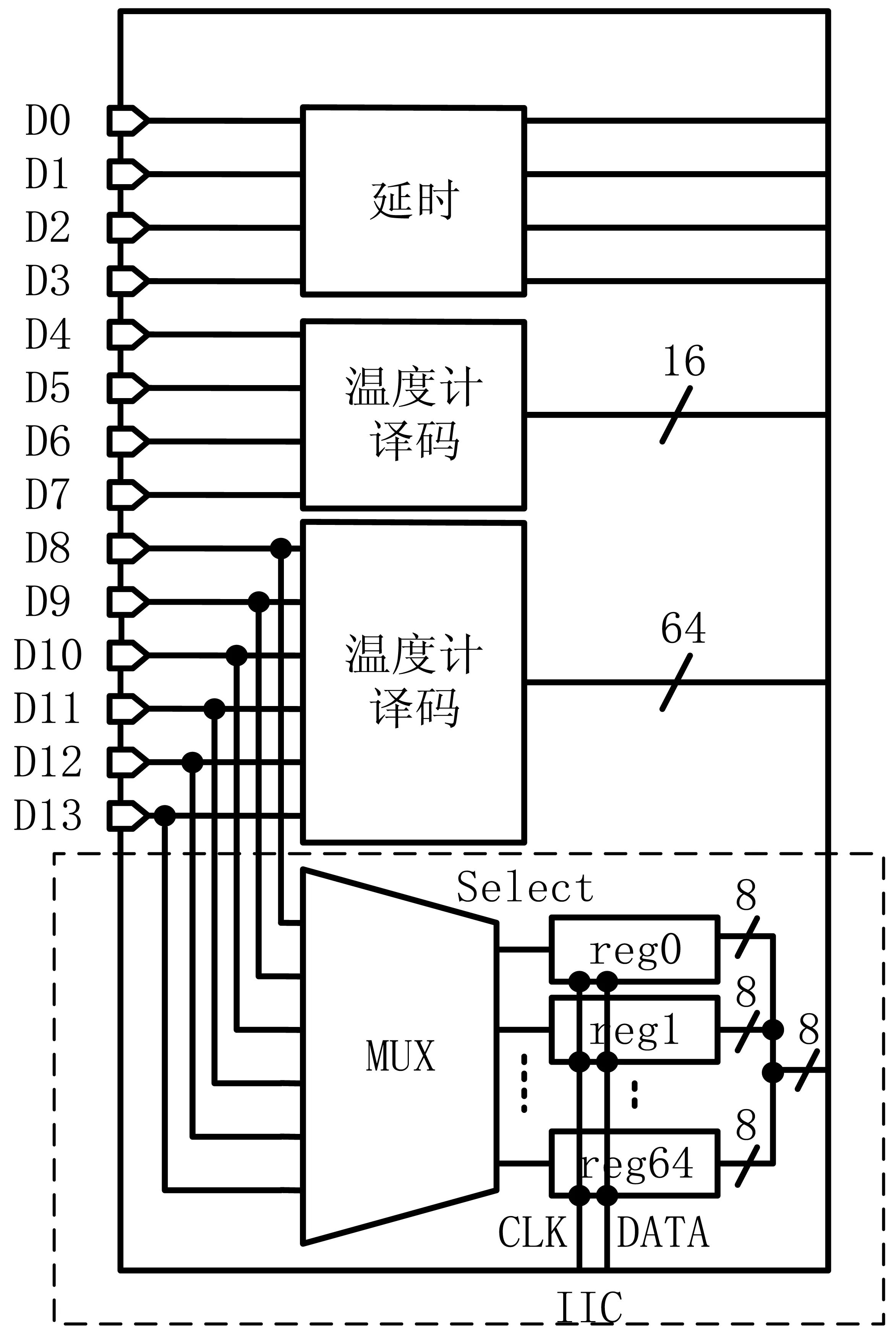

对校准步骤进行详细分析,图3为校准流程图。在初始状态,DAC输入设为14′ b00000000000000,校准DAC输入设为8′ b10000000,用数字万用表测出此时的差分输出电压。接着,将14 bits DAC的低8位输入全设为1,即DAC输入设为14′ b00000011111111,用数字万用表测出此时的差分电压,将这个差分电压减去初始状态的差分电压,取绝对值除2除255,255意为低位每跳变255下,高位改变1,得到用来校准的单位参考电压值VREF。测出单位参考电压后,开始校准高6位的MSB电压。将14位的低8位输入全部置0,高6位的二进制码从6′ b000000变化到6′ b111111,测量每个输入码对应的差分输出电压,与使用单位参考电压VREF计算得到的理想值作差,然后根据比较的情况,得出校准DAC的8位输入控制信号,共64组。例如DAC的输入码为14′ b10001100000000,则输出的理想电压为[2×256 (21+22+25)-16383]VREF,与实际测量差分电压做差,根据电压差通过校准DAC向正相端和负相端补充相应的电流。校准原理图如图4所示:

图3 校准流程图

图4 校准原理图

图4中D0—D13为14位数字信号输入,MUX的输入为14位输入信号中的高6位D8—D13,MUX根据不同的高6位输入信号选择对应的寄存器,将相应寄存器里的控制字作为输出来控制校准DAC。寄存器中的8位控制字是根据高位MSB电压与参考电压VREF差值得到。共有65个寄存器,在非校准状态下,MUX选择reg64,其控制字控制非校准状态下的校准DAC输出。校准状态下,高6位输入信号D8—D13共有64种状态(000000-111111),MUX根据不同的高6位输入信号,选择reg0-reg63中相应的寄存器,寄存器中的控制字作为输出来控制8位校准DAC输出电流补充至正相输出端和负相输出端,使实际电压与理想电压逼近,得到整体更好的性能。

3 仿真结果

设计采用0.18 μm、5 V/1.8 V CMOS工艺,使用spectre和calibre进行后仿真验证。将N=8代入式(3)、(4)中,得到电流源WL应大于8.45。结合式(4)中推导得到的N=14时电流源尺寸为W=1 μm,L=8.5 μm,此尺寸刚好符合8位精度但不符合14位精度,电流源阵列版图如图5所示:

图5 电流源阵列版图

该电流源阵列L=1.4 mm,W=0.8 mm,面积为1.12 mm2,比由式(4)计算得到的14位电流源阵列理论面积小了近30倍,系统性失配误差大大减小。

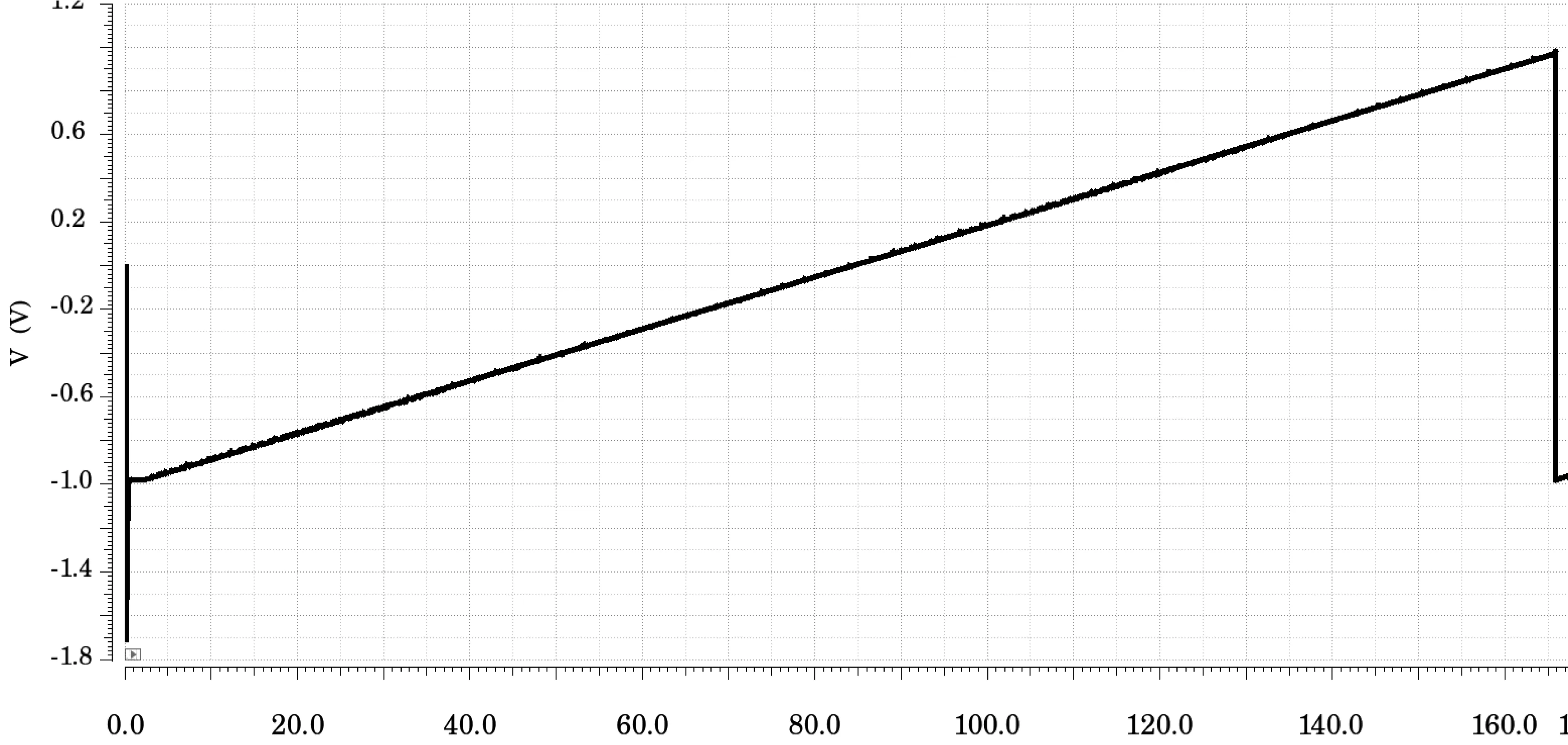

在27℃、tt工艺角下,加入失配模型,输入为遍历14′ b00000000000000到14′ b11111111111111的二进制码,共16384个,每隔10 ns跳变一次,得到的输出模拟信号如图6所示:

图6 输出模拟信号

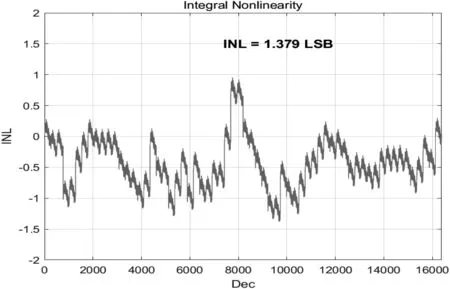

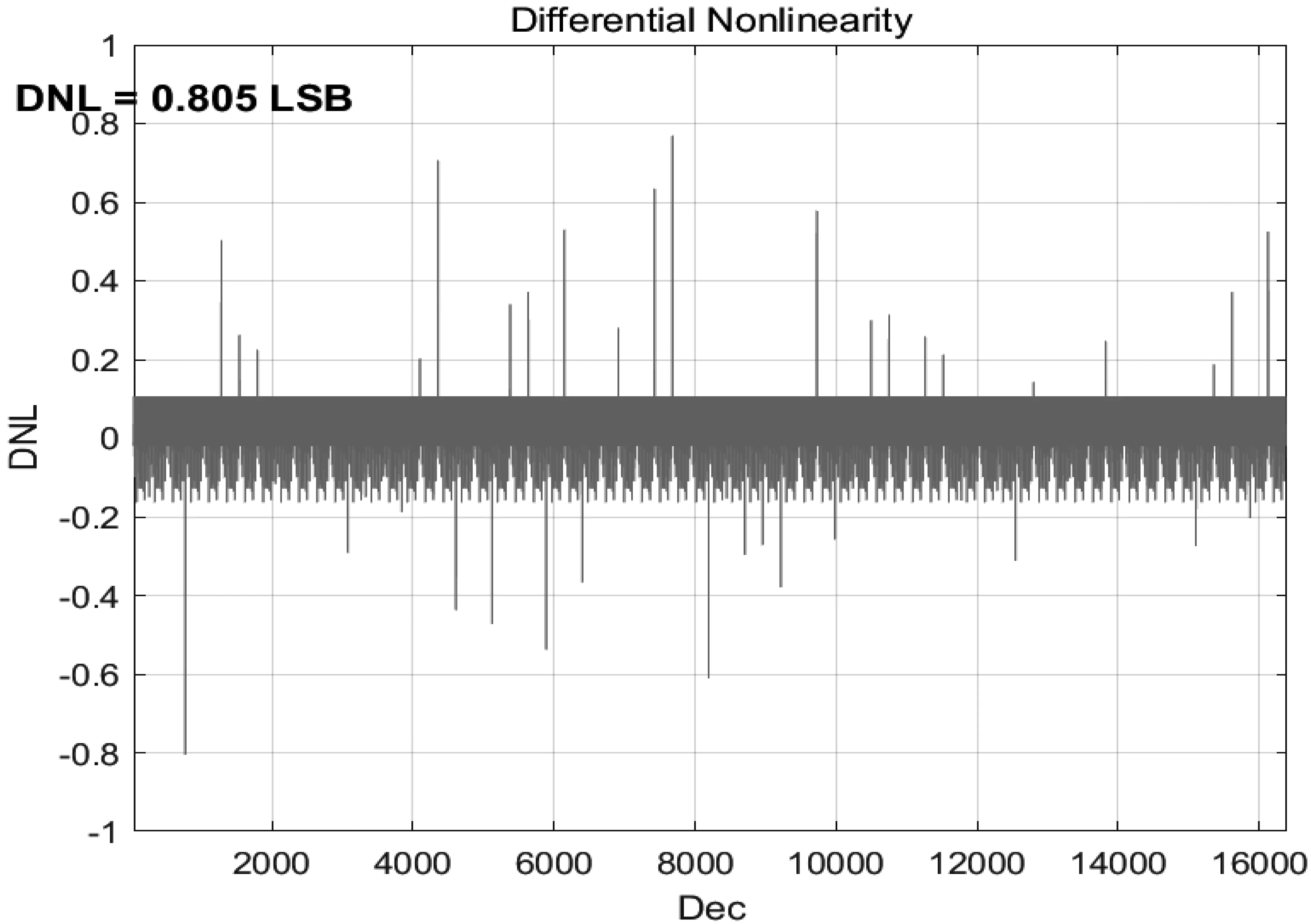

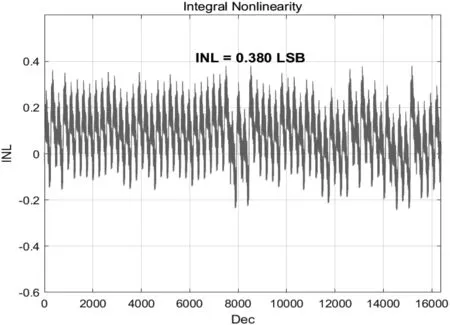

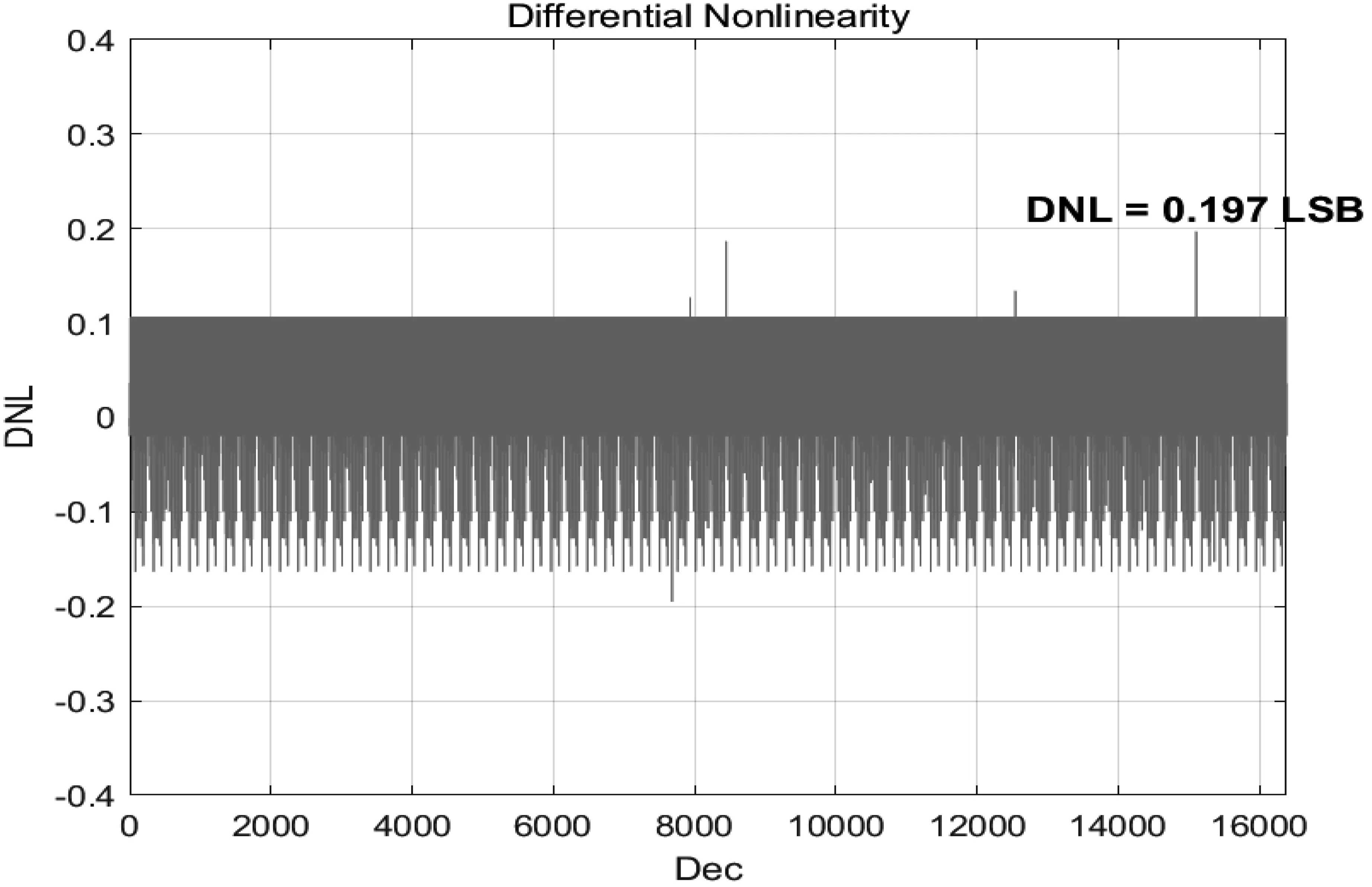

对输出波形进行采样,采样频率为100 Msps,将采样得到的16384个点导入Matlab进行处理,得到未校准DAC的静态性能,如图7和图8所示:

图7 校准前INL

图8 校准前DNL

根据本文提出的静态校准技术进行校准,给定高位64种状态对应的8位控制字控制校准DAC,输入重新遍历二进制码,采样后经Matlab处理,得到校准后的静态性能,如图9和图10所示:

图9 校准后INL

图10 校准后DNL

根据仿真结果可以看出DAC静态性能得到明显优化,该校准算法能够在减小电流源阵列面积的基础上校准随机性失配误差。

4 结语

分析了电流舵DAC的工作原理和静态误差来源,提出了一种静态校准技术,应用在一款14 bits精度、100 Msps采样率的电流舵DAC中。该校准技术不仅可以校准随机性失配误差,根据该校准技术的机理,也可以减小电流源MOS管尺寸从而减小系统性失配误差,从两方面提升了电流舵DAC的静态性能。通过后端仿真验证,证明了该数字校准算法的有效性和可行性。本文可以帮助学生了解电流舵DAC的工作机制,理解数字校准算法在设计中的重要性,将实践与教学更好地结合。