一种弹载信息处理器NAND Flash高可靠数据管理方法*

2022-07-27朱旭锋郭佳鑫胡晓晴梁建强

朱旭锋 郭佳鑫 胡晓晴 梁建强 张 红

北京航天自动控制研究所,北京 100854

0 引 言

随着导弹信息化、智能化、实战化发展,弹载信息处理器对非易失的大容量数据存储器需求变得非常迫切。NAND Flash因具有非易失、存储密度高、读写寿命长、写入和擦除速度快等特点,在弹载信息处理器被广泛应用。但NAND Flash存在天然缺陷:一是存在坏块而且坏块会随时间增加;二是存在不确定的位反转[1-2]。因此,通常需要采用坏块管理、备份、ECC校验等方法提高数据存储可靠性。文献[3]提出了一种高效的坏块管理方法,通过对坏块地址映射和替换,提高了星载NAND Flash存储器的使用寿命,但这种坏块管理方法主要适用在多片NAND Flash并行存储的星载场合,而且没有进行ECC校验,对于弹载信息处理器仅有限数量NAND Flash存储关键参数的场合并不适用。文献[4]基于FPGA方法实现了NAND Flash坏块管理,但并没有考虑数据位反转带来的可靠性问题。文献[5]采用硬件双备份和坏块管理相结合实现了NAND Flash数据存储,但仍然无法解决位反转带来的可靠性问题。文献[6]采用FPGA实现了一种基于汉明码的高性能ECC校验方法,每256Byte可实现24bit的ECC校验。但这种算法可纠正1bit错误,对于2bit及以上错误无法保证纠错和检错[7]。

本文为提高NAND Flash数据存储可靠性,在对NAND Flash芯片机理分析基础上,提出一种NAND Flash全生命周期数据管理方法:将DSP软件和FPGA算法相结合,实现了坏块管理、坏块评价、ECC实时校验,提高了NAND Flash数据存取的可靠性。

1 NAND Flash数据管理技术

1.1 NAND Flash简介

NAND Flash存储器是Flash存储器的一种。NAND结构能提供极高单元密度,是高数据存储密度理想解决方案。其存储结构为:NAND Flash数据以bit方式保存在memory cell,一个cell只能存储一个bit。这些cell以8个为单位,连成bit line,形成byte。这些byte line会再组成Page,然后每128个page形成一个Block。Block是NAND Flash中最大的操作单元,擦除按照block为单位完成,编程/读取是按照page为单位完成的。NAND Flash读写操作以页为单位。在每次写入数据之前必须进行擦除操作,擦除最小单位为块。块与块之间相互独立。坏块不会影响其他块,这正是进行坏块管理的基础。

NAND Flash芯片在使用时,应考虑两类对错误类型处理:即坏块和位反转。

1.2 目前NAND Flash数据管理方法

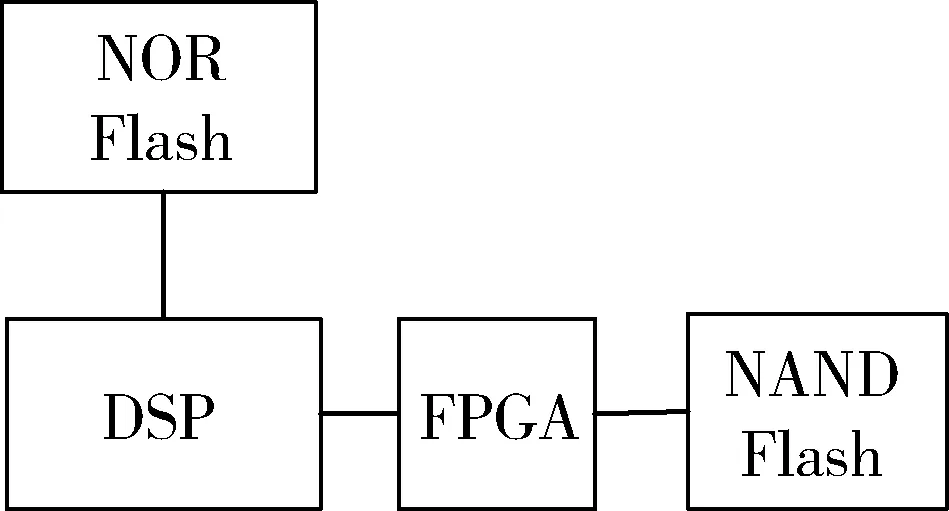

目前弹载信息处理器中,NAND Flash数据读取结构如图1所示。

图1 弹载信息处理器NAND Flash应用架构

图1中,NOR Flash存储容量较小,主要存储程序信息。NAND Flash存储容量较大,主要存储图像数据和深度学习关键参数。DSP通过FPGA访问NAND Flash数据。FPGA设计NAND Flash控制器,控制NAND Flash读写。为了实现NAND Flash数据管理,目前方法如下:

一是建立坏块表:在出厂时,将NAND Flash出厂时标定的坏块信息存储在首块首页(block0,page0)存储空间,首块存储空间厂家出厂保证不是坏块;在数据烧写时,首先读取坏块信息,按照坏块信息跳过坏块。烧写过程中,如果某block回读数据与上传数据不一致,则将该block标记为坏块,并将原本写入该block数据写入下个block,同时更新位于block0坏块信息表;

二是采用硬件或者软件方式进行数据备份。通过备份提升位反转(Bit Flip)条件下数据加载可靠性;三是通过FPGA软件进行错误检查和纠正(ECC,Error Checking and Correction)校验算法来提高数据可靠性。但传统的单bit纠错能力,不能满足嵌入式CPU和GPU对NAND Flash存储的可靠性需求。文献[8]采用了BCH码与经典硬判决的编解码算法,但编码效率低。编码延时大。数据吞吐能力无法满足航天器高速存储系统需求。文献[9]提出一种RS+LDPC码级联并行编码设计方案,但编码复杂,适用于多片NAND Flash并行处理场合。文献[10]利用BCH算法实现了对负责GPU数据交互的NAND Flash进行多bit错误纠正,其通过GPU实现了修正的校验多项式计算单元(Syndrome generator),构建了适应多种传输参数的BCH编解码架构。文献[11]提出了一种对称逐块拼接的架构,优化BCH的编码解码过程,提升算法的编解码效率。文献[12]进一步基于对称逐块拼接架构进行优化,整合主编码器和一个辅助编码器,进一步提升BCH算法的纠错能力[12]。上述文章都从优化纠错能力和执行效率的角度对BCH算法的编码和解码方式进行改进。对基于FPGA的嵌入式高可靠应用,并行BCH算法的解码单元需要消耗大量的逻辑资源。在保证算法纠错能力的基础上,需要兼顾模块资源使用情况,对消耗资源多单元模块进行压缩和优化。

本文在实现经典BCH编码和解码模块基础上,通过逻辑单元复用将无逆BM解算PE单元数量压缩为原有的1/8,将整个BCH编解码模块逻辑资源使用量压缩为传统1/2以下。

2 一种基于PE单元复用的BCH ECC校验算法

2.1 编码器设计

本文研究的BCH编解码单元,每个译码过程处理的数据内容包括4200位(4096个数据位(512字节),104个校验位),对于BCH算法码长为n=2m-1,为了实现对数据内容的包络,取m=13,纠错能力t为8位,每512字节的校验位位数为m×t=104位,每页大小为4096字节,包含8个512字节,从而需要104字节的空间来存储校验位。BCH码可描述为BCH(4200,4096,8)。NAND Flash每个数据读或写为8位字节格式,因此选择并行度为8的编码器、译码器设计。由于m=13,得到其本原多项式为:

f(x)=x13+x4+x3+1

(1)

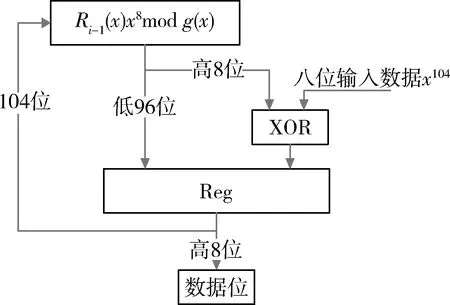

NAND Flash对外接口为8位,对于8位并行的在线数据移入,利用对应生成多项式规则的线性移位寄存器的高8位与移入8位数据乘以x104的结果相加(对于二进制伽罗华域,相加代表异或操作)。可以得到8位并行编码器的解析表达式,其硬件实现只需将表达式的每一位用同步逻辑表达。设计实现电路如图2所示:

图2 8位并行BCH编码器

在完成512次8位数据输入后,得到的104位表达式为13字节校验位数据。对于一个页来说,其数据存储区域为索引0到4095的存储字节。而4096位至4105位的10个字节存储块信息,其校验位存储在4106开头的地址空间中。

2.2 译码器设计

译码器设计包括3个模块,分别是伴随多项式计算模块、错误位置多项式计算模块、钱搜索模块。伴随多项式计算用于检测512字节的数据是否存在位反转的错误;错误位置多项式计算采用SiBM算法(Simple Inverse-free BM),用于从伴随多项式确定错误位置多项式的系数;钱搜索将错误位置多项式根的求解转化为对本原多项式根的幂的验证。

2.2.1 伴随多项式计算模块

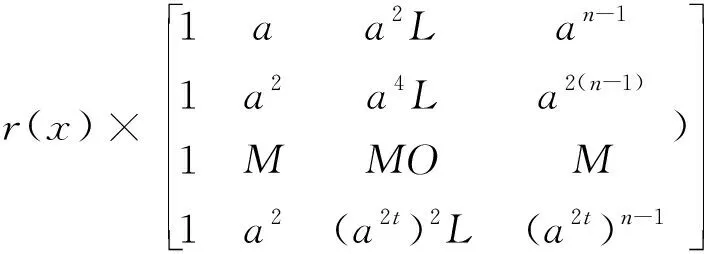

伴随多项式用于确认数据是否发生错误。对于t位纠错能力的BCH译码器,需要数量为2t个伴随多项式。

(2)

传统对单个数据位的计算,工作效率低,不能满足工程需求。对应NAND Flash数据位宽为8位,采用8位并行计算策略,如图3所示。

图3 8位并行线性移位单元

2.2.2 错误位置多项式计算模块

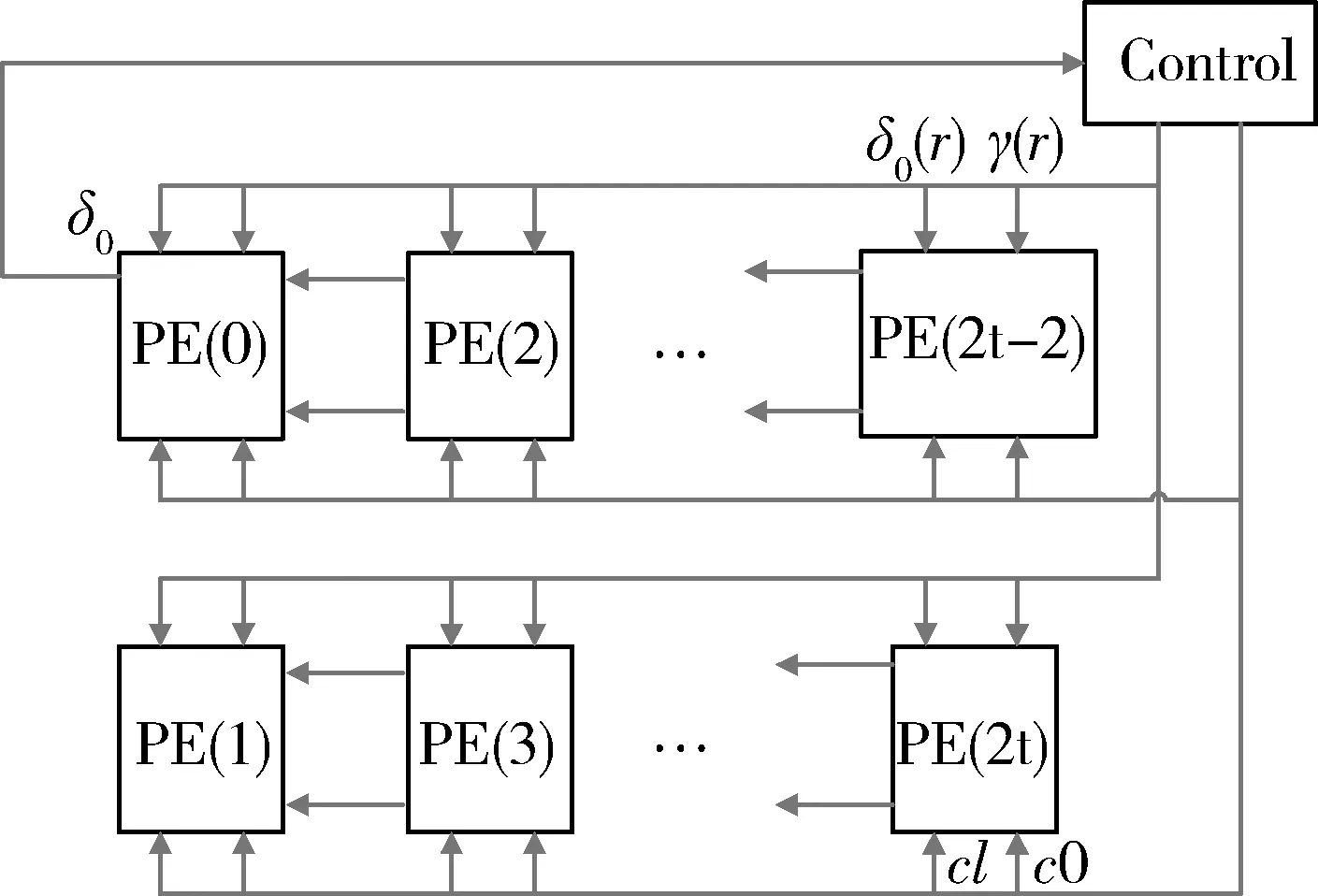

错误位置多项式计算模块是译码器设计中占用逻辑资源最多的部分。伯利坎普-梅西算法是传统的无逆BM算法,是求解错误位置多项式的解决方法之一,其实现依赖于16个PE单元的组合,如图4所示。

图4 传统无逆BM算法求解模块

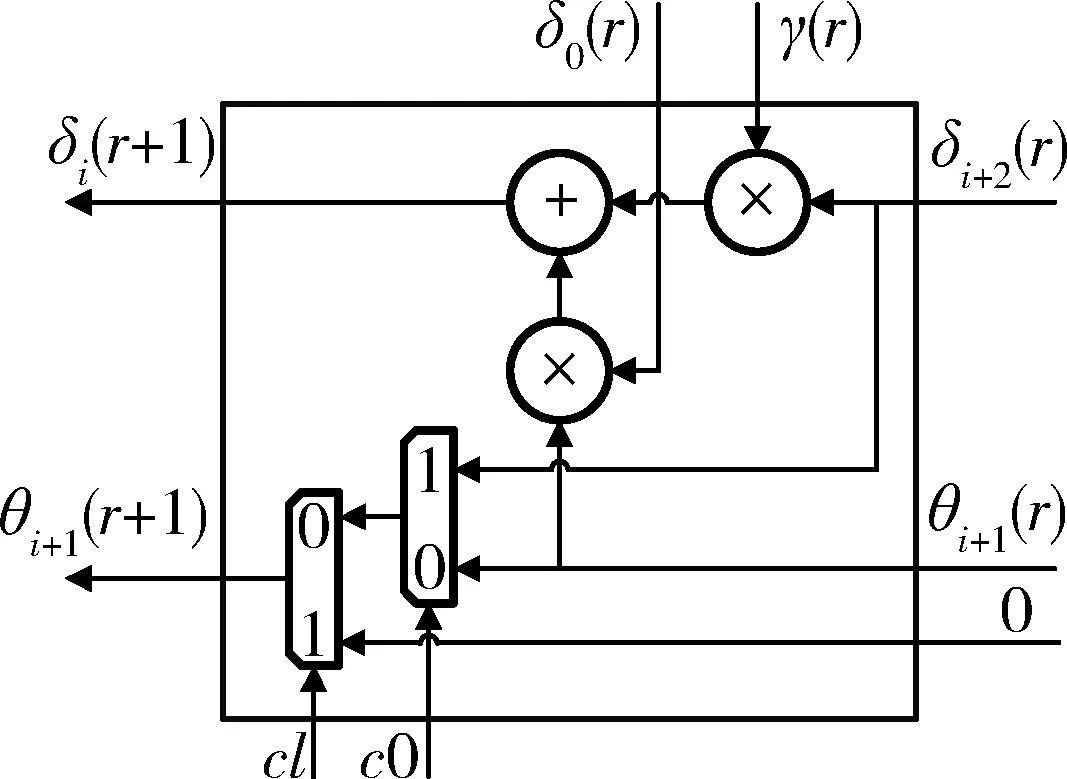

每个PE单元的组成如图5所示:

图5 PE单元设计

可以看出,传统无逆BM算法虽然实现简单,但PE资源的堆叠造成逻辑资源的极大消耗,不利于FPGA的编程实现。

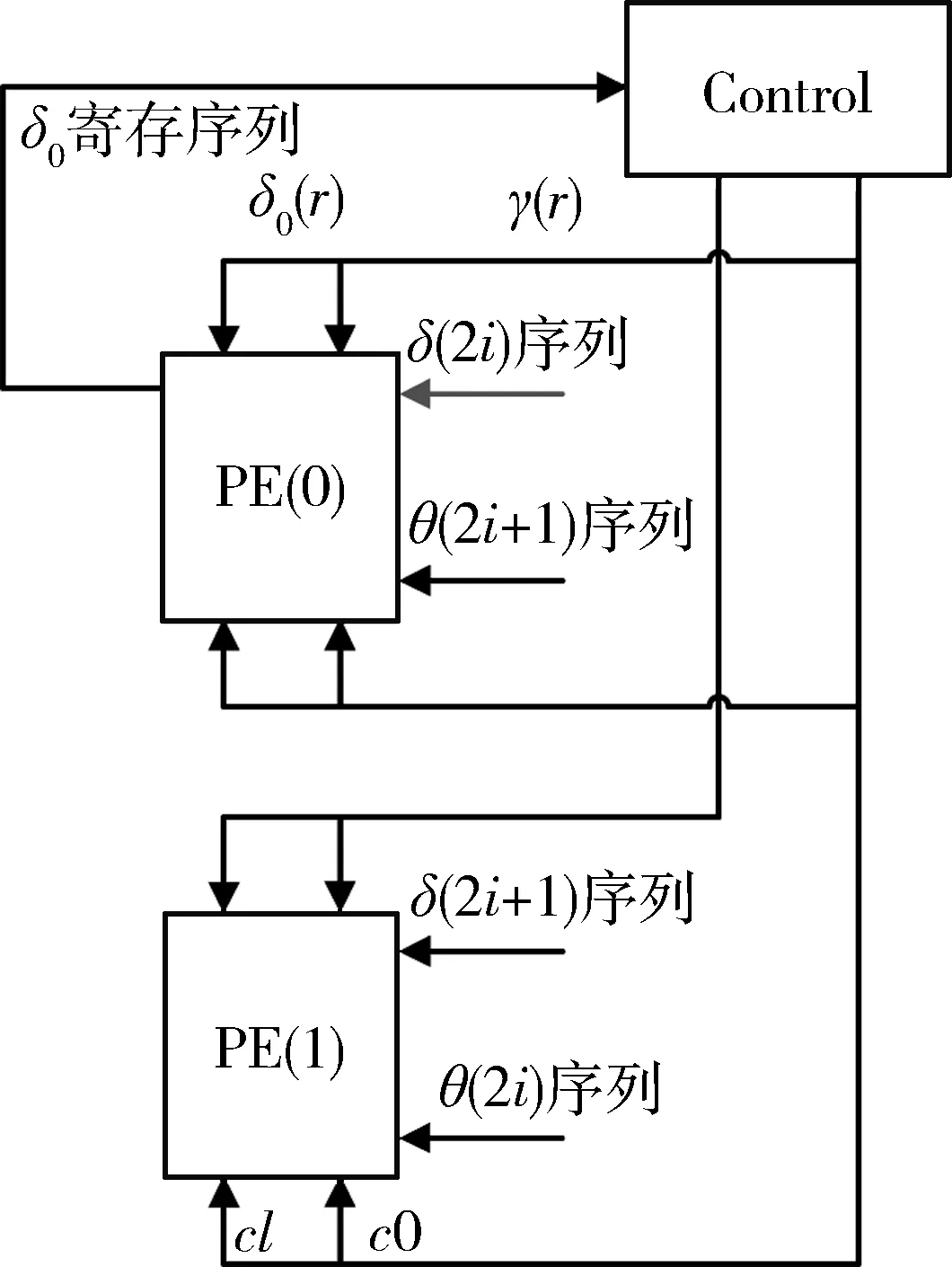

本文采用简化的无逆BM算法(SiBM)求解错误位置多项式,即采用PE单元的复用实现资源的节省,如图6所示。

图6 PE复用无逆BM算法求解模块

采用2个PE单元复用的设计方式,算法的迭代次数从t次扩展为t×t=64。钱搜索和伴随多项式计算都需要512个周期的情况下(且数据访问等待时间在于NAND Flash自身的缓存数据准备),增加的迭代次数不会显著增加数据获取的延迟。无逆BM算法模块PE单元的复用,在不显著增加访问数据延迟的情况下,将整个BCH ECC模块逻辑资源使用压缩为原来的1/2。

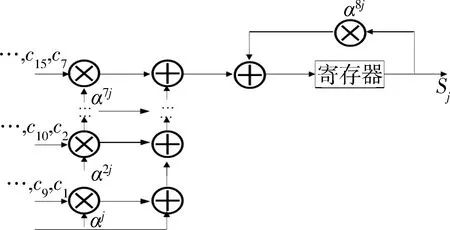

2.2.3 钱搜索模块

钱搜索是利用关键方程的错误位置多项式σ(x)确定错误位置的过程。本文的BCH(4200,4096,8)算法是一个缩短码架构,原码是(8191,8087,8),所以在使用钱搜索寻找σ1的根的过程,并不是从α0开始,对所有的幂次都进行搜索。而是从3991(8191-104-4200)开始,8位并行钱搜索的计算电路设计如图7所示。

图7 8位并行钱搜索模块

算法的运行过程为:开始的第一个时钟周期,选择器把最左边的伽罗华域乘法器的结果存入寄存器,以后每个周期选择器选择的是后面反馈过来的数据。对于第一排来说,每个固定因子乘法器计算的结果都会用到下面的加法器进行运算,从而实现八位并行的功能。一共有8个这样的处理单元,最终结果为result0-result7,如果result0-result7某个寄存器结果为00000000,代表该位对应的数值为错误多项式的根(乘法结果为0),对应的校验数据为1,否则代表该位未发生反转,对应的校验数据位为0。在第1个时钟周期选择错误位置多项式输入左侧乘法器后,模块自身持续迭代512个周期,得到512个8位校验数据。当DSP读取Flash中的数值时,利用FIFO结构,将从NAND Flash获取的512字节读取数据和算法产生的512字节校验数据进行异或,得到纠正后的数据。

3 NAND Flash数据管理方法

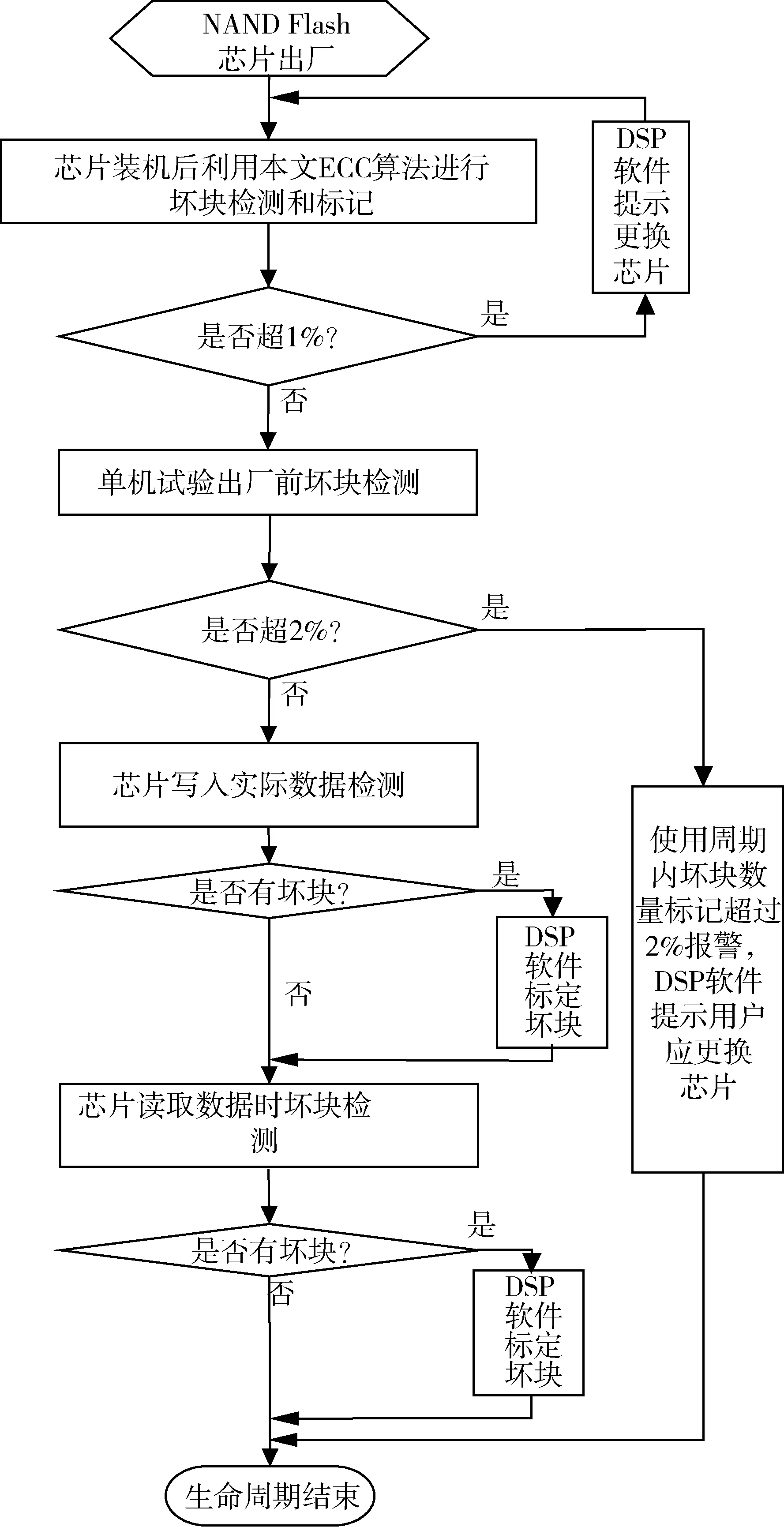

在以上ECC算法基础上,建立了一种NAND Flash的全生命周期的数据管理方法如图8所示。

图8 NAND Flash全生命周期坏块管理

NAND Flash全生命周期数据管理流程如下:

1)芯片出厂坏块检测

根据和芯片公司交流,芯片公司出厂前会对NAND Flash进行芯片擦除和写入检测:将擦除、写入失败(查询状态信息),以及超过8bit的错误块标志成坏块,存放于每个坏块第1页的空闲区位置。在完成纠错的基础上,当发生反转的位数量≤8时,反转位能够从校验数据中得到纠正。通过对比每个512字节中关键方程的非零根数量和校验数据的非零位数量,得到反转的错误位计数。当发生反转的错误位数量超过8位,出现非零根数量和校验数据的非零位数量不等的状况,FPGA对DSP上报错误。在纠错的基础上,FPGA的ECC模块能够实时监测NAND Flash读写过程中的状态,为软件的坏块管理提供更精确的依据;

2)芯片装机后初始坏块检测

NAND Flash装入弹载信息处理器后,通过对NAND Flash全部块区域的坏块标记位进行读写,完成坏块数量的检测,如果坏块数量超过1%,则说明芯片失效,需要更换新的芯片;

3)单机试验出厂前芯片坏块检测

弹载信息处理器进行一系列单机试验后,需要对NAND Flash进行坏块检测。具体方法为对芯片未标记为坏块的部分进行擦除和写入操作,失败则标记为坏块,若ECC算法检出8位以上错误,则标记为坏块;如果DSP软件判别坏块数量超过2%,则说明芯片失效,需要更换新的芯片;

4)产品写入NAND Flash数据时坏块检测

当往NAND Flash写入数据时,会进行坏块检测,对芯片未标记为坏块的部分进行擦除和写入操作,失败则标记为坏块,若ECC算法检出9位以上错误,则标记为坏块;如果坏块数量超过2%,则说明芯片失效,需要更换新的芯片;

5)产品读取NAND Flash数据时坏块检测

当从NAND Flash读出数据时,也会进行坏块检测。如果读出的数据无法纠错,则将无法纠错的块进行坏块标记。同时,此时需要对数据进行重新更新。如果坏块数量超过2%,则说明芯片失效,需要更换新的芯片。

4 仿真效验

以MICRON公司的NANDFLASH芯片(MT29F8G08ABABAWP-AITX)为例,仿真模拟NAND Flash读写过程数据。

4.1 编码器效率评估

通过采用本文改进BCH ECC校验算法后,与无ECC校验算法相比,读取时间上增加约10%,但在数据正确率上达到了100%。具体仿真方法如下:写入4096字节数据,然后写入104字节校验位。按页写入,先写入4096字节数据,然后写入104字节校验位。校验码带来的数据写入时间在总的页写入时序中占比小于10%。

4.2 数据区读取正确时校验数据仿真结果

按照本文改进的BCH算法,假设写入数据8FF,如果数据读出(fifo1_data_out)正确,为8FF,则校验数据(parity_result)为800。

4.3 数据区或校验码发生位反转仿真结果

按照本文改进的BCH算法,当按页读取数据,对于512字节,假设第一个数据8FF反转为800 (fifo1_data_out),得到的校验数据(parity_result)从800变为8FF。校验数据与读取数据异或结果为正确的数据8FF,实现了对8位反转位纠正。

由于校验码存放在每页(4096+224)字节中的224字节存储区,此存储器仍然存在发生位反转概率。仿真结果表明,在总反转位数不超过纠错能力8位的情况下,当数据、校验码分别或者同时发生位反转时,本文的BCH ECC算法都能够有效纠正位反转的数据。

4.4 本文改进BCH ECC算法资源和速度实测结果

本文提出的NANDFLASH数据管理方法已经在某弹载信息处理产品进行了实测。实测结果如下:

1)对逻辑资源进行对比,传统BCH ECC算法占用逻辑资源为6300LUT,而本文改进后的BCH ECC算法占用逻辑资源为2900LUT。说明改进的BCH算法可以有效减少逻辑资源数量;

2)对数据读取速度进行对比,如果无BCH ECC算法,25MHZ时钟下读取NANDFlash数据速度为1.4Mb/s。采用传统的BCH ECC算法数据读取速度在0.5Mb/s。在采用本文的BCH ECC算法后,读取速度为1.35Mb/s。说明采用本文的BCH ECC算法后读取速度延迟更小;

3)在某项目弹载信息处理器上,按照本文提出的NAND Flash全生命周期高可靠数据管理方法进行数据管理:以一年为测试周期,多次写入和读取NAND Flash数据,未再发生由于没有ECC校验而导致的数据读取错误问题。NAND Flash数据读取可靠性得到了有效提高。

5 结论

本文提出的一种弹载信息处理器NAND Flash全生命周期高可靠数据管理方法:以坏块管理为基础,通过DSP软件对NAND Flash全生命周期进行实时坏块检测,采用一种基于PE单元复用的BCH ECC校验算法,实现了对NAND Flash内存储数据的检9纠8实时检测。通过DSP软件坏块管理、基于FPGA的实时ECC纠错来提高数据管理的可靠性。

仿真效验结果表明,采用该方法即可实现实时ECC校验,同时能够有效避免数据错误和数据备份带来的空间浪费问题,提高了NAND Flash全生命周期数据管理的可靠性。本文的研究,对弹载信息处理场合应用NAND Flash实现高可靠数据管理具有重要实用意义。