大摆幅输出的高速线性行波驱动器*

2022-07-21任方圆闵成彧

黄 俊,任方圆,胡 欢,袁 恺,闵成彧

(联合微电子中心有限责任公司,重庆 400000)

0 引言

随着信息时代的到来,数据的吞吐量呈现出爆炸式的增加,其中70%以上的数据流量交互发生在数据中心[1-4]。光纤通信作为一种解决方案,能够利用光信号传输更多的数据,效率更高,传输速度更快,同时能耗更低,使数据中心之间的带宽传输能力得到了显著提高[5-8]。马赫-曾德尔调制器(Mach-Zehnder Modulator,MZM)作为光发射机的重要组成部分,它具有高速度和宽光谱等优点。对于行波电极的MZM,通常需要2 V 至10 V 的驱动电压以保证输出光的高消光比[9]。然而,这对行波MZM的驱动电路却提出了更高的要求。MZM 更高的传输速度迫使驱动电路采用更小节点的工艺来设计制造,工艺节点越小,器件的击穿电压也就越低,这与大摆幅驱动电压相互矛盾。P.Rita 等人采用0.13 μm SiGe:C BiCMOS工艺设计了工作速度为40 Gb/s,输出Vpp为4 V 的行波MZM 驱动器[10]。在2017 年,一种采用55 nm SiGe BiCMOS工艺的行波MZM 驱动器可以实现工作速率128 Gb/s,输出电压可达4.8 V[11]。然而,上述两种方案中都没有考虑输入信号受工艺、电压、温度和封装等因素的影响,信号强度会发生较大的变化,需要驱动器的增益可调;以及直流失调可能会导致系统不能正常工作。

为了解决上述问题,本文基于0.13 μm SiGe BiCMOS工艺设计了一种高速线性的行波MZM 驱动器。驱动器的输入级采用可变电阻和可变电容实现了可变增益的功能;输出级采用了击穿电压倍增实现大摆幅输出;在输出与输入之间采用DCOC 以消除直流失调。后仿结果表明,输出眼图质量很好,驱动器工作速率最高为100 Gb/s,差分输出Vpp约为4 V,驱动器实现了增益可调的功能,以及环路系统稳定。

1 行波MZM

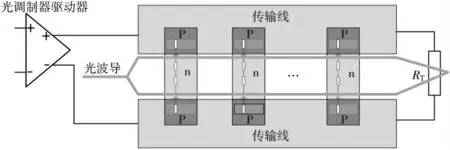

图1 所示为行波MZM 的结构示意图[12-14],主要由两个相位调制器、两个Y 分支波导和相应的驱动电极组成。其中相位调制器由周期排放的PN 结构成,波导如图中灰色实线所示,行波驱动电极由上下两根传输线构成。当驱动器的差分输出电压施加到两根传输线时,PN结的耗尽区宽度随之变化,波导中的光相位也随之改变,最终完成由电信号到光信号的转换。为了减小传输线中的信号反射,每根传输线的末端需要接一个电阻与传输线的特征阻抗完成阻抗匹配。在本文中,行波MZM的等效电模型为:终端为100 Ω 的电阻、阻抗为50 Ω 的传输线。

图1 行波MZM 结构示意图

2 行波MZM 驱动器的基本原理

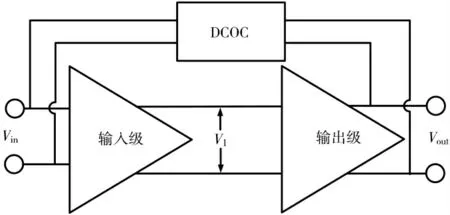

图2 所示为行波MZM 驱动器的基本结构图,主要由输入级(Pre-Driver)、输出级(Output-Driver)和直流失调消除(DCOC)构成。驱动器采用差分输入、输出可以有效地抑制电源噪声和衬底噪声,提高输出信号的共模抑制比和输出电压的输出动态范围。输入级完成与信号源的阻抗匹配以及信号的预放大。此外,输入Vin通常是幅度约为200 mV 的差分信号,但是由于输入信号受工艺、电压、温度和封装等因素的影响,信号强度会发生较大的变化,而驱动器需要一个固定的输出电压驱动光调制器。为了适应强度变化的信号,输入级的增益可调。

图2 行波MZM 驱动器的基本结构图

输出级将输入级输出的信号(V1)进行放大并驱动光调制器。这里需要指出的是,输出级需要在保证输出大摆幅电压的同时保证器件不击穿。

失调一般是由系统的不对称或者器件在加工过程中的失配引起的,比如工艺生产过程中的掺杂不均匀、刻蚀误差等。如果电路中存在较大的失调电压,那么经过多级级联后,失调电压可能因为很大的级联增益使得后级电路工作点发生偏移甚至不能正常工作,严重限制了电路的性能。因此,DCOC 加在了输出级的输出端(Vout)与输入级的输入(Vin)之间,如图2 所示。

2.1 输入级

输入级如图3 所示,为了与芯片外部实现50 Ω 阻抗匹配的同时为输入级提供合适的偏置电压,输入射随对(Q1和Q2)基极端接50 Ω 到输入电源VDD1。尾电流源在偏置电压VG1的控制下为各个支路提供合适的工作电流。输入射随之后接差分放大电路(Q3和Q4)进行高频信号峰化补偿信道损失以及实现增益可调。发射极之间的两个可变电容C1的数值由电压VC_ctrl控制,发射极与尾电流之间的晶体管M1和M2工作在深线性区,假设M1(M2)的漏源电压为VDS,则流过其电流为:

图3 输入级电路结构

其中μn为沟道的电子迁移率,Cox为单位面积的栅氧化层电容,W、L 和VTH分别为沟道宽度、长度和阈值电压。当VDS<<2(VDS-VTH),式(1)变为:

也就是说,IDS是VDS的线性函数。这种线性关系表明M1和M2可以用一个线性电阻表示,该电阻为:

这样,M1和M2就可以作为一个由栅极电压VR_ctrl控制的电阻。根据文献,C1、M1和M2构成发射极负反馈,通过控制信号VR_ctrl改变Ron,实现对输入级增益的连续控制;通过控制信号VC_ctrl控制C1的大小,实现零点可调。此外,在输出端,采用并联电感峰化技术(L1)来实现扩展带宽[15]。

2.2 输出级

为了提高调制光信号的消光比,同时为行波MZM提供合适的Vπ电压,驱动器差分输出摆幅设计为4 V,而SiGe BiCMOS 工艺提供的NPN-HBT 的击穿电压BVCEO为2.1 V,存在器件击穿的问题。通常,行波MZM驱动器在输出级使用共射共基结构来支持大摆幅,但是共基极管子的基极电压恒定,最大摆幅受限于集电极-发射极击穿电压[16]。

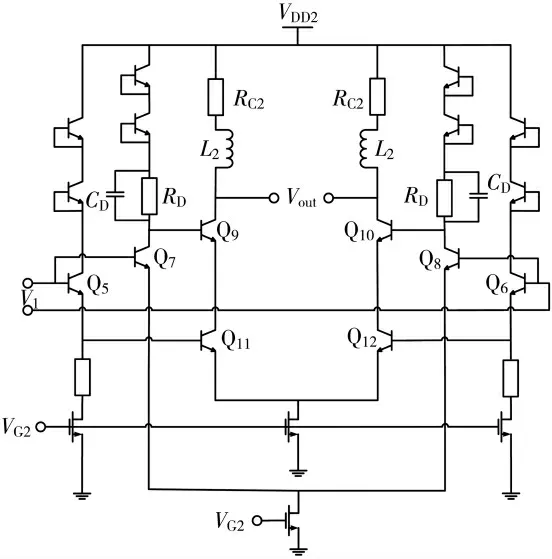

为了打破BVCEO的限制,对传统的共射共基结构进行了修改,在输出级引入主信号通道和辅助信号通道将大摆幅均匀分配在共射共基管,改进后的输出级电路如图4 所示。输出级采用的是差分输入、差分输出,其中主信号通道的信号主要经Q5、Q11和Q9到达输出节点,辅助信号通道的信号经Q7和Q9到达输出节点,其半边等效电路如图5 所示。由于信号传输路径不同,辅助路径信号到达输出节点的时间要早于主路径信号,传输时间不匹配将造成信号的失真,因此在辅助路径Q7(Q8)的集电极增加电容CD来对时间常数进行调节,以确保主路径信号和辅助路径信号到达输出节点时间接近。此外,为提高电路带宽,输出节点处的电感L2采用了并联电感峰化技术。射随级和输出级尾电流源通过偏置电压VG2来进行调节。

图4 输出级电路结构

图5 输出级的半边等效电路

2.3 DCOC

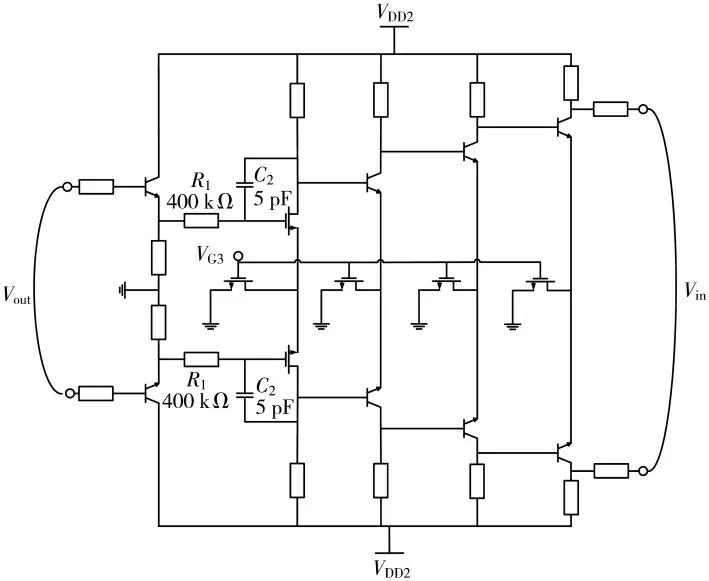

DCOC 电路结构如图6 所示,也是采用差分输入和差分输出,其中输入为输出级的输出Vout,输出端接输入级的输入端Vin。输入信号首先经过一级射随,再经过一个由R1和C2构成的低通滤波器,然后经过一级共源放大,最后再经过三级级联的共射极放大电路输出。需要指出的是,R1和C2构成的低通滤波的截止频率约为79 kHz,这可以保证DCOC 环路不会反馈高频信号,从而不会导致环路不稳定的问题。

图6 DCOC 电路结构图

3 版图与仿真结果

整体芯片版图如图7 所示,行波MZM 驱动器采用0.13 μm SiGe BiCMOS 工艺加工,该工艺提供的NPN-HBT特征频率约为300 GHz。输入级、输出级和DCOC 分别位于芯片的左上位置、右上位置和底部。芯片尺寸大小为560 μm×780 μm(包含PAD 及外围划片道)。芯 片有2个电源电压PAD(VDD1和VDD2)和5 个偏置电压PAD(VG1,VG2,VG3,VC_ctrl和VR_ctrl)。为了便于调试电路,各个电源和偏置电压独立为芯片供电和提供偏置。核心电路采用对称设计,级与级之间相对紧凑,减小寄生参数的影响。由于芯片工作电压较高,摆幅较大,信号路径应当充分考虑电流应力的影响。为了满足芯片填充率及金属、多晶密度检查,使用了大量的退耦MOS 电容。

图7 行波MZM 驱动芯片的版图

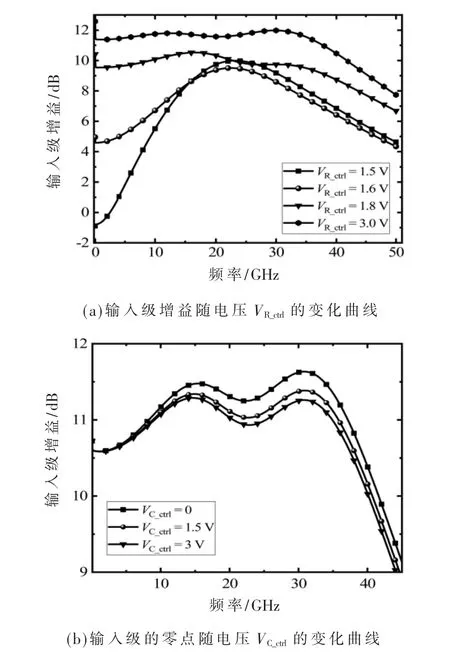

输入级增益随VR_ctrl的变化曲线如图8(a)所示,可以看出当VR_ctrl从1.5 V 增加至3 V 时,低频增益可以从-1 dB增加至11.5 dB。这是因为输入级中电压VR_ctrl通过控制M1和M2的栅极电压来控制其漏源之间的电阻,进而通过发射极负反馈来改变输入级的增益大小。因此,行波MZM 驱动器通过M1和M2实现可变增益的功能。此外,输入级的幅频特性随电压VC_ctrl的变化曲线如图8(b)所示,可以看出当VC_ctrl从0 增加至3 V 时,输入级中的零点有显著变化。这是由于VC_ctrl直接控制着C1的大小,从而通过发射极负反馈实现零点可调。

图8 输入级变化曲线

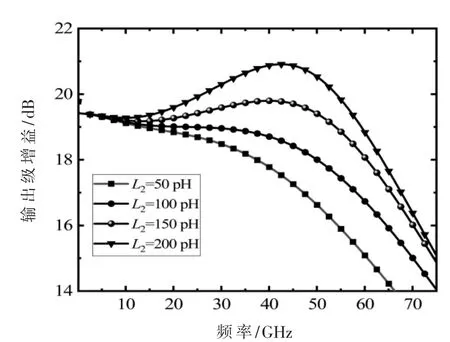

输出级增益随电感L2的变化曲线如图9 所示。由图中可知,当L2从50 pH 变化到200 pH 时,输出级在频率为42 GHz 处的峰化逐渐增强。当L2超过150 pH 后,高频处的幅频特性曲线出现了一个尖峰,这会导致在输出眼图出现过冲的现象,为此,输出级增益曲线应该尽可能平坦,所以L2设置为100 pH。

图9 输出级增益随电感L2 的变化曲线

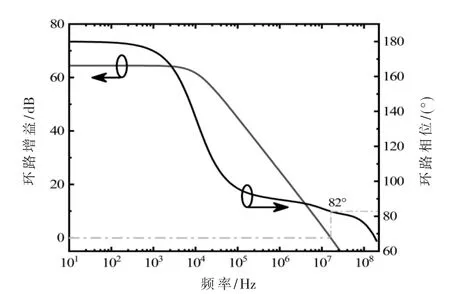

输入级、输出级和DCOC 构成一个环路,环路频域响应曲线如图10 所示。由图中可以看出,在环路增益为0 时,环路相位约为82°,也就是说,该系统有足够的相位裕度,系统稳定。这主要是因为DCOC 电路中R1和C2构成的低通滤波的截止频率约为79 kHz,这可以保证环路不会反馈高频信号。

图10 环路频域响应

当驱动电路输入端的共模电平存在差值时,这个差值也会出现在驱动电路的输出端。图11 所示为输出端的共模电平差值随输入端的共模电平差值变化曲线,可以看出当无DCOC 时,输出端的共模电平差值随输入端共模电平差值线性地增加;而当有DCOC 时,当输入差值小于12 mV 时,输出共模电平差值几乎为零,从而消除了直流失调,直到当输入差值大于12 mV 后,输出共模电平差值才开始增加。因此,DCOC 具有消除直流失调的作用。

图11 输出端的共模电平差值随输入端的共模电平差值变化曲线

驱动器的S 参数(S11和S21)随频率的变化曲线如图12所示。可以看出,当频率由0 增加至38.5 GHz 时,S11都小于-10 dB,这表明驱动器与信号源的阻抗匹配非常好,驱动器的输入端反射非常小。S21为输入到输出的传输系数,表征信号增益及带宽,S21在低频时约等于26 dB,3 dB带宽约为30 GHz。因此,S11和S21都表明驱动电路的工作频率可以非常高。

图12 行波MZM 驱动电路的S11 和S21 参数

当输入差分信号Vin的Vpp为200 mV,速率为50 Gb/s的NRZ 时,可以得到驱动电路的后仿电压输出眼图,如图13(a)所示。可以看出,输出Vpp约为4 V,jitter 时间约为1 ps,眼图质量很好。当输入差分信号Vin的Vpp为200 mV,速率为50 Gbaud 的PAM4 时,后仿电压输出眼图如图13(b)所示。可以看出,三个眼几乎一样大,眼图质量很好,工作比特率速率可达100 Gb/s。这主要是由于驱动电路的线性度高,因此可以工作在PAM4模式。

图13 后仿电压输出眼图

4 结论

本文提出了一种新型的高速线性行波MZM 驱动器,完成了电路设计和版图设计,其中芯片尺寸大小为560 μm×780 μm。仿真结果显示,本文设计的驱动器的最高工作速率为100 Gb/s,输出Vpp可达4 V,具有增益可调和消除直流失调的功能。