基于SiP 技术的某分组件及测试系统设计与实现

2022-07-21刘继祥钱宏文廖明勋

刘继祥,钱宏文,廖明勋

(中国电子科技集团公司第58 研究所,江苏 无锡 214035)

0 引言

武器装备尤其是飞弹、无人机、飞艇等微小型[1]系统平台,其电子载荷不仅要求高可靠和高性能,还要求具备轻质、高效、小尺寸的特征。作为近现代信息技术的关键核心半导体器件,应尽可能地实现轻量化、小型化、高度集成化和高可靠性,才能满足武器装备的低SWaP(Size,Weight and Power)[2]要求。

SiP 系统级封装技术[3-4]作为在系统层面延续摩尔定律的主要技术路线,得到了行业的广泛关注和应用。相比SoC 系统单芯片,SiP 封装[5]具有灵活性强、面积小、集成度高等优势。因此,SiP 封装技术不仅在工业应用、物联网、智能手机以及其他小型化智能设备中具有广阔的应用市场,在武器装备市场中,同样具有广阔的应用前景。

1 SiP 分组件原理及测试系统设计

1.1 SiP 分组件原理设计

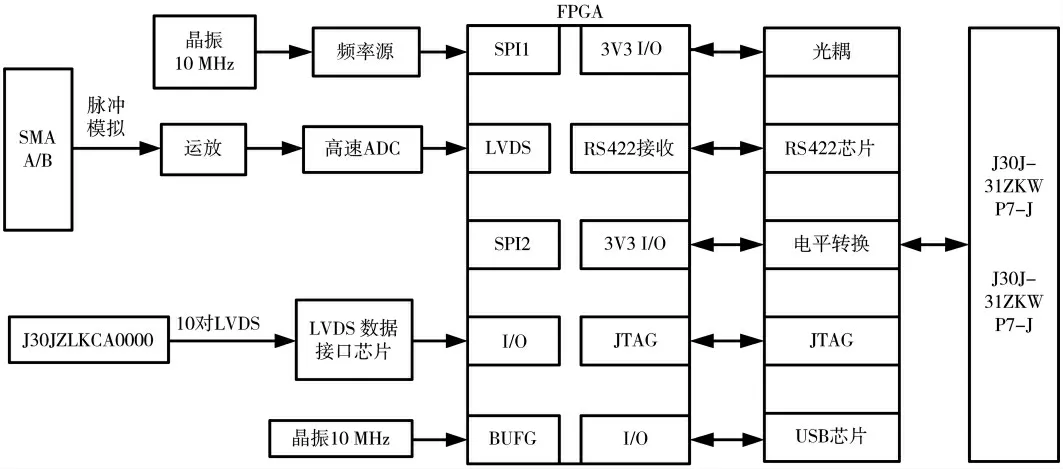

如图1 所示,SiP 分组件[6]主要由FPGA 电路、A/D采样电路、锁相环电路、电平转换电路、RS422 总线电路、离散信号采集电路及LVDS 输出电路等组成,具体包括2 路高速A/D 采集、3 路RS422 输出通道、2 路RS422 输入通道、20 路TTL 输出I/O、6 路TTL 输入I/O 口、1 路USB 接口、2 路隔离I/O 输入及10 路LVDS 输出接口。系统上电后,FPGA 首先加载程序,程序加载完成后,通过SPI 接口配置时钟芯片及ADC 芯片。ADC 进入工作状态,采集外部模拟信号并向FPGA 上传数据。之后,FPGA 对ADC 数据进行数据处理,结合外部相关输入控制信号做出相应判断,输出相关控制信号。SiP 分组件可通过RS422 接口与外部相关控制单元进行通信,例如实时上报健康状态及数据、还可通过USB 接口上传实时A/D 数据至上位机,上位机通过算法对ADC 数据进行相关分析。

图1 SiP 系统结构图

1.1.1 FPGA 电路

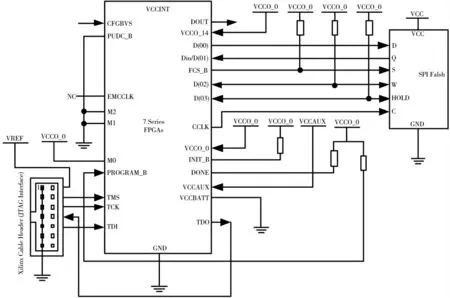

FPGA 选用国产SMQ7K325TFFG900 进行主电路设计。该芯片是基于SRAM 配置的FPGA 电路,拥有先进的高性能逻辑结构。最高工作频率625 MHz,拥有16 020 Kb BRAM、840 个DSP、500 个用户I/O,与Xilinx 公司Kintex系列XC7K325T-2FFG900I 电路兼容。具有7 种启动配置模式[7]:主串模式、从串模式、主SelectMAP 模式[8]、从SelectMAP 模式、JTAG 模式、主SPI 模式、主BPI模式,如图2所示,通过模式选择引脚M[2:0]进行模式选择。为了减少器件数量及管脚数量使用,节约布线空间,本设计将FPGA 配置为Master SPI 模式进行加载,总线宽度为4 bit,当配置时钟为50 MHz 时,配置时间最大为458 ms(91548896bit/4/50000000s)。

图2 FPGA Master SPI 配置电路示意图

SMQ7K325TFFG900 具有MultiBoot 逻辑资源,支持Fallback 启动重配置和热启动(IPROG)重配置。国产7K325T根据M[2:0]引脚值确定启动模式,进行上电加载启动,如果加载失败,FPGA 内部配置逻辑产生复位脉冲信号,FPGA 根据配置信息重新选定新的加载地址进行程序加载,即Fallback 配置。如果Fallback 配置也失败,则配置过程停止,INIT_B 和DONE 引脚都输出低电平。SMQ7-K325TFFG900 内部通过IPROG 命令进行IPROG 重配置,IPROG 命令具有和拉低PROGRAM_B 引脚相似的作用,在FPGA 配置成功后,通过设置WBSTAR 寄存器配置热启动地址,再通过FPGA 原语发送IPROG 命令,开始重配置过程。

1.1.2 高速A/D 采集电路

高速A/D 采集电路由时钟分频电路、运放电路、A/D采集电路组成。选用高速ADC 芯片SAD08D1500MQ 进行A/D 采集,该芯片为插值和折叠结合的结构,内部的电路包含折叠放大器、采样/保持放大器、LVDS 输出、时钟电路和带隙电压基准等电路。具有功耗低、采样率高、增益和失调自动校正、3 线接口控制和线性误差小等特点,如图3 所示。通过3 线接口可以对芯片内部电路的失调、增益和通道间的时钟匹配进行校正,模拟输入信号为差分输入,既可以直流耦合也可以交流耦合;时钟输入电路的内部设有直流偏置,必须使用交流耦合输入。

图3 ADC 内部功能图

1.2 测试系统设计

SiP 分组件测试系统为自动化测试[9]设备,用于SiP分组件产品的常温功能测试、性能测试以及稳定性测试,同时也可以用于产品的环境试验,生产筛选测试。

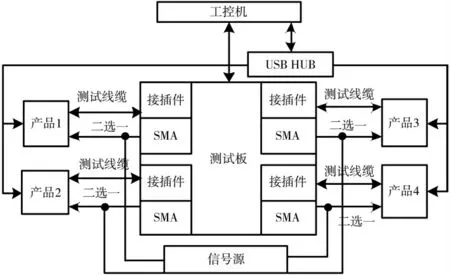

测试系统由测试盒、电源、信号源、测试盒电源适配器、显示器(选配)组成,如图4 所示。

图4 测试系统结构图

测试盒形态为小型机箱,内部集成上位机,控制器采用ZYNQ 核心板,DDS 芯片AD9910 作为信号源,ZYNQ核心板通过SPI 控制AD9910 输出,经过放大、加电压偏置输出4 路。上位机通过USB HUB 连接4 只产品的USB口及测试盒。测试盒可以同时支持4 只产品的测试,拨码开关用于板卡识别。

测试接口主要包括JTAG 接口、USB 接口、LVDS 接口、RS422 总线接口及GPIO 接口。在测试过程中,测试流程由测试设备发起,测试结果由测试设备判断,测试设备将测试结果通过RS485上传至上位机。

ADC 采集数据通过USB 上传至上位机,上位机对数据进行分析计算出SNR,4 块产品USB PID VID 由测试盒4 路上拉电阻控制GPIO 电平进行设置,产品上电后FPGA 读取GPIO 信号完成USB PID VID 信息写入。

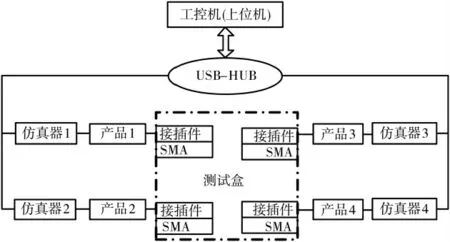

1.2.1 JTAG 接口测试

在常温下,工控机与仿真器通过USB连接至产品的JTAG 口,并烧入测试程序,以此判断该接口是否正常。

1.2.2 USB 带宽测试

通过FPGA 向上位机以最大速率传输固定大小递增数,上位机对接收数据正确性进行比对,无误后计算出USB 最大传输速率。

1.2.3 模拟输入通道测试

模拟通道测试包括两种形式:

(1)使用信号源输出标准信号,测试ADC 信噪比,通过上位机控制可编程信号源按照测试信号参数进行输出;

(2)使用测试盒上的DAC 输出不同的电平信号,测试ADC 数模转换精度及线性度测试。

1.2.4 其他接口测试

测试盒主要提供产品的输入/输出接口,检测GPIO接口,RS422 接口和LVDS 接口,电源监测及控制,并通过RS485 接口与工控机通信。其核心为Zynq7020 核心板,采用米联成熟产品,仅需开发底板,降低难度和成本。

2 测试软件设计

测试软件采用LabVIEW、Vivado-Tcl 脚本[10]、MATLAB(dll 库)[11]实现自动化测试,如图5 所示,实现了JTAG 接口检测、FPGA 代码自动下载[12]及产品功能、性能自动化测试;极高地提升测试效率,避免了每次人工手动下载FPGA[13]代码重复性、复杂性,提高了测试效率及准确性,避免人为失误,减小了工作量。

图5 某分组件测试流程图

2.1 JTAG 接口测试

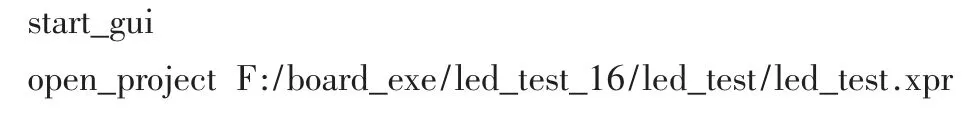

上位机通过系统命令完成cmd.bat 脚本文件调用,如图6 所示;cmd.bat 脚本文件调用Vivado-Tcl 脚本[14],实现FPGA 代码自动化烧录;Vivado-Tcl 脚本包含本项目所需功能。本项目主要完成JTAG 接口功能测试、FPGA 代码烧录,支持多产品程序依次下载,如图7 所示。

图6 LabVIEW 系统命令

图7 FPGA 程序下载示意图

cmd.bat 自动化脚本命令如下:

vivado-tcl 脚本指令如下:

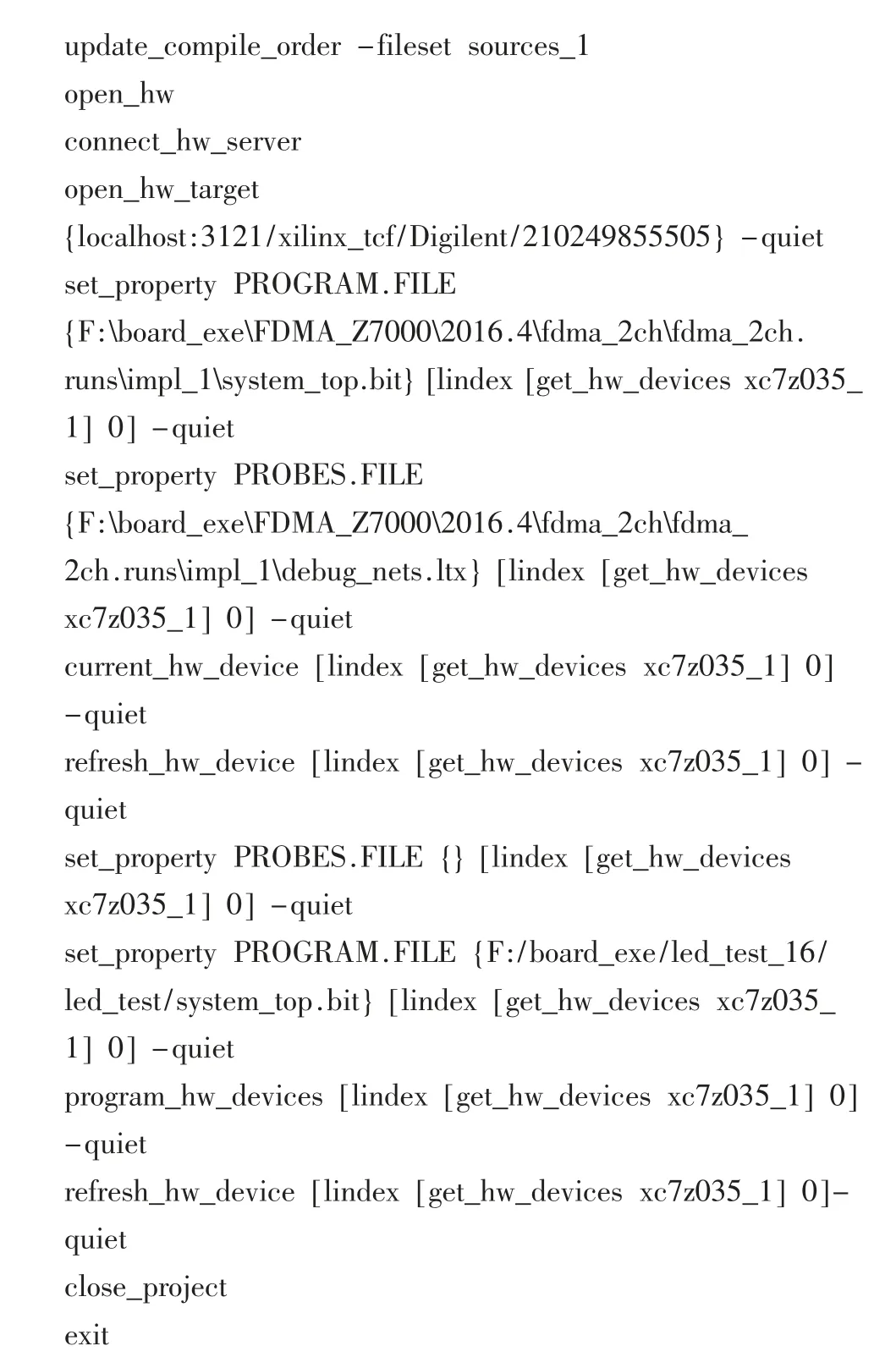

2.2 USB、串口自动识别

串口自动识别:上位机软件通过给设备管理中串口发送通信协议,若有回复命令,则认为该串口为测试盒串口,并停止检测其他串口,如图8 所示;在产品自动化测试过程中,测试盒将周期测试项测试结果实时存储于FPGA 的FIFO 中,接收到上位机测试指令后将测试结果及采集电压信息上至上位机。

图8 串口自动识别

USB 自动识别:上位机根据PID VID[15-16]完成USB号举例,通过初始化USB 状态判定产品在线情况,如图9所示。

图9 USB 自动识别

2.3 USB 速率测试

针对USB 接口速率测试[17],工控机首先通过上位机向产品发送USB 速率测试指令,产品接收到USB 速率测试指令后,FPGA 主动生成200 MB 递增数据并通过USB发送至上位机,上位机完成200 MB 数据接收、比对,结果无误后对FPGA 计时信息进行解析并显示USB 速度。

2.4 模拟输入通道测试

上位机通过USB 接收产品A/D 采集32 KB 数据,调用MATLAB(.dll)库完成ADC SNR 指标分析计算,如图10所示。

图10 LabVIEW 调用COM 组件

2.5 自动生成报表

通过对周期信号、单次信号进行测试,上位机对测试结果进行统计、汇总后依次写入测试记录模板内。

3 测试结果分析

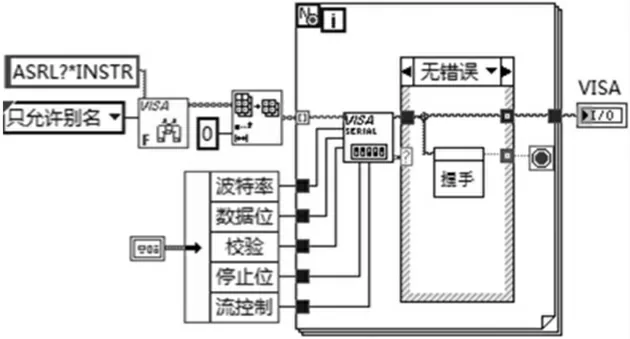

自动化测试平台能够对SiP 分组件进行快速、高效、高稳定性接口功能、性能检测,如图11 所示。同时也可以用于产品的环境试验,生产筛选测试,并根据实际需求生成测试报告,如图12 所示。

图11 某分组件测试界面

图12 某分组件测试报告

4 结论

应用SiP 技术将各个功能单板进行模块化设计后,可以有效调高系统的集成度,从而减小系统体积、质量和功耗,同时使得应用系统电路板变得更加简洁,简化了系统结构。通过设计基于SiP 技术的某分组件产品,并为此开发一套自动化测试设备,经过多次测试、反复验证,该SiP 分组件满足客户低SWaP 技术要求,测试系统能够对SiP 分组件产品接口功能、性能进行有效、快速验证。