一种数模混合无线传输收发机的设计

2022-07-21王沛佩

王沛佩

(大连海事大学,辽宁大连,116000)

0 引言

当今,无线技术飞速发展,越来越多地运用到我们的日常生活中,与有线技术相比,无线技术具有方便、灵活、减少布线、降低成本等优点。本文给出了一种通过FPGA实现了数字的键入、数字信号到模拟信号的转换,模拟信号合成的无线传输设备的设计。为了满足对20~30MHz信号调制与解调的要求,系统使用模拟乘法器AD835与20~30MHz的本振源进行调制,得到已调信号。采用与调制电路完全一致的模拟乘法器AD835与本振源进行解调,得到调制信号;为了使解调后的信号无失真还原,采用低通滤波器和高通滤波器,将合路信号分离还原。最后,再次利用FPGA进行模数转换,转换后的数字信号译码接入数码显示。

1 系统功能及其实现方案

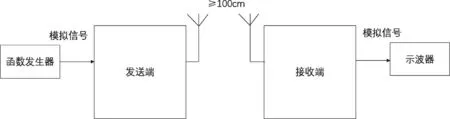

系统组成部分如图1所示。本设计是在同一信道进行数字-模拟信号混合传输的无线收发机。

图1 系统功能图

■1.1 系统功能描述

数字信号由4个0~9的一组数字构成,在发送端中通过液晶屏键入;模拟信号为语音信号,频率范围为100Hz-5kHz,通过函数发生器产生。采用无线传输的方式,载波频率范围为20~30MHz,信道带宽不大于25kHz,收发设备间最短的传输距离不小于100cm。收发机的发送端完成数字信号和模拟信号合路处理,在同一信道调制发送。收发机的接收端完成接收解调,分离出数字信号和模拟信号。接收端数字信号用数码管显示,模拟信号用示波器进行观测。

1.1.1 发射端的功能

(1)实现单路模拟信号传输。由函数发生器输入模拟信号为100Hz~5kHz的语音信号。

(2)实现单路数字信号传输。首先在液晶屏上键入4个0~9的一组数字,在发送端进行存储并显示,然后按下发送键对数字信号连续循环传输。当发送端按下停止键,结束数字信号传输,同时在发送端清除已传数字的显示,等待键入新的数字。

(3)实现数字-模拟信号的混合传输。任意键入一组数字,与模拟信号混合调制后进行传输。

(4)收发机的信道带宽不大于25kHz,载波频率范围为20~30MHz。并且收发机可在不少于3个载波频率中选择设置。

1.1.2 接收端的功能

(1)解调后的模拟信号波形无明显失真。

(2)在只有模拟信号传输时,接收端的数码显示处于熄灭状态。

(3)在只有数字信号传输时,解调出数字信号,通过4个数码管显示。开始发送到数码管显示的响应时间不大于2秒。

(4)在数模混合传输时,能正确解调数字信号和模拟信号,数字显示正确,模拟信号波形无明显失真。

■1.2 系统实现方案

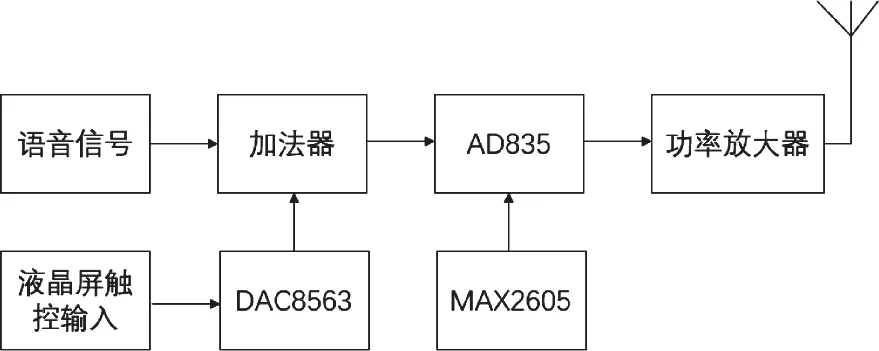

1.2.1 发射端方案实现

发射端方案如图2所示。主要包括DAC8563、加法器VCA810、AD835、AD9959、功率放大器OPA847。利用频分复用的思想,通过与FPGA板连接的液晶屏输入数字信号,经DAC8563将数字信号转为模拟信号。另一路语音信号直接通过函数发生器输入不进行频谱搬移。再将两路信号使用加法器VCA810进行合路,两路信号在各自的频段内互不干扰,独立进行数据传输。此方案方法简单,合成信号后接收端得到的解调信号无明显失真。采用线性调制的方法,将合路信号通过模拟乘法器AD835与载波频率为20~30MHz的本振源完成对合路信号的调制。该本振源通过MAX2605压控振荡器产生。由于MAX2605最低可产生45MHz的载波,所以我们将该载波信号通过单片机STM32二分频后进行输出。此方案在简单易实现的同时,能够更好的降低电路系统的功耗。

图2 发射端方案图

接收端方案如图3所示。

图3 接收端方案图

该方案主要包括:LNA、AD603、AD835、AD9959、ADS8688。将天线接收到的小信号通过20db的LNA进行放大,使用AD603实现增益可调。在解调时,采用相干解调的方法,该方案需要选用与调制载波同步的相干载波。经模拟乘法器AD835和与发送端完全相同的本振源解调后得到调制波。在两路信号分离时,采用模拟电路分离。将解调后的调制信号的频带分隔开。一路采用低通滤波器将模拟信号(语音信号)分离出来。另一路采用高通滤波器使两路信号的还原互不干扰。并且将该路模拟信号采用AD转换直接转为数字信号。将目标模拟量转为二进制离散数字量输出,并将还原出来的离散电压值显示在数码管上。该方法图像显示直观,且程控转换高速,大大降低了电路功耗。避免了混叠的情况发生,而且不用大规模采样,大大减少了工作量,也不会出现由于“数据丢失”而出现的失真问题。同时,分离出的数字电路通过液晶屏显示。直观,可触摸,相比于数码管实现功耗低。

2 系统的硬件部分

■2.1 发射端硬件设计

2.1.1 数字-模拟信号合路系统的设计

在两路信号合路处理之前,先对数字信号进行处理,通过与FPGA连接的DAC8563将离散数字量转换为模拟量。在可触摸液晶屏上输入一组四位数字,并对键入的数字进行一定次序的编码,使数字信号内部以0-1方式进行传送,形成一个方波,存入FPGA内部。再利用FPGA将采集到的数字信号通过FSK调制的方式转换为模拟信号。在二进制频移键控(FSK)中,当传送“1”码时对应于载波频率f1,传送“0”码时对应于载波频率f0,使该方波变为在高电平与低电平处频率不同的合成波形。此方式抗干扰性较高,并且经FPGA处理后所占频带较窄。在液晶屏上的操作过程为在液晶屏上键入一组由4个0~9构成的数字,进行存储并显示,通过调用FPGA内部IP核,编程实现FSK过程,生成模拟信号。

同时,为满足信道带宽不大于25kHz的要求。我们想要将信道带宽控制在该范围内,首先要计算出DA转换后的模拟信号的频率范围。函数发生器输入的模拟信号为100Hz~5kHz。为了让数字与模拟的合路信号不发生频谱的重叠并且满足带宽要求,将该模拟信号的上限控制在25-5=20kHz。我们在两个频带之间预留出大于10kHz的宽度。所以下限频率我们设定在18kHz处。与此同时,18k~20kHz这一频率范围,在将模拟信号扩展至50Hz~10kHz时,也完全可以满足带宽要求。其次,在数字-模拟信号合路部分我们信道带宽的上限已经到了25kHz。所以,我们在调制部分不能再引入另外的带宽。于是,我们选定了相干解调的方式。不改变整个频带的宽度,只对整个频带做整体搬移。最终,我们确定了将转换后的模拟信号频率设定为18kHz~20kHz范围内。

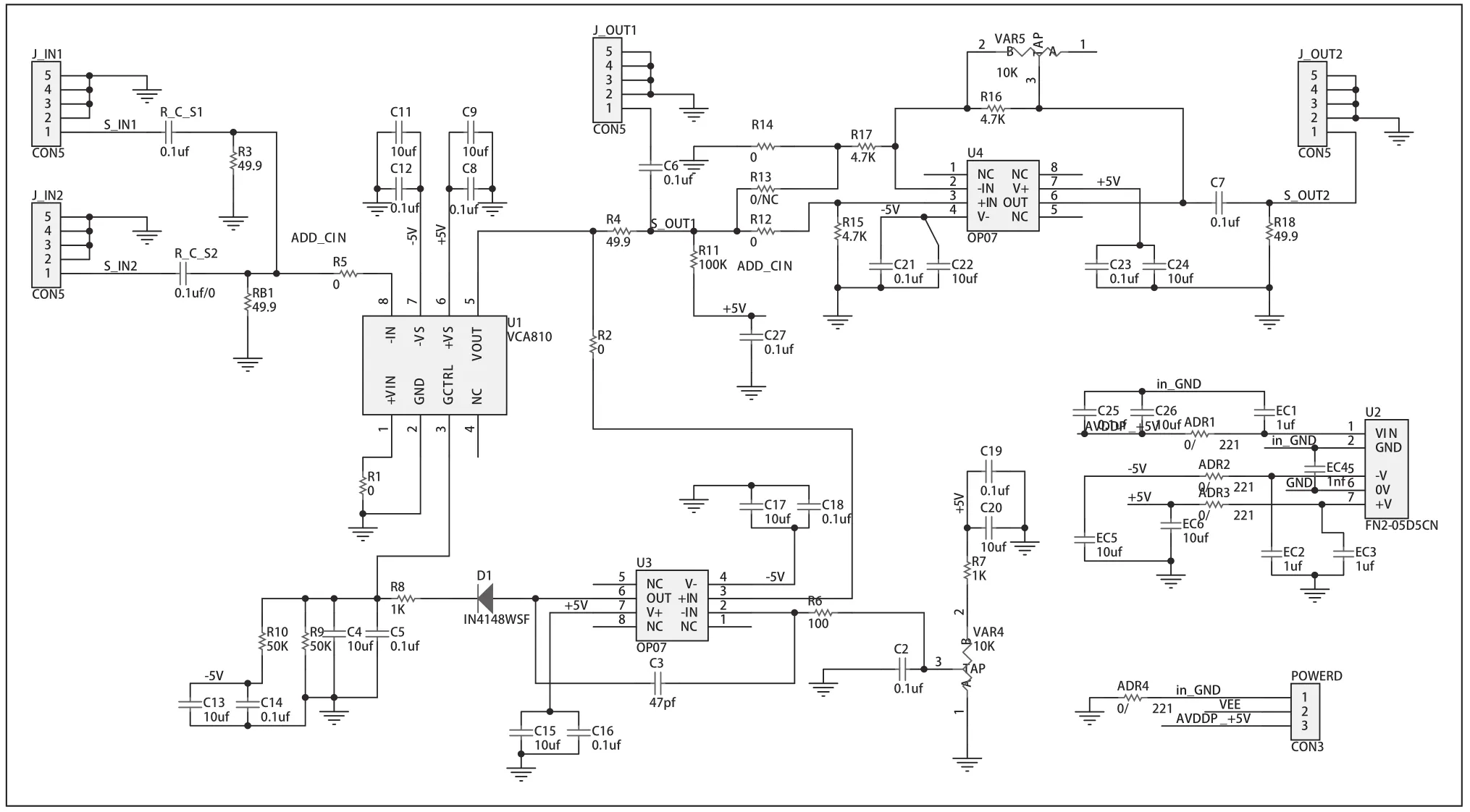

然后,将它与语音模拟信号输入加法器进行相加放大,实现频分复用。加法器内置芯片采用VCA810,它是一个具有高增益调整范围的宽带放大器,能将电压稳定在一定的范围内。基带放大器采用VCA810和OP07实现。VCA810是一个高增益调节范围,宽带,可变增益放大器。输入信号经过VCA810后,通过OP07可以进行增益反馈调节,使输出的电压稳定在一定的数值范围内。该加法器的电路原理图如图4所示。

图4 加法器电路图

由于语音信号频率范围在100~5kHz(可在适当范围内扩展),二者在频谱上互不重叠,完全可以实现。

2.1.2 调制发送系统的设计

将键盘键入的数字信号通过FSK做数字预调制,不仅完成了信号从数字到模拟的转换,而且将原始的信号先做了一次调制,将转换后的模拟信号频谱搬移到18kHz~20kHz。再对该模拟信号与语音信号进行合路处理,合成后整体再进行模拟信号的调制。

上述过程中频率范围为20~30MHz的本振信号可以通过调节FPGA振荡器外部电压来实现变化。本振源使用MAX2605实现,电路原理图如图5所示。MAX2605是集成的,高性能的中频(IF)压控振荡器,可用于便携式无线通信系统设计。

图5 MAX2605本振源电路图

将调制后的信号通过射频放大器OPA847发送出去。系统使用OPA847(单位增益带宽为3.9GHz)电压反馈运放作为中频放大器,由于前面的设计中已经包含有增益放大功能,故单级使用即可,共实现20dB的中频增益放大,满足系统要求。

■2.2 接收端硬件设计

2.2.1 接收解调系统的设计

天线接收到发送端的信号后,先让其通过一个低噪声放大器(LNA)。系统选用噪声系数NF=0.8的射频小信号放大器SBB5089作为前级放大器,其3dB频率范围50MHz~6GHz。增益为20dB,具有高带宽、低噪声的优点,能够很好地实现小信号放大。

接着通过AD603做进一步可控增益放大,AD603是一款低噪声、电压控制型放大器,用于射频(RF)和中频(IF)自动增益控制(AGC)系统。它能提供精确的引脚可选增益,90 MHz带宽时增益范围为+11 dB至+31 dB,9 MHz带宽时增益范围为+9 dB至+51 dB。用一个外部电阻便可获得任何中间增益范围。采用推荐的±5 V电源时功耗为125mW。它的优点是宽频带、增益为线性且性能稳定。

再通过一个乘法器和频率范围为20-30MHz的载波实现相干解调,乘法器电路由AD835芯片构成,电路参考芯片手册的典型电路设计,如图6所示。以X端为例,输入并接50Ω(R1||R2;或者:R1或R2焊接49.9Ω)到地,保证电路的输入阻抗为50Ω,匹配阻抗为50Ω的同轴线输入。W输出端串接51Ω(R6),一是为保证电路的输出阻抗为50Ω,匹配阻抗为50Ω的同轴线输出;二是为与电容C7构成一阶低通滤波器,实现输出信号的高频滤波。电容C7默认不焊接,可根据实际需求焊接所需电容。RW1和R5用于调整乙端的输出电压,实现W=XY+Z,Z端默认接地。

图6 AD835乘法器电路图

2.2.2 分离电路的设计

将解调后的信号通过一个fs=40kHz的低通滤波器,去掉高频干扰。再用截至频率为10kHz的低通滤波器和截至频率为40kHz的高通滤波器分别还原出两路信号,实现信号分离。其中10kHz低通滤波器通过放大器OP1177和两个二阶低通滤波器级联实现,40kHz高通滤波器则由于两信号频段本身相隔较远,因此无需再用乘法器对两信号的频带做分隔处理。

而对于两路输出信号,一路使用将,设计成一个四阶切比雪夫低通滤波器,通带在11kHz,通带衰减0.2db。另一路同样使用两个低阶滤波器级联的方式,设计成一个15kHz的三阶切比雪夫高通滤波器。然后将高通滤波后的信号经ADS8688转换为数字信号,再用数码显示输出。

图7 滤波器原理图

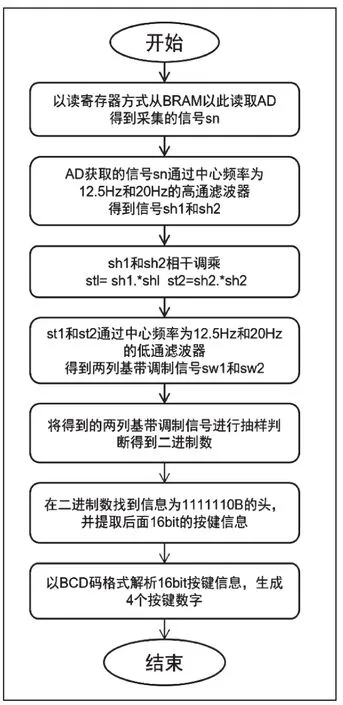

3 系统的软件部分

(1)PS端发送数据给PL端

PS端通过AXI-BRAM的通信方式将2FSK调制后的2400*16bits数据给PL端。其大致流程如下:

PS端通过AXI-LITE配置1个读AXI-BRAM的长度寄存器rd_bram_len和1个允许PL端读AXI-BRAM的rd_bram_enable寄存器,先写0再写1给PL端,PL端触发rd_bram_enable寄存器的上升沿,再循环读取rd_bram_len长度的AXI-BRAM数据,通过DAC8563输出成模拟信号。如果PS端更新4个键控数据,则重复以上流程。

(2)PL端传输数据给PS端

PL端通过AXI-BRAM的通信方式将ADC数据连续地传输给PS端。其大致流程如下:

PS端通过AXI-LITE配置1个bram_start寄存器给PL,先写0再写1表示启动ADC数据采集,之后PL端会清零AXI-BRAM数据,同时实时采集ADS8688的16bits有符号数据,ADC采样频率=100kHz,PL端先将采集的16bits ADC数据缓存到16KB的FIFO中,同时将FIFO中的数据缓存到指定的AXI-BRAM中,当AXI-BRAM写够PS端通过AXI-LITE配置的长度寄存器bram_len长度时,PL端会通过AXI-LITE输出1个AXI-BRAM写满的状态寄存器bram_wr_addr_over给PS端。PS端会定时查询该状态寄存器bram_wr_addr_over,当状态寄存器bram_wr_addr_over=bram_len-32'd4时,表示PL端已经写满AXIBRAM,之后PS端会读取AXI-BRAM内的数据进行2FSK解码(解码采用非相干解调),解调出4×4bits的键控数据,并将该值显示在4端数码管中。当PS端在读取AXI-BRAM的数据时,其实PL端还在连续地采集ADC数据,只是将ADC值缓存在FIFO中,这也是我们将FIFO开这么大的原因。

图8 FSK调制过程流程图

图9 FSK解调过程流程图

PS端每次读完AXI-BRAM中的bram_len个数据时会通过AXI-LITE重新配置1次bram_start寄存器先写0再写1给PL,PL端检测到该寄存器的上升沿表示PS端允许更新AXI-BRAM数据,PL端可以再次将ADS8688的数据缓存进AXI-BRAM,重复上述步骤,可实现连续采集ADC数据。

4 总结

整个系统经过实际测试满足了设计要求可在100Hz~10kHz的频率范围内对模拟信号进行传输,且解调后的波形无明显失真。对于数字信号,完全可以实现数字键入、显示、停止、清零的功能。系统扩展性强,载波频率的范围在20~30MHz可调,并且信道带宽满足不大于25kHz的要求。本设计突破了原有的双路模拟信号同传的限制,可实现一路模拟信号与一路数字信号的同传,应用性强。

本设计创新点:通过使用Xilinx公司生产的ZYNQ系列FPGA实现了数字信号的键入,采集,处理。数字信号通过可触摸的LED显示屏进行输入,给人更加直观的感受。对本振源MAX2605的控制也可通过FPGA实现。既可以使用压控实现,也可以通过调节滑动变阻器进而改变反馈电阻来实现。此外,本设计在模拟与混合信号电路设计方向,加入了与数字信号的混合,能更好的应用于雷达,导航,海上无线通信等方向。