一种MLS接收机中频电路的设计与实现

2022-07-12井维

井 维

一种MLS接收机中频电路的设计与实现

井 维

(中国电子科技集团公司第二十研究所,西安 710068)

介绍了MLS接收机中频电路的基本原理,结合工程应用实际,采用模拟集成电路的方法对中频电路进行了设计实现。与以往使用分立器件的设计相比,该方法的优点是集成度高、功耗低,而且提高了电路的可靠性。该设计已在实际工程MLS接收机中得到良好的应用。

MLS接收机;中频电路;频率合成器;自动增益控制

0 引言

微波着陆系统[1](Microwave Landing System,MLS)地面设备向空间定向发射经过某种角度编码的射频信号,该信号覆盖区内的MLS接收机根据地面设备发送的信号,解算出引导着陆的数据信息。MLS接收机[2]由接收前端、中频电路以及数字信号处理等相关电路组成。之前,该接收机的中频电路主要采用分离器件组成,设计复杂,器件密集,并且故障率较高。

本文设计了一种模块化、故障率低、调试简单的中频电路,中频电路进一步实现信号的下变频,信号的自动增益控制(Automatic Gain Control,AGC)放大、包络信号和相位信号的解调功能。

1 中频电路的设计

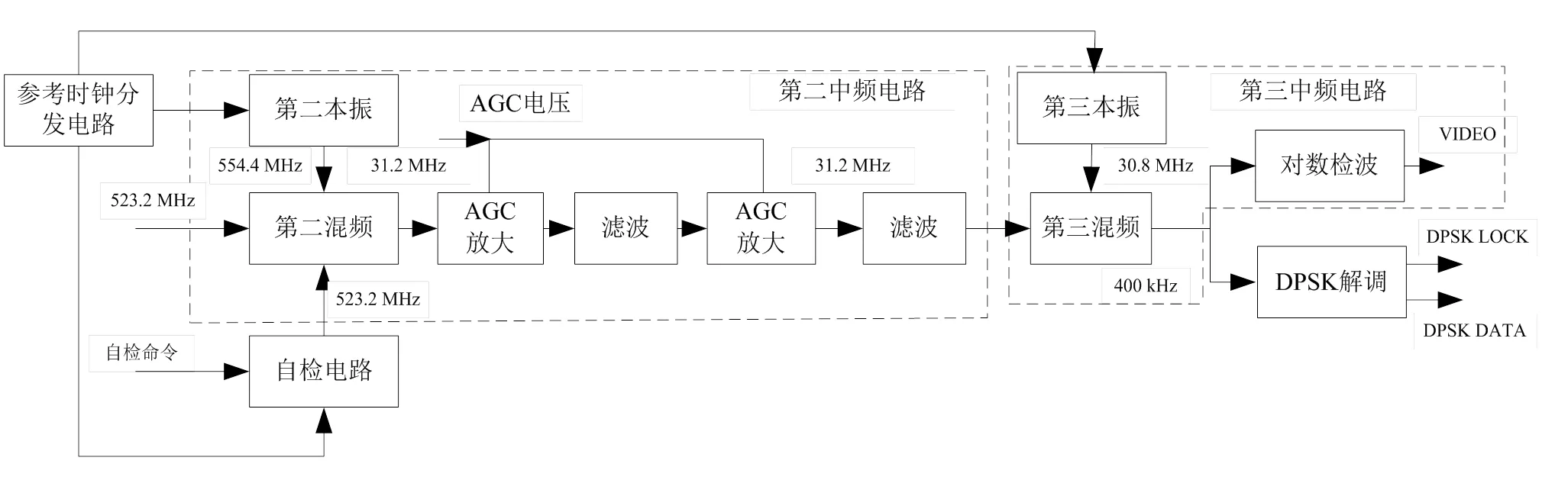

中频电路主要由第二中频电路、第三中频电路、差分相移键控(Differential Phase Shift Keying,DPSK)解调电路、自检电路、参考时钟分发电路等组成,总体设计原理框图如图1所示。

当中频电路收到自检命令时,自检电路工作输出523.2 MHz的调制信号对接收机进行自检。当没有收到自检命令时,自检电路不工作,射频前端输出523.2 MHz的信号,中频电路对该信号进行两次下变频后分为两路:一路是经对数检波后的视频包络送去进行角制导处理;另一路是经DPSK解调后送去进行前导和数据处理。

图1 中频电路原理框图

1.1 第二中频电路设计

第二中频电路工作频率为31.2 MHz,带宽为140 kHz。用554.4 MHz本振信号与523.2 MHz射频信号混频得到。由第二本振电路、第二混频电路、AGC放大电路以及滤波电路组成,完成第二次下变频、AGC放大和信道滤波功能。

混频器选用HSP12P1,该混频器是一款双平衡混频器,采用金属陶瓷封装,具有体积小、重量轻、抗干扰、可靠性高等特点。混频器HSP12P1的主要性能指标如表1所示。

表1 HSP12P1主要工作参数

综合带宽和放大倍数的考虑,选择了AD公司的AGC放大器AD8330。AD8330具有增益调整范围大、噪声低、带宽高等优点,其最显著特点是它的带宽在整个增益范围内都是固定的150 MHz。AD8330增益控制特性如图2所示。

图2 AD8330增益控制特性

第二中频电路中的AGC电路由两级AGC放大器组成。单个AD8330增益设计值为0~45 dB,两级级联实现0~90 dB增益调节范围,满足系统要求的75 dB动态范围。

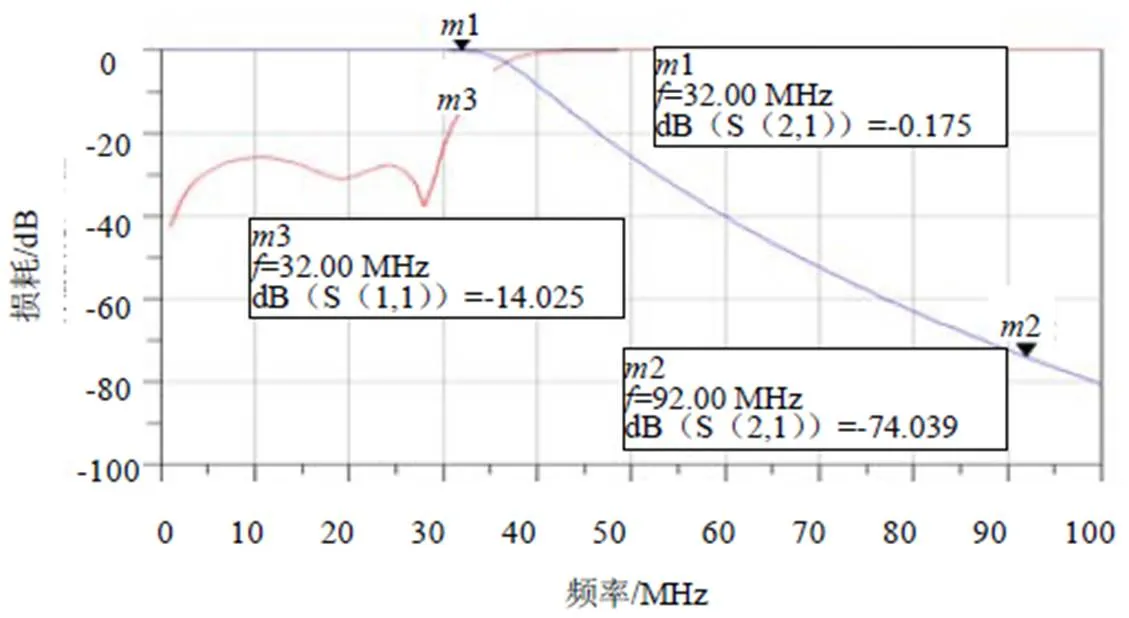

低通滤波器的作用是滤除第二次混频产生的混频杂散,以及本振泄露、中频干扰等,第一次混频产生的各种杂散频点计算后,混频杂散离通带都很远,杂散频点集中在60 MHz以上,故采用低通滤波器滤除远端杂散。仿真得到的该低通滤波器回波曲线和传输曲线如图3所示。

图3 31.2MHz低通滤波器回波曲线和传输曲线

从图3可以看出,该滤波器在60 MHz可抑制40 dB,在92 MHz以上可抑制74 dB以上,此设计满足接收杂散抑制需求。

同时,第二中频需要考虑邻道抑制、交调杂散、带外干扰以及矩行系数的要求,信道滤波器采用两级晶体滤波器实现,滤波器设计指标要求如表2所示。分析对比最终选用LST-4的31.2 MHz宽带晶体滤波器实现。

表2 晶体滤波器主要设计指标要求

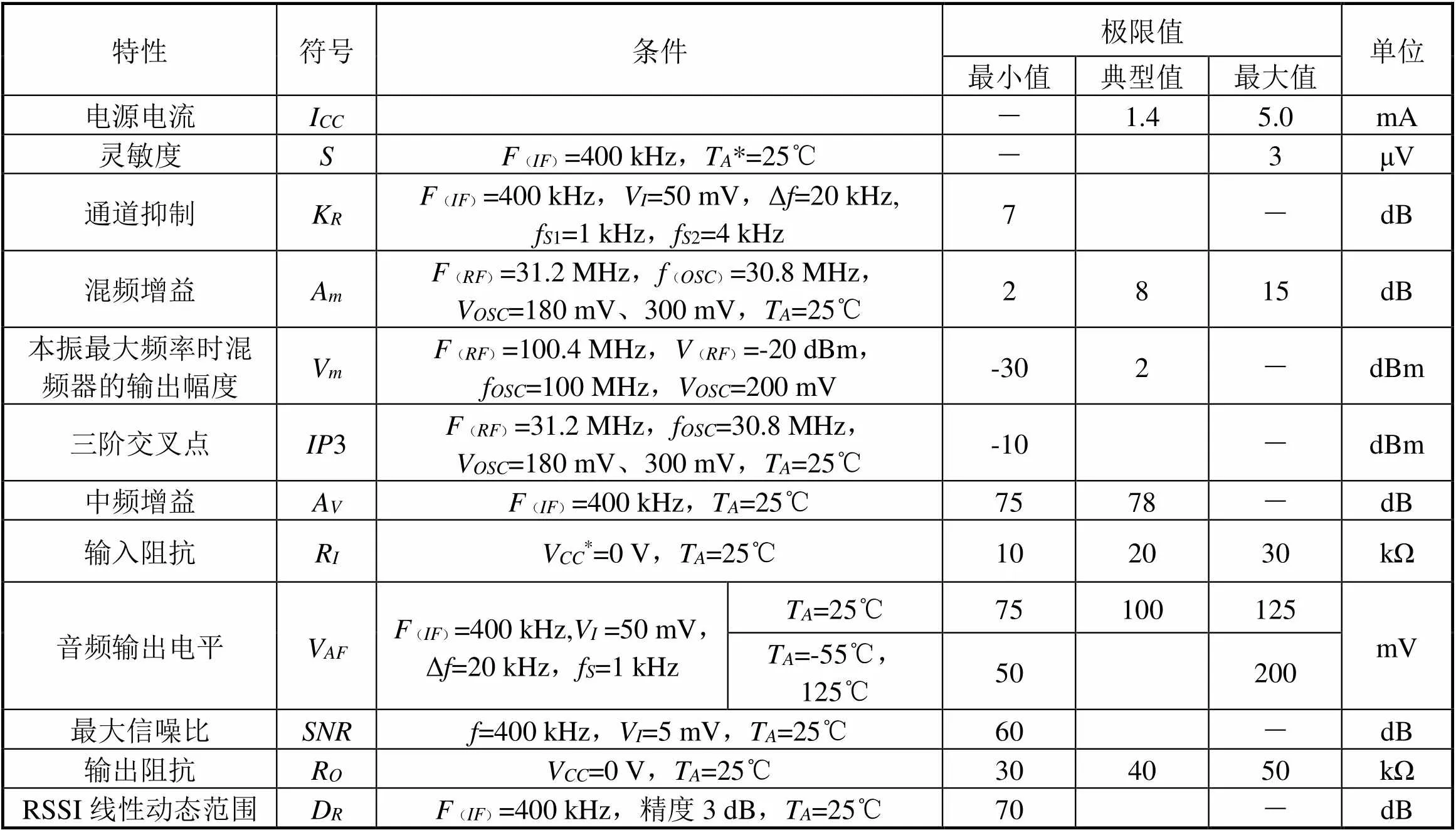

1.2 第三中频电路设计

第三中频频点为400 kHz,用频率为30.8 MHz的本振信号与频率为31.2 MHz的第二中频信号混频得到。第三中频需完成滤波、对数放大、视频信号输出功能。这里选用SB6652多功能接收器来实现,SB6652集成了本振源、混频级、中频放大级、对数放大级、鉴相器等,实现了对接收信号的混频、中频限幅放大、对数动态压缩、FM信号和AM信号解调的功能。SB6652主要技术指标如表3所示。

表3 SB6652主要技术指标

*若无其它规定,V=5 V,-55℃≤T≤125℃。空白单元格为数据不适用,一字线为数据无法获得。

该对数放大器输出为电流型输出,外接对地电阻调整输出电压幅度,并通过运放进行信号幅度调节,以满足视频输出电平为0.6~2 V的要求。

第三中频滤波器的作用是滤除第三次混频产生的混频杂散,以及本振泄露、中频干扰等,保证杂散指标。第三次混频产生的各种杂散频点计算后,第三次混频杂散在0.8 MHz以外,设计一个中心频率为400 kHz,带宽为140 kHz,对200 kHz以下频率抑制55 dB以上,对800 kHz以上频率抑制50 dB以上的带通滤波器实现。仿真得到的该滤波器回波曲线和传输曲线如图4所示。

图4 400 kHz带通滤波器回波曲线和传输曲线

1.3 本振电路的设计

本振电路采用了一种简单可行的频率合成器[3]的设计,即选择TI公司的LMX2572低功耗宽带射频合成器[4-5]提供两次变频所需的本振信号。LMX2572可生成从12.5 MHz到6.4 GHz之间的任何频率,而无需使用内部倍频器。仅需3.3 V电源供电,基底噪声为-232 dBc/Hz,可在20 μs以内实现频率的改变。

LMX2572外围电路简单,体积小,功耗低,编程的灵活性强,对电路调试要求也较低,是一款性能很好的频率综合器件,可应用于大规模批量生产。

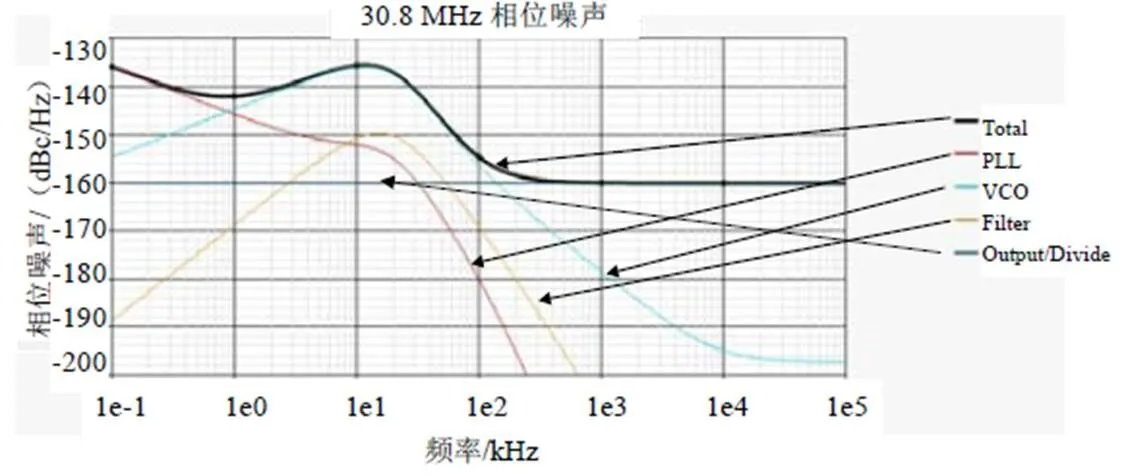

本设计中两种本振信号的硬件电路相同,通过管脚SDI、SCK和CSB进行寄存器的配置来确定LMX2572的工作状态。LMX2572本振电路原理图如图5所示,第二本振554.4 MHz的相位噪声仿真结果如图6所示,第三本振30.8 MHz的相位噪声仿真结果如图7所示。仿真结果中包括各个模块对总体输出的噪声贡献曲线以及噪声叠加后的输出信号相位噪声。

图5 LMX2572本振电路原理图

图7 第三本振相位噪声仿真结果

通过图6相位噪声仿真结果看出,输出信号相位噪声性能达到-110dBc/Hz@100Hz、-116 dBc/Hz@1kHz、-110dBc/Hz@10kHz、-130 dBc/Hz@100 kHz,满足设计指标要求。通过图7相位噪声仿真结果看出,输出信号相位噪声性能达到-135 dBc/Hz@100 Hz、-142 dBc/Hz@1 kHz、-135 dBc/Hz@10 kHz、-154 dBc/Hz@100 kHz,满足设计指标要求。

1.4 DPSK解调电路

信号经SB6652下变频和对数放大后分成两路,一路输出视频信号,一路进入硬件解调电路,解调出DPSK基带信号。

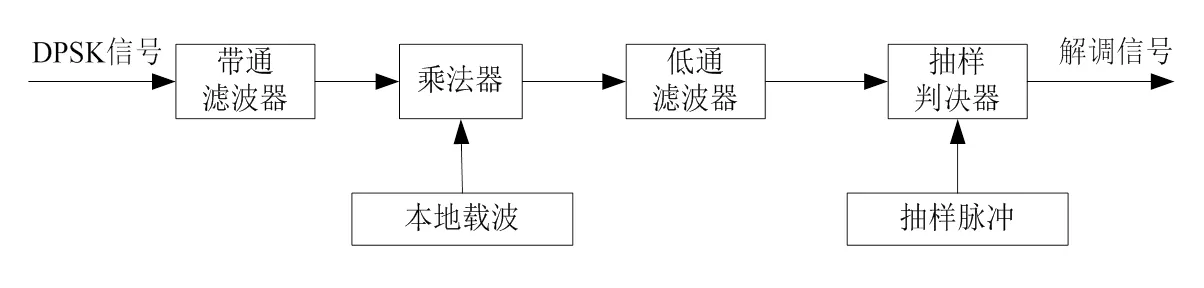

在DPSK编码中,数字信息是用前后码元已调信号的相位变化来表示的,在输入相同信噪比的情况下,虽然相干解调比非相干解调实现起来相对复杂一些,但相干解调的误码率比非相干解调的误码率要低,为了尽可能提高精度,在设计中采用相干解调方式来实现DPSK信号的解调。DPSK信号先经过带通滤波器,去除调制信号频带以外在信道中混入的噪声,再与本地载波相乘,去掉调制信号中的载波分量,再经过低通滤波器去除高频成分,得到包含基带信号的低频信号,将其送入抽样判决器中进行抽样判决得到基带信号的差分码。DPSK相干解调原理如图8所示。

图8 DPSK相干解调电路原理图

相干解调法关键在于如何得到相干本地载波。本次采用高速锁相环54HC4046和双D触发器54HC74来提取400 kHz载波。将提取出的400 kHz载波与输入的400 kHz已调制信号相乘抵消载波。抵消载波后的信号与同步脉冲信号通过低通滤波器后进入比较器,进行抽样判决,得到基带信号的差分码。

1.5 自检电路的设计

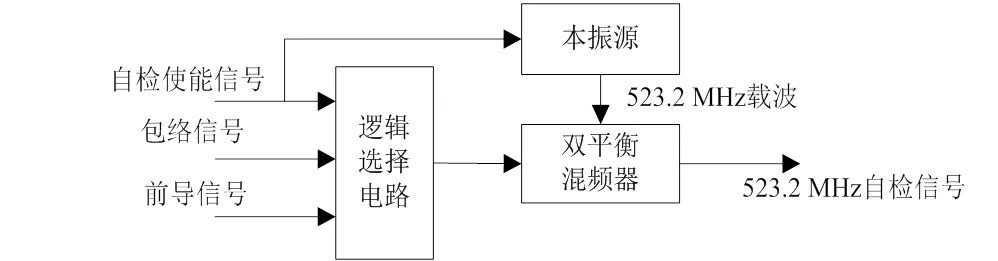

自检电路的工作原理是通过信号处理电路模拟MLS信号格式产生一个自检信号序列,这个信号序列控制中频电路内的自检电路产生出自检信号,自检信号可以快速检测接收机的性能和各种处理功能。当信号处理电路的自检使能信号为高电平时,该自检电路工作输出523.2 MHz自检信号。自检电路由双平衡混频器、本振源和逻辑选择电路组成。自检电路原理图见图9所示。

图9 自检电路原理框图

本振源依然采用锁相环LMX2572产生 523.2 MHz的载波信号,利用双平衡混频器HSP12P1的调相功能,将包络信号和前导信号进行调制,从而产生载频为523.2 MHz的自检信号。

1.6 参考时钟分发电路

选用国产低功耗的温补晶体振荡器STX013E100MCSH,晶振频率为100 MHz,直接通过功分器,给三个本振源和自检电路提供参考时钟,原理框图如图10所示。

图10 参考时钟分发电路原理框图

2 实际应用结果

该中频电路已在某飞机微波着陆接收机中实际应用,整机指标满足以下系统指标要求:

1)灵敏度:-100 dBm;

2)动态范围:≥75 dB;

3)邻道抑制:≥75 dB;

4)精度:方位≤±0.017°,方位≤±0.015°;仰角≤±0.017°,仰角≤±0.010°。

从而验证了该设计在实际应用的正确性。

3 结论

采用新方法设计的中频电路具有集成度高、功耗低、可靠性高、调试要求较低的特点,实现了MLS接收机中频信号的下变频、滤波、视频检波以及解调等功能,经过实验验证,整机功能、性能满足技术要求。

[1] 周其焕,魏雄志,崔红跃. 微波着陆系统[M]. 北京:国防工业出版社,1992.

[2] L.K.Regenbogen. Design & Implementation of MLS Data Demodulation and Processing Unit[M]. 1996.

[3] 张厥盛,郑继禹,万心平. 锁相技术[M]. 西安:西安电子科技大学出版社,2003.

[4] 郑澍鹏. 宽频段低功耗快速频率合成器的设计[J]. 电子世界,2019(20):122-124.

[5] 黄志伟. 锁相环与频率合成器电路设计[M]. 西安:西安电子科技大学出版社,2008.

Design and Implementation of MLS Receiver IF

JING Wei

The basic principle of intermediate frequency circuit of MLS receiver is introduced, and the intermediate frequency circuit by using the method of analog intergrated circuit combined with the engineering application practice is designed and implemented. Compared with the previous design of discrete devices, this method has the advantages of high intergration, low power consumption, and improves the reliability of the circuit. The design has been well applied in practical engineering MLS receiver.

MLS Receiver; IF; Frequency Synthesis; Automatic Gain Control

TN858

A

1674-7976-(2022)-03-202-06

2022-03-02。

井维(1983.10—),陕西大荔人,工程师,主要研究方向为电路与信号处理技术。