RISC-V处理器芯片的电源网络设计

2022-07-11李溢祺王仁平

李溢祺,王仁平

(福州大学 物理与信息工程学院,福建 福州 350108)

近年来,随着芯片制造和半导体产业的发展,芯片的集成度越来越高。不断增大的集成度带来了欧姆电压降(ohmic potential drop,IR drop)、电迁移(electromigration effect,EM)以及热载流子效应(hot carrier effect,HEC)等一系列问题[1]。电压降是芯片内部电源线不断变细,电阻变大,消耗在电源线上的电压变大产生的现象。电迁移是由于芯片内部金属连接线不断变细导致金属线能承受的电流密度上限变小,引起的金属离子迁移的现象。这些现象在80 nm以下的芯片制程中越来越不可忽视[2]。

设计一个合理的电源网络结构可以很好地解决上述问题。在芯片的电源网络设计领域,国内外学者都进行了相应的研究。

在学术上,国外主要提出了:基于网络划分的层次分析方法、基于预优共轭梯度的分析方法、基于类多网格技术的分析方法等;国内这方面研究起步较晚,主要集中于对层次分析法和类多网格法等技术的改进。这些研究都是专注于电源网络压降计算的计算速度和精度方面的提升[3]。

在工程上,国内外的研究主要集中于工程实践和设计分析流程上的优化。一般是通过EDA工具抽取电源网络的寄生参数,建立模型进行分析、计算和验证,并以此评估所设计的电源网络是否合理[4]。这些研究主要专注于保证设计的可靠性。工程设计的周期长短和可靠性很大程度取决于设计者的设计经验。由于集成电路的规模越来越庞大,EDA工具分析电源网络所需的时间不断增加[5],每一次重新设计和分析验证都要花费很大的时间成本,采用一套合理可靠的电源网络设计方法成为了大多数设计者的选择。

本文的芯片采用的是RISC-V指令集架构,可以支持二维码识别等功能。本文从工程的角度入手,主要通过该芯片的版图设计来解决电源网络设计常遇到的问题,以及如何在设计阶段就考虑电压降以及电迁移因素的影响,减少电源网络设计过程中的迭代,缩短芯片整体的设计周期。

1 RISC-V芯片电源网络的设计

电源网络通常由电源IO、电源环、电源网格和电源轨道四个部分组成。电源IO的数量决定外部提供的总电流的大小,电源环和电源网格的设计影响芯片内部电压降的大小,电源轨道为标准单元提供正常工作所需的电压[6]。电源轨道的参数一般是厂家预先定义好的,不需要特别的设计,所以本文的电源网络设计主要包括电源IO数目的确定和电源环、电源网格的设计两个部分。本设计所使用的逻辑综合和布局布线(place and routing,P&R)工具是synopsys公司的Design Compile和IC Compile。经过逻辑综合后,本设计包含的物理单元数量为:标准单元数20 656个,电源IO 28个,用于存取数据的4K*32位的ram模块2个。

本设计采用的工艺库是中芯国际(semiconductor manufacturing international corporation,SMIC)的55 nm的工艺库,该工艺库适用的电压范围为1.08~1.32 V,温度范围为-40~125 ℃,可选的金属层数为6~10层,本设计采用6层金属的设计方案。

1.1 电源IO数目的确定

电源IO是专门用于给芯片供电的特殊电源IO。每个电源IO能提供的电流大小是有限的,取决于采用的工艺、电压以及温度等因素[7]。只有设置足够数目的电源IO才能保证芯片的正常运行。计算电源IO数目见公式(1):

(1)

式中,Ptotal、Itotal以及Vcore分别表示芯片内核的消耗的总功耗,mW、正常工作时所需的工作电流,mA,以及电压,V;n表示电源IO的数目,个;I1.2 V表示一个供电电压为1.2 V电源IO可以提供的最小电流的大小,mA。通过上式,我们就可以计算出所需的电源IO数目。

用式(1)计算,必须先估算出芯片内核消耗的总功耗Ptotal。本设计中,该功耗主要由两个部分的单元产生,一是标准单元的总功耗Pstd,二是所使用的2个RAM的总功耗Pram。

(1)计算标准单元的总功耗Pstd

首先,估算出设计的等效总门数m。可以通过以下公式得出:

(2)

式中,Stotal表示设计中时序和组合逻辑单元的总面积,μm2;Snand表示最小型号的二输入与非门的面积,μm2。

根据逻辑综合的结果,可以得到Stotal为280 326 μm2。通过查看逻辑库.lib文件可以得到Snand为1.12 μm2,计算可得总门数m为250 292门。

其次,根据等效门数m计算出标准单元总功耗Pstd。通过查看厂家提供的数据手册,可以得到二输入与非门在Typical条件下的基本功耗Pnand约为0.016 8 μW。将其与式(2)算出的等效门数m相乘可以得到标准单元的总功耗Pstd为4.205 mW。

(2)计算RAM的总功耗Pram

首先,通过厂家提供的计算功耗的相关文件中得出RAM上的总电流IRAM。根据文件说明,得到以下公式:

IRAM=IACFram+IDC

(3)

式中,IAC代表动态电流,μA/MHz;IDC表示静态电流,μA;这两个参数可以由表1得到。Fram表示RAM的时钟频率,本设计为40 MHz。

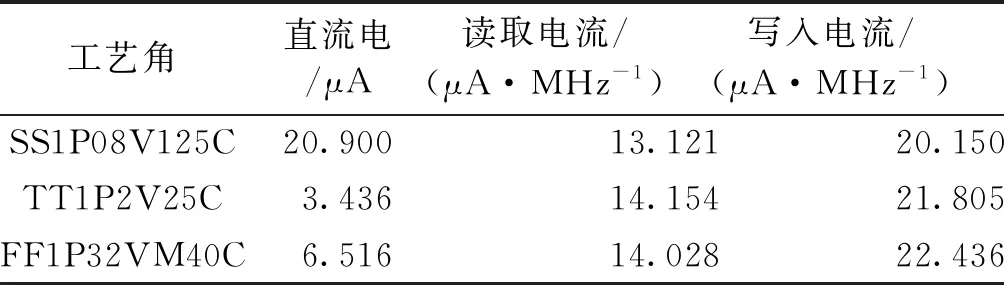

表1 RAM静态与动态电流参数Tab.1 Static and dynamic current parameters of RAM

根据表1的参数,取典型状态(TT1P2V25C)下的电流大小估算其总电流,通过前仿的波形可以得到RAM读和写的状态占比大约为80%和20%,可算出其动态电流值为627.36 μA/MHz。再按式(3)计算其总电流IRAM,得到结果为630.804 μA。

其次,可以根据功率公式计算出Pram。具体做法就是将工作电压乘上总电流。RAM的工作电压为1.2 V,所以可得单片RAM的功耗约为757 μW,设计中的两片RAM的总功耗Pram为1.513 mW。

通过上面的计算,得到了芯片内核消耗的总功耗Ptotal为5.718 mW。由式(1)可得,总电流Itotal为4.765 mA。通过厂家提供的数据手册,可以得到供电电压1.2 V的电源IO可提供的最小电流I1.2 V为40 mA,所以仅需要一对电源IO就可以提供芯片正常工作所需要的电流。查看数据手册可以得到单个电源IO的功耗约为0.036 45 mW,所以所有电源IO消耗的总功耗Ppad为1.020 6 mW。

1.2 电源环和电源网格的设计

要使芯片正常工作,除了电源IO外,还得有合理的内部电源网络设计,保证其能连接到每个器件的电源地引脚,让各个器件都能正常工作。内部电源网络主要由电源环和电源网格两个部分组成。在设计的过程中应该充分考虑各个部分流过的电流大小,设置合适的电源环宽度、电源网格的线宽以及间距,使其不超过最大电流密度限制,防止电源线熔断以及电迁移现象的产生[8]。

1.2.1电源环设计

电源环是包围在芯片内核外以及一些宏单元周围的环形供电金属,它的目的是使得供电分布均匀,同时它也是连接电源IO与标准单元的桥梁[9]。电源环的设计主要考虑3个参数,分别是:电源环的宽度Wring、电源环的间距Dring以及电源环的对数N。其中,电源环对数N可以由设计者综合工艺库要求和设计实际情况取值。

(1)电源环的宽度计算Wring

Wring可以由式(4)得出:

(4)

式中,IP为芯片峰值电流,mA;CD为厂家工艺库要求的电流密度上限,mA/μm2;N是电源环对数;k为调整因子,与工艺和供电单元数目有关。

首先,计算峰值电流IP的值。通过synopsys的功耗分析工具PTPX可以得出芯片的峰值功耗为1.795 7 W,从而可以得到芯片峰值电流大小约为1 495.83 mA。

其次,查看电流密度CD上限和调整因子k的大小。电流密度上限可在技术文件中查看,本设计电源环设置在金属5和6层,取第5,第6层金属中的较小的值,即第5层金属的电流密度,大小为39.9 mA/μm2。调整因子k的值通过查找数据手册得到,为0.75。

再次,确定电源环对数N的值。N一般是由工艺文件中要求的每层金属最大宽度确定的,本设计中取N的值为1。

最后,根据以上数据,算出Wring的大小约为7 μm。考虑到估算的偏差以及EM的影响,实际的宽度应该再增大50%左右,本设计中将其设置为10 μm。

(2)电源环间距Dring

电源环的间距Dring可以根据厂家所给的设计规则中的最小间距决定,一般情况下为最小间距的2倍左右,本设计为0.1 μm。

1.2.2电源网络设计

电源网络的另一个设计关键点是电源网格的设计。电源网格由横向和纵向的电源条交叉构成,可以为标准单元的电源轨道供电,能够防止芯片内部的电压降过大。电源网格的设计就是电源条的设计,主要考虑2个参数,分别是:电源条的间距Dstrap和电源条的宽度Wstrap。

(1)计算电源条的间距Dstrap

首先,要算出芯片内核单位面积上的功耗Punit,公式如下:

(5)

式中,Score为芯片内核的面积,μm2,可以通过做初步的平面规划确定;Ptotal为芯片内核消耗的总功耗,mW。

通过式(5)算出本设计中的Punit为0.020 05 μW/μm2。

其次,可以通过Punit算出n等分的标准单元电源轨道上每段的平均电流i的大小,公式如下:

(6)

式中,l代表每一段电源轨道的长度,μm;Wstd代表标准单元的高度(本设计为1.4 μm);Vcore代表芯片内核工作电压,为1.2 V。

再次,根据公式(7)计算第n段金属线上的电压降大小Vrail。

(7)

本设计中,Vrail的大小要求在电源电压的5%以内,所以可以设其大小为0.06 V。

最后,通过联立式(6)和式(7),可以算出n的大小,进而可以得到电源条的间距。计算得出,电源条的间距约为60 μm。

(2)计算电源条的宽度Wstrap

首先,考虑电源轨道能承受的最大电流Irail以及电源条要提供的电流Istrap。公式如(8)、(9)所示:

(8)

(9)

式中,Wrail为标准单元电源线宽度,μm;N为芯片的电源轨道的行数;Dm2为第二层金属(第二层金属是电源轨道所在的金属层)能承受的最大电流密度;Dm6为第六层金属(最高层金属)能承受的最大电流密度

其次,结合式(8)计算的结果,通过式(9)可以得出本设计所需的电源条的宽度Wstrap约为3 μm。这个数值可以根据设计的拥挤程度进行调整,过宽的电源条会使得布线出现多处阻塞。

根据以上的估算,做出的平面规划图示意图如图1所示。图1中,最外层一圈的蓝色方块是电源IO单元和辅助的物理单元。电源IO使用工艺库自带的PAD filler进行连接,再由工艺库中专门给电源IO供电的PVDD2RT型号的电源IO供电。内部则是芯片的内核部分。内核中包含标准单元、RAM和电源网络。中间紫色的区域是标准单元放置区,下方两个绿色的方块是RAM模块。芯片内核的电源环是图中黄色环状部分,用到了第5、6层金属。电源条构成图中红色的交叉网格,用到了第5、6层金属,电源轨道是图中蓝色细线,用到了第2层金属。

图1 芯片的平面规划图Fig.1 Floorplan of chip

2 芯片电源网络可靠性检验

设计出来的电源网络必须要经过严格的可靠性检验,通过后才可以流片。本设计检验工具是synopsys公司的PrimeRail。PrimeRail 是用于signoff阶段的验证工具,它做的各种分析准确度很高,通过了它的检验,可以达到流片的要求。本文主要用PrimeRail进行电源完整性检查、电压降分析以及电迁移分析。

2.1 电源完整性检查

完整性检查主要检查电源网络的物理连接是否可靠,一般分析以下几类问题[10]。

(1)浮空块和浮空引脚:即没有和其他电源网络连接的单独的金属块或引脚。

(2)悬挂块和悬挂引脚:只有一边和其他电源网络连接的金属块或引脚。

(3)悬挂通孔:只有一边和其他电源网络连接的通孔。

(4)通孔缺失:应该打通孔的位置没有通孔。

(5)金属断连和短路:应该连接的金属线中断或者不该相连的金属连在了一起。

一般在做完IC Compile流程中的place阶段后就可以将版图导入PrimeRail进行完整性验证,这样做可以保证place完后的电源网络不会有物理上的问题,也可以减少后面设计规则、版图原理图功能一致性检查时的错误。在创建完外部电源(taps)后,通过运行“check_supply_net_integrity”命令,即可在PrimeRail中进行该检查。本设计在该检查中存在一些通孔缺失问题,重新连线打孔后通过了该检查。

2.2 静态和动态电压降分析

电压降是指出现在芯片内部电源和地网络上电压下降或升高的一种现象,随着集成电路产业工艺的不断进步,金属互连线的宽度越来越窄,导致电源网络上的电阻值显著上升,电压降产生的问题已经严重影响芯片的正常工作[11]。为此,在设计芯片之前,一般都要对设计能容忍的最大电压降进行限制。本设计中要求,静态电压降的最大限值不超过电源电压VDD的3%。动态电压降约为静态电压降的4倍,即不超过VDD的12%。本设计中,芯片的电源电压VDD为1.2 V,VSS是地电压,为0 V。

2.2.1静态电压降分析

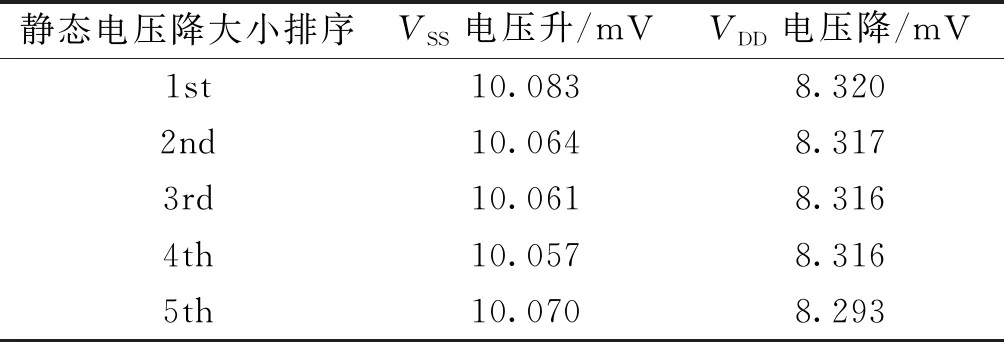

静态电压降主要是基于平均功耗分析得来的,得到的是平均电压降的大小[12]。平均功耗包含内部功耗、开关功耗以及泄露功耗三部分,其中,前两种功耗占了总功耗的90%。在做静态电压降分析时,本文采用的是Vector Less分析模式,即通过设置翻转率来计算芯片消耗的功耗大小,翻转率的大小设置为0.3。这样做的好处是可以提高效率,减少工具消耗在功耗计算的时间。缺点是计算的准确率会有所下降,所以要求设计者对所设计的芯片电路工作的模式和信号跳变情况比较熟悉,设置合理的翻转率大小。由于静态电压降的计算本身用到的是平均值,只要对翻转率估算得当,计算结果的偏差可以控制在10%左右,而运行时间可以减少80%。静态电压降分析得到的最大的5个VDD电压降和VSS电压升的值如表2所示。

表2 静态电压降值Tab.2 Static IR drop value

静态电压降的大小是VDD电压降和VSS电压升之和。分析得到VDD最大电压降为0.008 32 V,VSS最大电压升为0.010 083 V,所以静态电压降为0.018 4 V,小于3%VDD,符合项目要求。

2.2.2动态电压降分析

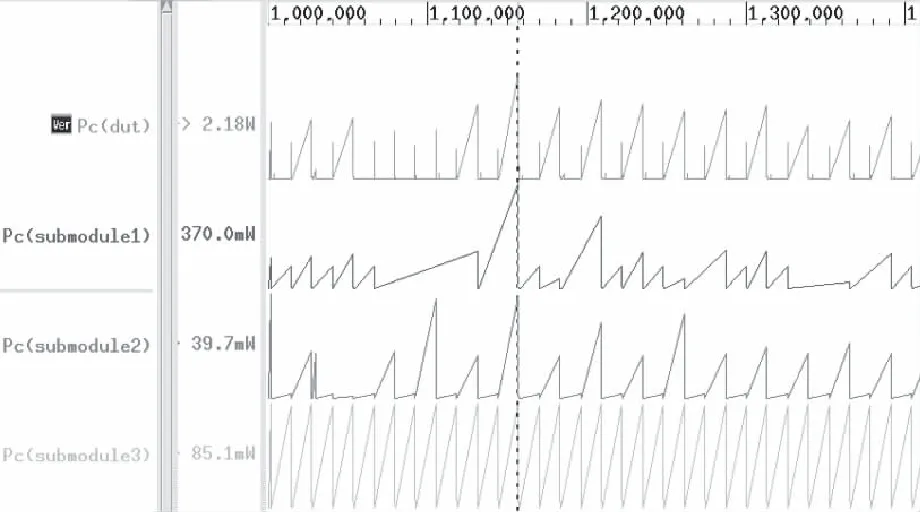

动态电压降分析主要是基于瞬态功耗分析得来的。在进行动态功耗分析时,对分析的准确率要求较高,本文采用Vector Based分析模式,即通过使用仿真得到精确的波形文件,全称为值变转储文件(Value Change Dump,VCD)。使用VCD提供的翻转数据可以计算瞬态功耗和电压降。分析得到的瞬态功耗波形如图2所示。

图2 动态功耗波形图Fig.2 Dynamic power waveform

图2中第一个波形DUT波形是整个被测模块,即芯片整体的功耗波形图,下面3个波形则是DUT中存在的三个子模块的功耗波形。由于是取VCD文件中芯片正常工作的时间段进行分析,所以整个功耗波形呈现规律性起伏。图2中虚线所在的时刻是功耗最大的时刻(1 157 ns处),峰值功耗为2.182 2 W。该功耗与前述工具分析得出的功耗约有20%的偏差,这是由于工具分析的精度不同,PrimeRail使用的功耗分析模型更为精确。为了避免该误差,之前设计电源网络时都留有一定的余量。

动态分析的结果如图3所示,颜色越红(深)的地方表示电压差越大。

图3 动态电压降(左边VSS,右边VDD)Fig.3 Dynamic IR drop (VSS on the left,VDD on the right)

分析得到VSS最大电压升为0.076 3 V,VDD最大电压降为0.063 9 V,所以最大的动态电压降为0.140 2 V,小于12%VDD,符合项目要求。但是最大电压降的部位与项目的限值相差不大,在实际制造中仍有可能出现违例。降低该部分的电压降有三种方式:一是在该区域插入去耦电容单元(decap cell);二是增大该区域电源网格的密度;三是调整电源IO的位置,使其更靠近此区域。本设计中只有一对电源IO,所以第三种方法并不适用,所以只尝试了前两种方法。

用第一种方法时,要选定范围,这里选择了图3中VSS和VDD红色(深色)区域重叠的部分,在该区域插入总电容约为10 pf的decap cell,插入完成后重新进行电源轨道分析,得到的VSS最大电压升为0.068 8 V,VDD最大电压降为0.057 6 V,动态电压降为0.126 4 V,为10.5%VDD。

第二种方法可以通过调整电源条的间距来增加区域电源网格密度,也可以在该区域额外打几条电源条。这里将图3红色(深色)区域附近的两对VDD、VSS电源条间距修改为45 μm,然后重新进行布线。经过测试得到,总电压降为0.132 4 V,约为11%VDD。要注意的是,该调整也会使区域之外的电源条间距加大,从而增加其他区域的电压降,所以调整的间距不能过大,一般为20%~30%。

上述的两种方法各有其适用情况:当设计周期较长或设计进入收尾阶段时,采用方法一可以快速解决局部电压降问题,不必再返工延长设计周期;当电压降违规区域恰好单元密度较大,没有足够位置插入decap cell时,采用方法二可以较好地解决问题。

2.3 电迁移分析

电迁移是金属原子在金属导体中被电子撞击发生位移的现象[13]。当通过导体的电流密度大到足以引起金属原子的位移时,就会发生这种问题。电迁移会造成金属线断路、相邻金属线短路等问题。在设计时,根据厂家提供的技术文件中的最大电流密度限制来设计金属导线,使得其上的电流密度始终保持在最大限制之下,就可以有效避免该问题。本文使用PrimeRail电迁移分析流程来验证所设计的电路的正确性。

本设计使用的电迁移规则是.tf文件中记录的规则信息,其中记录了各层金属以及通孔在不同模式下的最大电流密度限制。取峰值peak模式下的各层金属和通孔最大电流密度上限,如表3所示。峰值模式检查动态情况下,最大电流是否仍在电流密度容限内。在PrimeRail中运行“update_em”命令即可进行电迁移检查。在peak模式下,检查结果显示设计没有违例,满足了设计可靠性的要求。

表3 各物理层电流密度上限Tab.3 Current density of the layers

3 结语

在现在的集成电路设计中,电源网络的设计已经成为非常重要的环节。本文通过预先计算的方式,在设计电源网络之前对IR drop、电迁移等问题进行考虑,计算出电源IO数量,电源环和电源条的宽度、间距等参数,在此基础上完成了电源网络的设计及整个芯片的版图;使用PrimeRail作为验证工具,成功验证了本设计电源网络的可靠性,并取得了良好的效果,论证了前述计算方法的正确性。