一种采用互连线电容耦合的线计算电路设计

2022-07-04张会红张跃军

李 林,张会红,张跃军,2

(1.宁波大学 信息科学与工程学院,浙江 宁波 315211;2.复旦大学 专用集成电路与系统国家重点实验室,上海 201210)

随着集成电路制造技术的飞速发展,半导体工艺进入纳米时代,互连线的尺寸逐渐缩小,集成度逐渐提高,成本逐渐减少[1-2]。金属线宽度的变小导致其电阻变大,造成金属线延迟增加[3]。在先进的工艺节点下,增加金属线的垂直厚度是缓解线宽变小电阻增大的解决方案,但是器件的密集放置和金属线厚度的增加会造成互连线间横向电容增大,从而加剧耦合噪声,影响电路稳定性[4-5]。容性耦合是制约电路性能提升的关键因素,表现为干扰线上电压变化引起受扰线上感应电流而产生的电磁干扰现象。互连线之间的串扰将引入电路噪声,也会造成互连线延迟的不确定性[6-7]。随着半导体工艺节点的不断推进,互连线之间的串扰问题越来越突出[8]。互连线间的耦合电容噪声已经成为集成电路设计的挑战之一,引起研究者的广泛关注。文献[9]提出一种基于5线时延模型的精确串扰模型,用于估计存在串扰故障时通信信道的时延。为了降低耦合噪声,文献[10]提出一种具有缺陷接地平面结构的差分线路,可以抑制串扰耦合。文献[11]研究铜互连耦合模型在32 nm工艺节点上的串扰噪声,分析比较屏蔽插入技术和增加耦合互连线间物理间距对串扰的抑制作用。针对芯片长距离平行布线引起的串扰问题,笔者从正向利用电容耦合效应的角度出发,利用片上互连线间耦合电容设计逻辑门和简单组合逻辑电路,从而完成复杂逻辑运算。

1 互连线电容耦合机理及电路模型

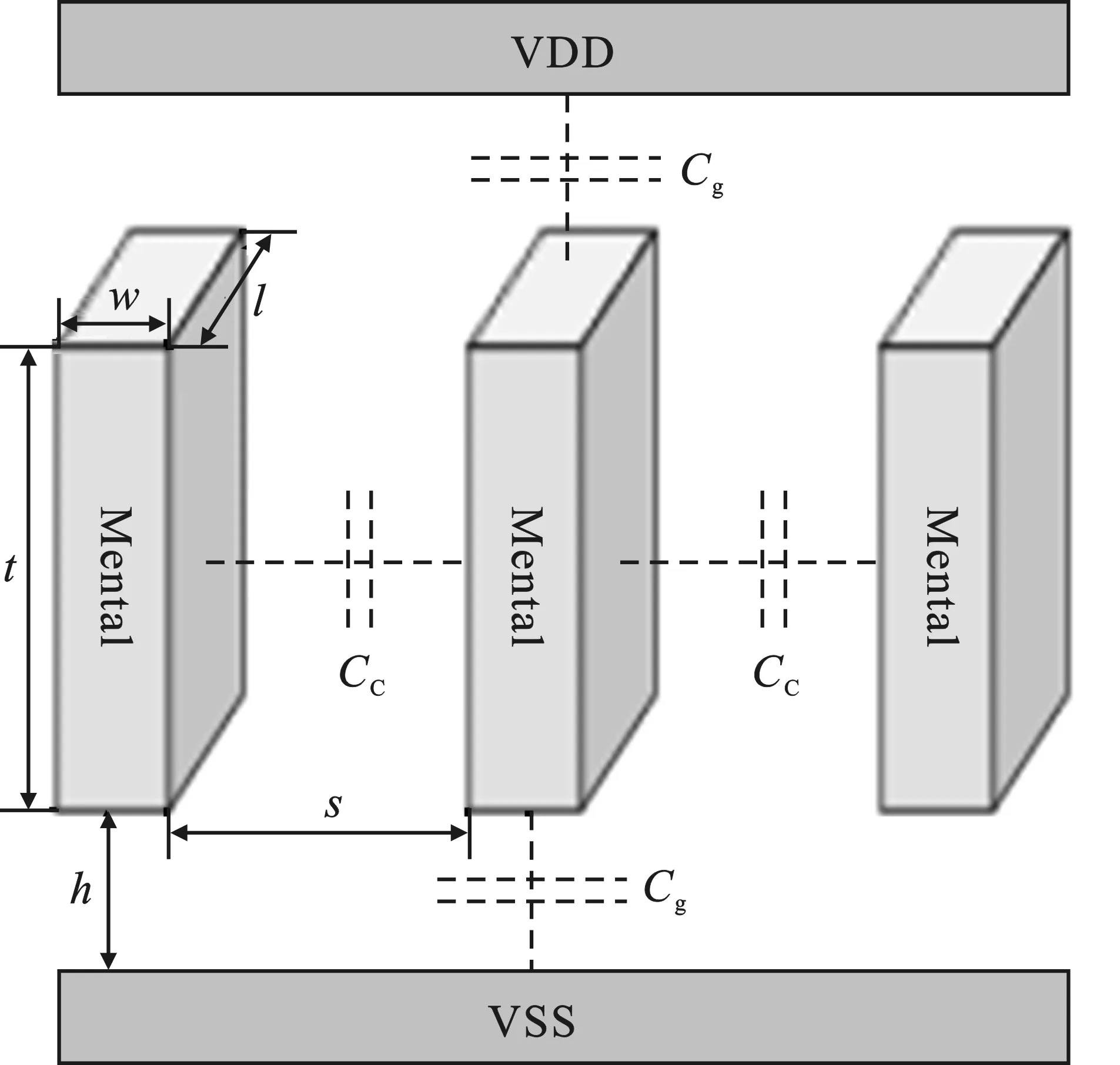

超大规模集成电路的片上互连资源越来越多,互连线总长度和复杂度增加,互连线之间形成的耦合串扰不能再被忽略[12-13]。采用多层金属线模型表示互连线间电容,三线并行互连结构如图1所示。

图1 多层互连线电容耦合结构

顶端金属线接VDD,底部金属线接VSS,模拟电源和地线对信号线产生的干扰,电源和地与金属线会形成耦合电容Cg,同层相邻金属线间会形成耦合电容CC,金属互连线的电容解析表达式如式(1)、式(2)所示[14-15]。金属线的长度、宽度、厚度、间距分别用变量l、w、t、s表示,金属互连线与地之间的距离用h表示。由电容计算公式C=εS/(4πKd)(其中ε是相对介电常数,S为电容极板的相对面积,K为静电力常量,d为金属线之间的距离)可知,耦合电容值大小与金属互连线间的相对介电常数和相对面积成正比,与金属互连线间距成反比。调节金属互连线长度、宽度、线间距等参数可以改变耦合电容大小,从而得到耦合强度不同的线间耦合电容:

(1)

(2)

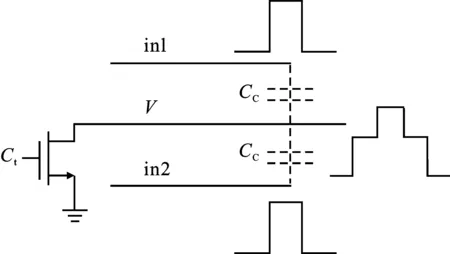

基于互连线电容耦合效应的研究,文献[16]提出一种新颖的互连线电容耦合电路模型,如图2所示。该电路模型采用金属线间的确定性干扰来模拟干扰线与受扰线的耦合场景,干扰线携带输入信号in1、in2,受扰线携带输出信号V,干扰线与受扰线之间会形成耦合电容CC,通过调节耦合电容值大小改变互连线之间的干扰程度。两条同层相邻金属互连线横向相对面积越大或线间距越小,两者之间的耦合电容值就越大,即干扰线对受扰线的干扰程度越大。当干扰线上的输入信号in1、in2跳变时,会在输出节点V处产生相应耦合电平信号[17]。因此,可以认为在受扰线上产生的信号拥有两根干扰线上信号的信息。基于以上结论,笔者在进一步研究干扰线与受扰线耦合强度调整技术的基础上,提出利用互连线电容耦合效应的逻辑计算电路设计技术,并将此类电路简称为线计算电路。在先进工艺节点上,利用金属线之间的确定性干扰设计逻辑电路,可以减少使用晶体管的数量和互连要求,为设计低成本的数字互补金属氧化物半导体集成电路提供新途径。

图2 互连线电容耦合模型

2 采用互连线电容耦合的门电路设计

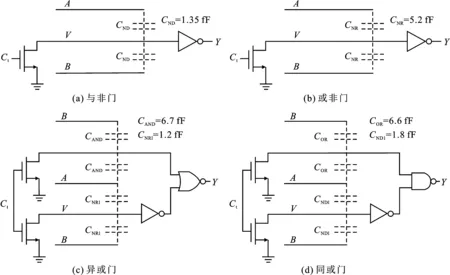

利用互连线电容耦合机理及模型设计线计算门电路。二输入线计算与非门结构如图3(a)所示,它仅由金属线、放电管和反相器构成,其中由Ct信号驱动的放电晶体管和一个反相器连接到受扰线两端。线计算电路工作在两种状态:放电状态(Discharge State,DS)和求值状态(Evaluation State,ES)。在放电过程中,Ct为高电平时放电晶体管导通,受扰节点V通过放电晶体管接地;Ct为低电平时放电晶体管不导通,相当于一个大电阻。因此,放电过程可以清除前一个逻辑计算的值,确保在下一个求值状态进行正确的逻辑操作,也保证与其他电路的同步。在求值过程中,干扰线电压的上升跃变在受扰线上产生感应电压,经过反相器输出标准逻辑电平便于驱动下一级门电路。每次逻辑求值完成后,将Ct设置为高电平,释放节点V处电压。对于二输入与非门电路,前一个放电周期结束,节点V处于零电压,仅当求值状态下两个输入都从逻辑0跃迁到逻辑1,节点V处电压累加为逻辑1,再经阈值反相器输出逻辑0,其他输入转换情况输出都为逻辑1,以实现二输入与非门逻辑功能。

同理,设计二输入或非门如图3(b)所示。二输入或非门与二输入与非门电路结构相同,区别点在于干扰线和受扰线间的耦合强度。对于二输入或非门,只要有一个输入(A或B)从逻辑0跃迁到逻辑1时,经耦合电容CNR感应到受扰节点V处的逻辑值即为1,再经低阈值反相器整形输出为逻辑0,以实现二输入或非门的逻辑功能。因此,实现二输入或非门比实现二输入与非门需要更大的耦合电容,反映为干扰线和受扰线之间的耦合强度更大,使受扰线在变化程度相同的电压干扰下产生的求和电压更高,确保正确输出逻辑功能。

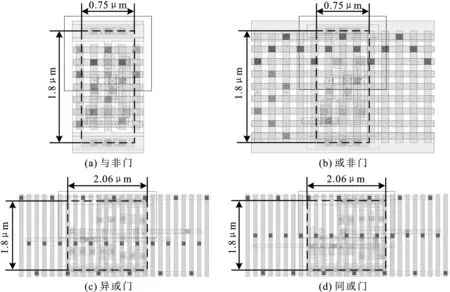

基于上述原理设计互连线电容耦合的二输入与非门、二输入或非门电路版图,分别如图4(a)、图4(b)所示。设计的耦合电容值大小通过设置干扰线与受扰线之间的正对面积和间距来实现。干扰线和受扰线采用高层金属布线,充分利用版图面积。

基于互连线电容耦合机理,进一步实现四输入与非门、异或门、同或门等复杂的逻辑门电路。干扰线数量与逻辑门的扇入相等,四输入与非门有四根干扰线,相比于二输入与非门增加了两根干扰线,对应增加了两个耦合电容。互连线电容耦合的异或门由线计算的与门、或非门和互补金属氧化物半导体或非门构成,其逻辑表达式为Y=(AB+(A+B)′)′,电路结构及版图分别如图3(c)、图4(c)所示。互连线电容耦合的同或门由线计算的或门、与非门和互补金属氧化物半导体与非门构成,其逻辑表达式为Y=((A+B)(AB)′)′,电路结构及版图分别如图3(d)、图4(d)所示。

(a) 与非门

图3 采用互连线电容耦合的二输入门电路结构

图4 采用互连线电容耦合的二输入门电路版图

由于任何函数都可以分解成与非门-与非门、或非门-或非门、与门-或门-非门等组合形式,因此所述的线计算方法在逻辑上是完备的。这种电路结构中含有金属线、放电管和反相器,通过调节干扰线和受扰线之间的耦合强度,可以实现不同功能的门电路,并在反相器输出端得到标准的逻辑电平,便于与下一级电路级联。

3 采用互连线电容耦合的译码器设计

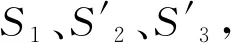

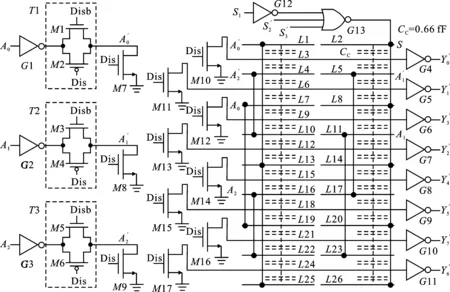

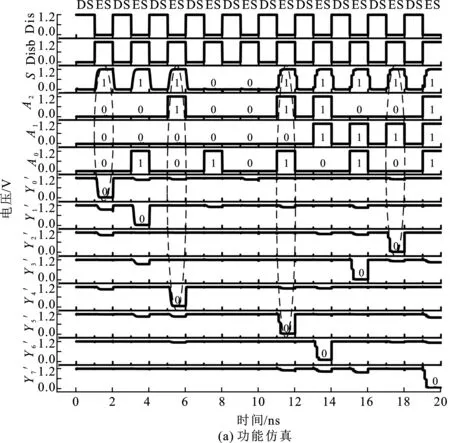

互连线电容耦合的3线-8线译码器中有8个四输入线计算与非门,四输入线计算与非门由4根干扰线、1根受扰线、1个放电管和1个反相器构成。受扰线两端分别连接放电晶体管和阈值反相器,4根干扰线与其相邻平行放置,调节干扰线与受扰线的耦合强度,可实现四输入与非门逻辑功能。如图5所示的金属线L1、L2、L3、L4、L5,N沟道金属氧化物半导体晶体管M10和反相器G4可以构成一个四输入与非门。采用互连线电容耦合的3线-8线译码器版图如图6所示,图5的32个耦合电容CC利用高层金属线实现,其值为0.66 fF。该3线-8线译码器由47个晶体管和互连线组成,版图面积为22.104 μm2。因此,线计算能以更紧凑的方式实现组合逻辑电路。

图5 采用互连线电容耦合的3线-8线译码器结构

图6 采用互连线电容耦合的3线-8线译码器版图

4 实验仿真与分析

采用台积电65 nm互补金属氧化物半导体工艺,实现了线计算门电路和3线-8线译码器设计,并利用Cadence Virtuoso IC5141和Cadence Spectre进行后端版图瞬态仿真测试分析,遍历所有激励。

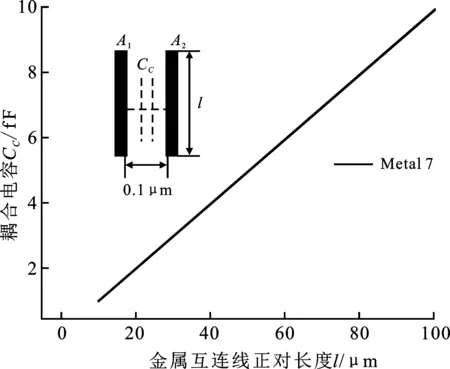

4.1 电容耦合效应

将2条宽度为0.1 μm的金属线平行放置,金属互连线间距设置为0.1 μm,模拟高层金属Metal 7的两相邻金属线之间的电容耦合情况,耦合电容大小与2条金属线的正对长度之间的关系测试结果如图7(a)所示。进一步,将3条金属线等间距平行放置模拟其耦合情况。中间金属线为受扰线,旁边两条为干扰线,调节干扰线与受扰线的正对长度,可以改变干扰线对受扰线的干扰程度,受扰节点电压与耦合电容大小的关系曲线如图7(b)所示。干扰线与受扰线耦合作用程度的不同,受扰节点V处产生的耦合电压就不同,当2条干扰线同时上升跃变时,受扰节点V处产生的信号电压值更高。利用以上结论,通过调整下级反相器阈值,可以实现多种门电路功能。实现二输入与非门是将反相器阈值设置在图7(b)所示的曲线Ⅰ与曲线Ⅱ中间,而实现二输入或非门则需要更低阈值的反相器,应设置在曲线Ⅱ以下。

(a) 两线耦合

4.2 线计算门电路仿真

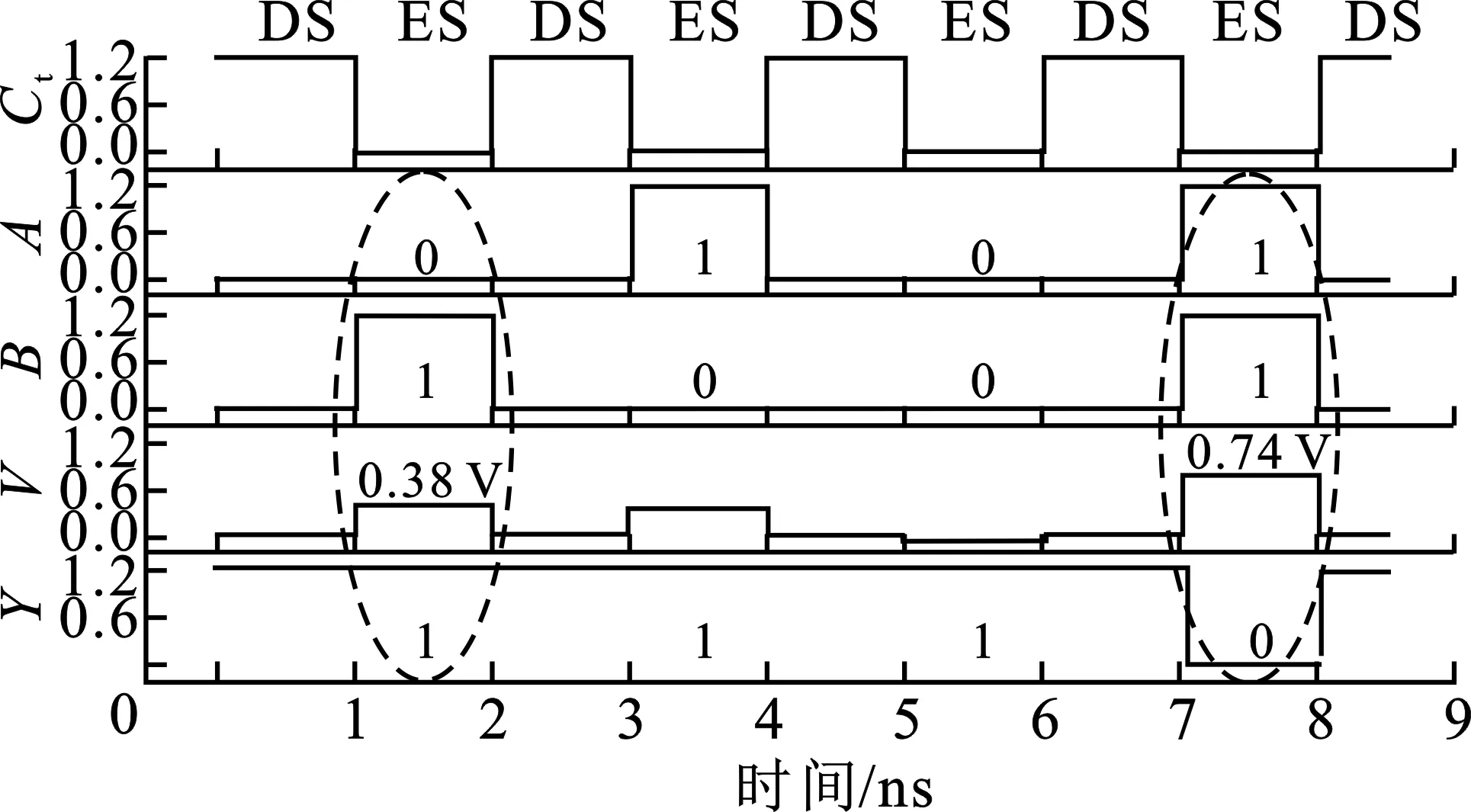

对于图3(a)所示互连线电容耦合的二输入与非门,功能仿真结果如图8(a)所示。初始时,Ct为高电平,受扰节点V放电至逻辑0。在1 ns时刻,设置Ct为低电平,进入逻辑求值状态,输入A为逻辑0,输入B从逻辑0跃变到逻辑1,干扰线B信号的上升跃变在受扰节点V处产生0.38 V感应电压,经阈值反相器采样输出Y为逻辑1。同理,在3 ns时刻,干扰线A信号的上升跃变也会在受扰节点V处产生感应电压。在5 ns时刻,由于没有干扰线信号从逻辑0跃迁到逻辑1,所以受扰节点V处电压为逻辑0。在每次求值完后,电路放电至逻辑0,清除上一个求值状态的逻辑值,确保下一个求值状态逻辑操作正确。在7 ns时刻,干扰线A信号和干扰线B信号同时发生上升跃变,在受扰节点V处产生累加电压为0.74 V,经下级反相器采样输出Y为逻辑0。

对于图3(b)所示互连线电容耦合的二输入或非门,功能仿真结果曲线如图8(b)所示。在1 ns时刻,由于干扰线B信号的上升跃变,经耦合电容的作用,电荷被引入到受扰节点V处,产生0.51 V的感应电压,经低阈值反相器整形输出Y为逻辑0。在5 ns时刻,没有干扰线信号发生上升跃变,在受扰节点处的感应电压最低,连接到受扰节点V的反相器可以使逻辑翻转,采样输出Y为逻辑1。在7 ns时刻,干扰线A信号和干扰线B信号同时发生上升跃变,通过电容耦合在受扰节点V处产生累加电压为1.06 V,最终采样输出Y为逻辑0。

将互连线电容耦合的与非门、或非门与互补金属氧化物半导体电路相融合,调节干扰线和受扰线之间的耦合强度,可以实现特定逻辑功能,如异或门、同或门等。互连线电容耦合的二输入异或门和二输入同或门功能仿真结果曲线分别如图8(c)、图8(d)所示。仿真结果表明所设计的电路逻辑功能正确。线计算门电路可以与互补金属氧化物半导体电路相连接,从而实现具有线计算能力的复杂逻辑电路。

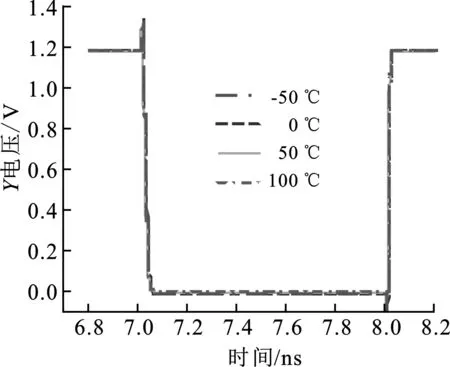

在台积电65 nm互补金属氧化物半导体工艺下,仿真不同温度对门电路延时的影响情况。当温度从-50 ℃到100 ℃变化时,逻辑门电路的延时情况如图9所示,结果表明所设计的与非门、或非门、异或门、同或门电路延时受温度影响小。

(a) 与非门

4.3 线计算译码电路仿真

图10 采用互连线电容耦合的3线-8线译码器仿真曲线

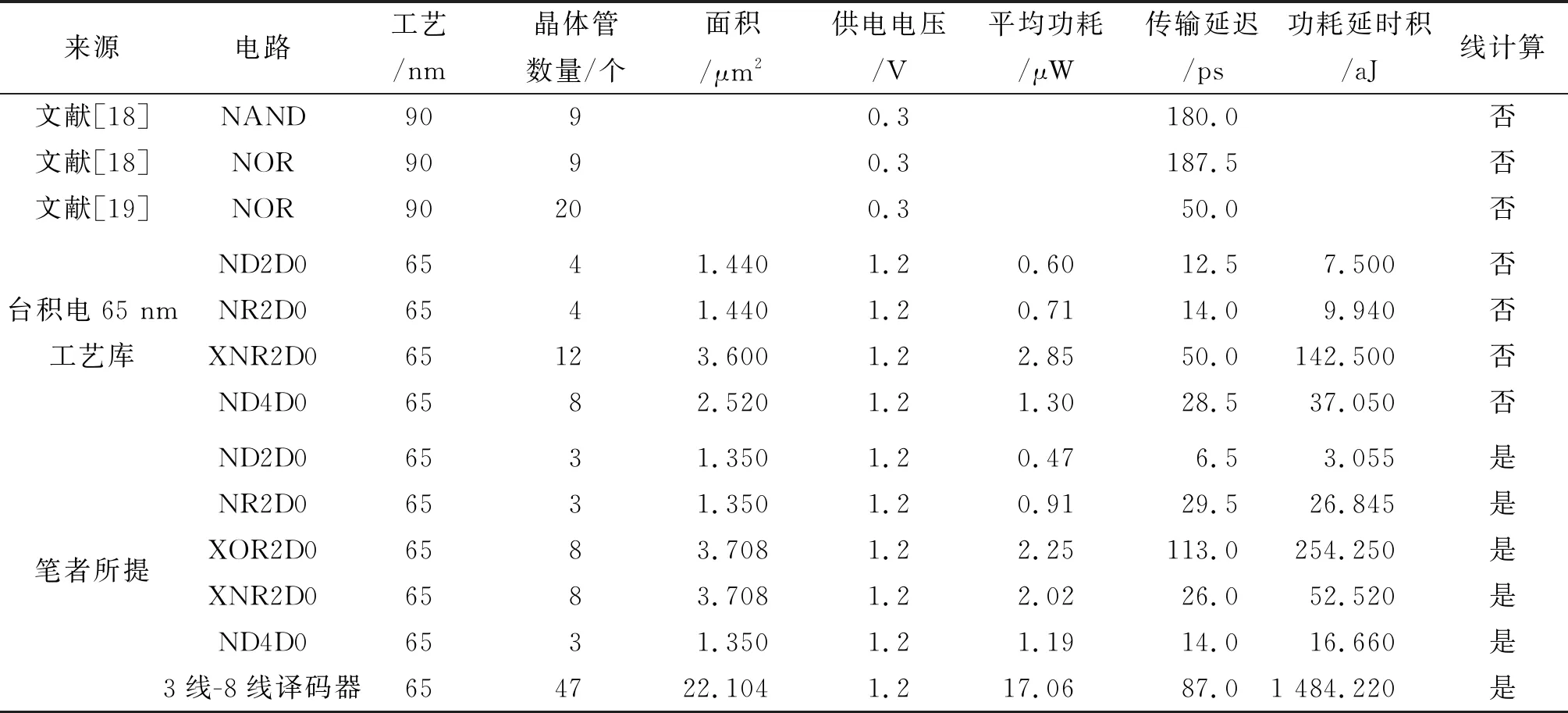

4.4 与相关文献比较

与相关文献的比较结果如表1所示。由表1可以得出,与台积电65 nm工艺库的标准单元相比,二输入与非门的晶体管数量、功耗延时积分别减少约25%、59.3%;四输入与非门的电路面积、功耗延时积分别减少约46.4%、55%;二输入同或门的晶体管数量、功耗延时积分别减少约33.3%、63.1%。与文献[18]相比,二输入与非门的晶体管数量、传输延迟分别减少约66.7%、96.4%;二输入或非门的晶体管数量、传输延迟分别减少约66.7%、84.3%。与文献[19]相比,二输入或非门的晶体管数量、传输延迟分别减少约85%、41%。因此,所设计的线计算电路减少了晶体管数量,在一定程度上减少了电路面积、功耗以及提高了电路性能。

表1 线计算电路与相关文献比较结果

5 结束语

笔者在研究金属互连线间电容耦合效应的基础上,探索在先进技术节点上利用高层金属线之间的串扰来完成相关逻辑计算的有效方案。构建了互连线电容耦合模型,通过调整反相器阈值和金属互连线间电容耦合强度等技术手段,在台积电65 nm工艺下完成了与非门、或非门、异或门、同或门和3线-8线译码器的方案设计。仿真测试结果表明所设计的电路逻辑功能正确,能以数量更少的晶体管实现更复杂的逻辑电路模块,提供了更密集实现数字互补金属氧化物半导体集成电路的机会。