《数字逻辑电路》中触发器的应用教学探讨

2022-06-30王华本

【摘 要】 探讨《数字逻辑电路》中触发器的应用线上教学。从集成边沿JK触发器入手,借助Proteus仿真电路,分析JK触发器的电路结构、功能真值表、卡诺图、特征方程、状态转换图、驱动表、时序图等七个方面;由Proteus仿真实践融合理论分析得出由触发器构成的应用电路,并分析电路功能,总结规律,实现了线上教学的时效性、扩展性和灵活性。

【关键词】 数字逻辑电路;触发器;时序图;卡诺图

Discussion on the Application Teaching of Trigger in "Digital Logic Circuit"

Wang Huaben

(Anhui Xinhua University, Hefei 230088, China)

【Abstract】 This paper discussesonline teaching of the application of triggers in "Digital Logic Circuits" . Starting from the integrated edge JK flip-flop, with the aid of the Proteus simulation circuit, the paper analyzes the circuit structure of the JK flip-flop, functional truth table, Karnaugh map, characteristic equation, state transition diagram, drive table, timing diagram and other seven aspects.Simulated by Proteus Practical fusion theory analysis,the paper obtains the application circuit composed of flip-flops, analyzes the circuit function, summarizes the rules, and realizes the timeliness, scalability and flexibility of online teaching.

【Key words】 digital logic circuit;triggers; timing diagram;Karnaugh map

〔中圖分类号〕 TN791-4 〔文献标识码〕 A 〔文章编号〕 1674 - 3229(2022)02- 0123 - 06

0 引言

新冠疫情使线上教学成为高校不得不选择的教学形式。计算机类专业的《数字逻辑电路》硬件课程从线下转移到线上,无形中难度增大。将仿真教学平台融入到线上教学中,结合Proteus仿真实践与理论进行线上教学,并将《数字逻辑电路》中触发器应用到线上教学中,提高了教学效果。触发器的应用学习过程,如何从简单的1个触发器,拓宽到2个触发器、3个触发器,再到复杂的4个触发器,怎样一步一步深入教学,这个过程是必须要思考的问题[1]。电路可以进行拓展,由减法计数器如何变成加法计数器,电路中时钟信号的作用,高级触发器如何与低级触发器进行级联,这些都是教学过程中要思考的问题,从JK触发器如何推导D触发器、T触发器、T′触发器,它们之间是如何关联的,如何逐层深入获取信息,仿真电路在整个分析过程中所起到的作用,本文针对这些问题,探讨《数字逻辑电路》中触发器的应用教学。

1 JK触发器

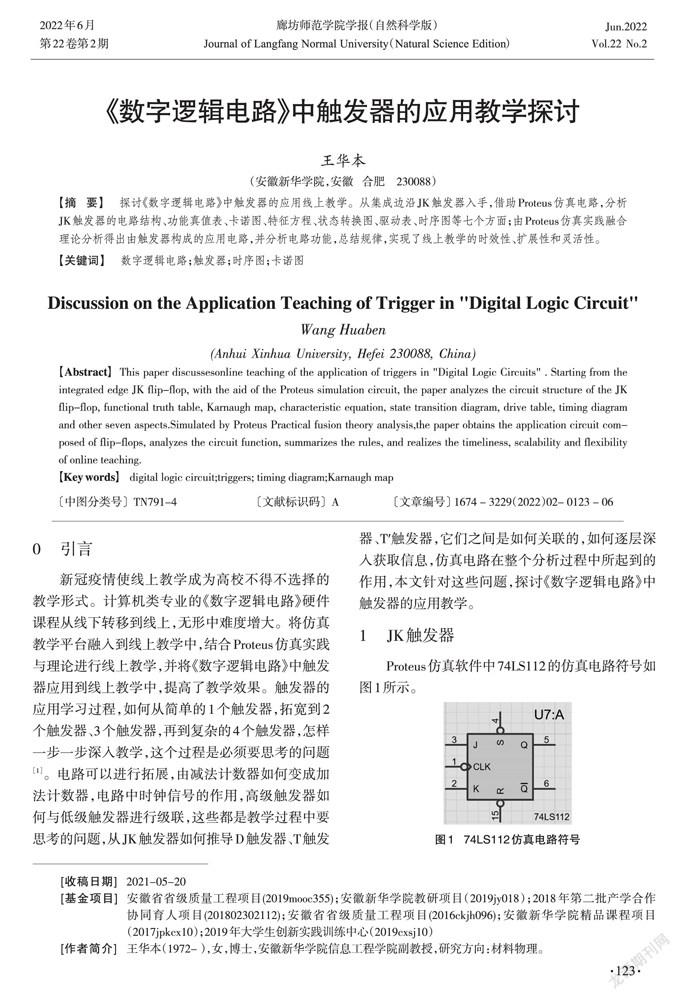

Proteus仿真软件中74LS112的仿真电路符号如图1所示。

74LS112仿真电路符号可以分为五个部分:输入端J、K;时钟信号CLK,下降沿触发有效;清零端R,低电平触发有效;置1端S,低电平触发有效;互补输出端Q、Q′。 74LS112的仿真电路如图2所示。

分别给74LS112的五个部分加载信号,这里的清零和置1优先级别最高,只要R、S处于相异状态,触发器就锁定在清零状态或者置1状态,R=0,S=1或者R=1,S=0,此时触发器的状态跟R一致,R、S其实就是设置触发器的初始状态[2-3]。通过仿真实验可以得出实验结果,从Proteus仿真电路图可以做6组仿真实验。

第一组清零实验,当R处于低电平时候,输出为0;第二组置“1”实验,当S处于低电平时候,输出为1;第三组仿真实验:当输入信号J、K分别是0、0时,输出状态保持原来状态;第四组仿真实验:当输入信号J、K分别是0、1时,输出状态保持J的状态;第五组仿真实验:当输入信号J、K分别是1、0时,输出状态保持J的状态;第六组仿真实验:当输入信号J、K分别是1、1时,输出状态取非。把以上六组仿真实验总结74LS112的功能真值表如表1所示。

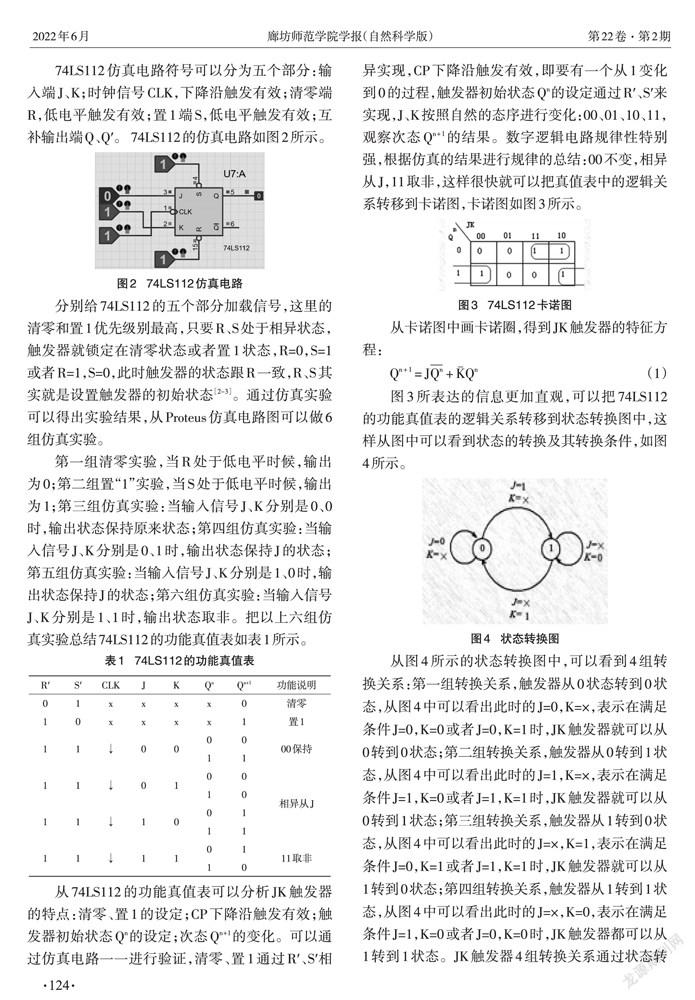

从74LS112的功能真值表可以分析JK触发器的特点:清零、置1的设定;CP下降沿触发有效;触发器初始状态Q的设定;次态Q的变化。可以通过仿真电路一一进行验证,清零、置1通过R′、S′相异实现,CP下降沿触发有效,即要有一个从1变化到0的过程,触发器初始状态Q的设定通过R′、S′来实现,J、K按照自然的态序进行变化:00、01、10、11,观察次态Q的结果。数字逻辑电路规律性特别强,根据仿真的结果进行规律的总结:00不变,相异从J,11取非,这样很快就可以把真值表中的逻辑关系转移到卡诺图,卡诺图如图3所示。

从卡诺图中画卡诺圈,得到JK触发器的特征方程:

图3所表达的信息更加直观,可以把74LS112的功能真值表的逻辑关系转移到状态转换图中,这样从图中可以看到状态的转换及其转换条件,如图4所示。

从图4所示的状态转换图中,可以看到4组转换关系:第一组转换关系,触发器从0状态转到0状态,从图4中可以看出此时的J=0,K=×,表示在满足条件J=0,K=0或者J=0,K=1时,JK触发器就可以从0转到0状态;第二组转换关系,触发器从0转到1状态,从图4中可以看出此时的J=1,K=×,表示在满足条件J=1,K=0或者J=1,K=1时,JK触发器就可以从0转到1状态;第三组转换关系,触发器从1转到0状态,从图4中可以看出此時的J=×,K=1,表示在满足条件J=0,K=1或者J=1,K=1时,JK触发器就可以从1转到0状态;第四组转换关系,触发器从1转到1状态,从图4中可以看出此时的J=×,K=0,表示在满足条件J=1,K=0或者J=0,K=0时,JK触发器都可以从1转到1状态。JK触发器4组转换关系通过状态转换图的形式呈现出来,逻辑关系非常清楚,在分析时序逻辑电路功能的时候,状态转换图可以直接体现电路的逻辑功能[4-5]。

状态转换真值表是分析时序逻辑电路的基础,驱动表是设计时序逻辑电路的基础,JK触发器的驱动如表2所示。

如果使用驱动表的方法设计时序逻辑电路,可以直接根据状态转换真值表的关系映射到驱动表,找到J、K的逻辑关系,把逻辑关系一一对应到卡诺图,通过卡诺图化简,就可以直接得出J、K的函数表达式,即驱动方程。如果不使用驱动表的方法设计电路,设计的过程比较复杂,需要先得出每个触发器的状态方程,然后和JK触发器的特征方程一一进行比对,最后得出驱动方程。

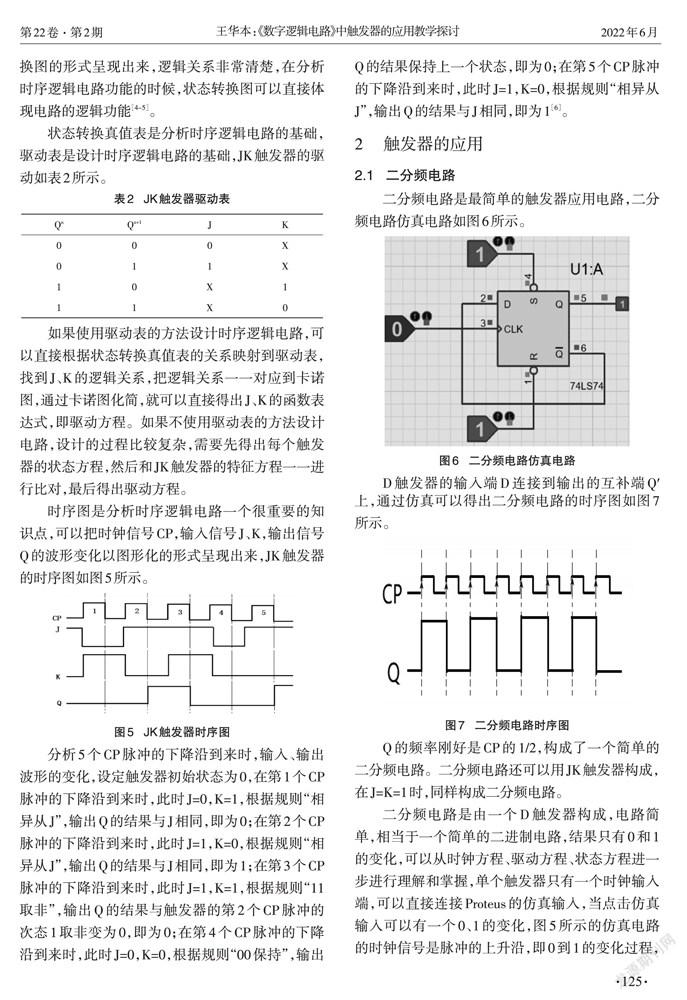

时序图是分析时序逻辑电路一个很重要的知识点,可以把时钟信号CP,输入信号J、K,输出信号Q的波形变化以图形化的形式呈现出来,JK触发器的时序图如图5所示。

分析5个CP脉冲的下降沿到来时,输入、输出波形的变化,设定触发器初始状态为0,在第1个CP脉冲的下降沿到来时,此时J=0,K=1,根据规则“相异从J”,输出Q的结果与J相同,即为0;在第2个CP脉冲的下降沿到来时,此时J=1,K=0,根据规则“相异从J”,输出Q的结果与J相同,即为1;在第3个CP脉冲的下降沿到来时,此时J=1,K=1,根据规则“11取非”,输出Q的结果与触发器的第2个CP脉冲的次态1取非变为0,即为0;在第4个CP脉冲的下降沿到来时,此时J=0,K=0,根据规则“00保持”,输出Q的结果保持上一个状态,即为0;在第5个CP脉冲的下降沿到来时,此时J=1,K=0,根据规则“相异从J”,输出Q的结果与J相同,即为1[6]。

2 触发器的应用

2.1 二分频电路

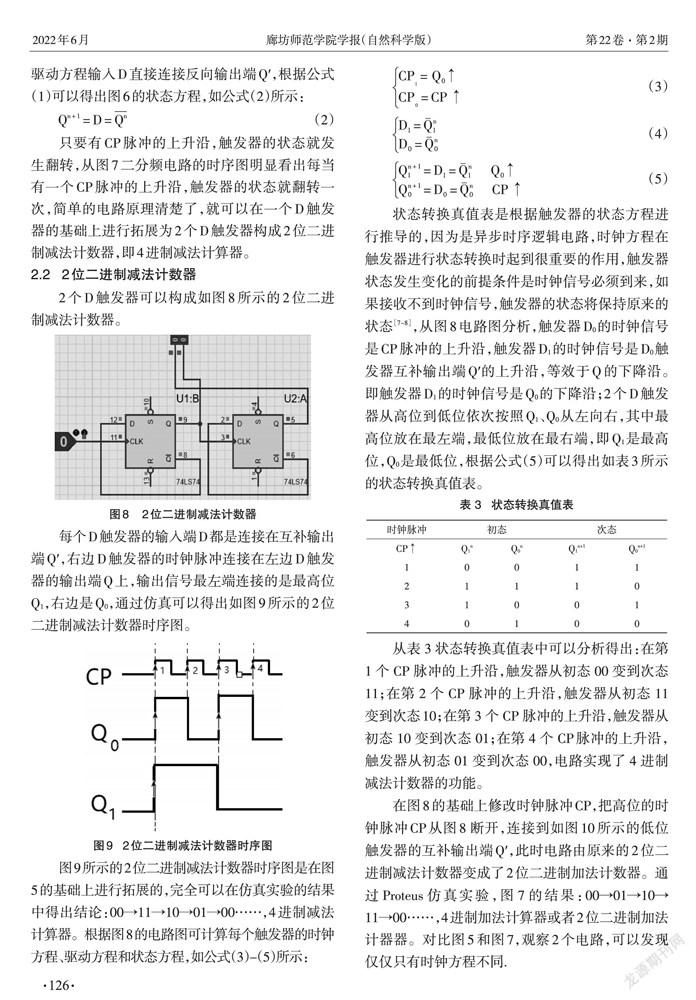

二分频电路是最简单的触发器应用电路,二分频电路仿真电路如图6所示。

D触发器的输入端D连接到输出的互补端Q′上,通过仿真可以得出二分频电路的时序图如图7所示。

Q的频率刚好是CP的1/2,构成了一个简单的二分频电路。二分频电路还可以用JK触发器构成,在J=K=1时,同样构成二分频电路。

二分频电路是由一个D触发器构成,电路简单,相当于一个简单的二进制电路,结果只有0和1的变化,可以从时钟方程、驱动方程、状态方程进一步进行理解和掌握,单个触发器只有一个时钟输入端,可以直接连接Proteus的仿真输入,当点击仿真输入可以有一个0、1的变化,图5所示的仿真电路的时钟信号是脉冲的上升沿,即0到1的变化过程,驱动方程输入D直接连接反向输出端Q′,根据公式(1)可以得出图6的状态方程,如公式(2)所示:

只要有CP脉冲的上升沿,触发器的状态就发生翻转,从图7二分频电路的时序图明显看出每当有一个CP脉冲的上升沿,触发器的状态就翻转一次,简单的电路原理清楚了,就可以在一个D触发器的基础上进行拓展为2个D触发器构成2位二进制减法计数器,即4进制减法计算器。

2.2 2位二进制减法计数器

2个D触发器可以构成如图8所示的2位二进制减法计数器。

每个D触发器的输入端D都是连接在互补输出端Q′,右边D触发器的时钟脉冲连接在左边D触发器的输出端Q上,输出信号最左端连接的是最高位Q,右边是Q,通过仿真可以得出如图9所示的2位二进制减法计数器时序图。

图9所示的2位二进制减法计数器时序图是在图5的基础上进行拓展的,完全可以在仿真实验的结果中得出结论:00→11→10→01→00……,4进制减法计算器。根据图8的电路图可计算每个触发器的时钟方程、驱动方程和状态方程,如公式(3)-(5)所示:

状态转换真值表是根据触发器的状态方程进行推导的,因为是异步时序逻辑电路,时钟方程在触发器进行状态转换时起到很重要的作用,触发器状态发生变化的前提条件是时钟信号必须到来,如果接收不到时钟信号,触发器的状态将保持原来的状态[7-8],从图8电路图分析,触发器D的时钟信号是CP脉冲的上升沿,触发器D的时钟信号是D触发器互补输出端Q′的上升沿,等效于Q的下降沿。即触发器D的时钟信号是Q的下降沿;2个D触发器从高位到低位依次按照Q、Q从左向右,其中最高位放在最左端,最低位放在最右端,即Q是最高位,Q是最低位,根据公式(5)可以得出如表3所示的状态转换真值表。

从表 3 状态转换真值表中可以分析得出:在第 1 个 CP 脉冲的上升沿,触发器从初态 00 变到次态 11;在第 2 个 CP 脉冲的上升沿,触发器从初态 11 变到次态10;在第 3 个 CP 脉冲的上升沿,触发器从初态 10 变到次态 01;在第 4 个 CP脉冲的上升沿,触发器从初态 01 变到次态 00,电路实现了 4 进制减法计数器的功能。

在图8的基础上修改时钟脉冲CP,把高位的时钟脉冲CP从图8 断开,连接到如图10所示的低位触发器的互补输出端Q′,此时电路由原来的2位二进制减法计数器变成了2位二进制加法计数器。通过Proteus仿真实验,图7的结果:00→01→10→11→00……,4进制加法计算器或者2位二进制加法计器器。对比图5和图7,观察2个电路,可以发现仅仅只有时钟方程不同.

2.3 3位二进制减法计数器

3个D触发器可以构成如图11所示的3位二进制减法计数器。

每个D触发器的输入端D都是连接在互补输出端Q′,高位D触发器的时钟脉冲连接在低位D触发器的输出端Q上,输出信号依次为Q、Q、Q,其中最左端连接的是最高位Q,最低位是Q,通过仿真得到如图12所示的3位二进制减法计数器时序图。

在图11的基础上修改时钟脉冲CP,把高位的时钟脉冲CP从图11 断开,连接到如图13所示的低位触发器的互补输出端Q′,此时电路由原来的3位二进制减法计数器变成了3位二进制加法计数器。

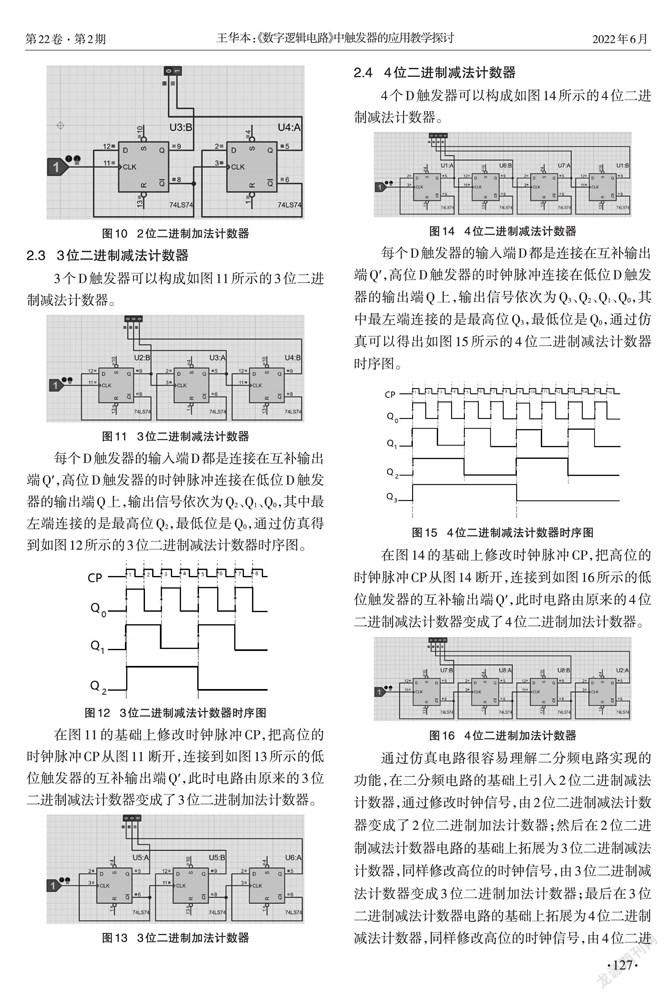

2.4 4位二进制减法计数器

4个D触发器可以构成如图14所示的4位二进制减法计数器。

每个D触发器的输入端D都是连接在互补输出端Q′,高位D触发器的时钟脉冲连接在低位D触发器的输出端Q上,输出信号依次为Q、Q、Q、Q,其中最左端连接的是最高位Q,最低位是Q,通过仿真可以得出如图15所示的4位二进制减法计数器时序图。

在图14的基础上修改时钟脉冲CP,把高位的时钟脉冲CP从图14 断开,连接到如图16所示的低位触发器的互补输出端Q′,此时电路由原来的4位二进制减法计数器变成了4位二進制加法计数器。

通过仿真电路很容易理解二分频电路实现的功能,在二分频电路的基础上引入2位二进制减法计数器,通过修改时钟信号,由2位二进制减法计数器变成了2位二进制加法计数器;然后在2位二进制减法计数器电路的基础上拓展为3位二进制减法计数器,同样修改高位的时钟信号,由3位二进制减法计数器变成3位二进制加法计数器;最后在3位二进制减法计数器电路的基础上拓展为4位二进制减法计数器,同样修改高位的时钟信号,由4位二进制减法计数器变成4位二进制加法计数器。

3 结语

《数字逻辑电路》的规律性很强,讲解触发器的应用电路时,必须先把单元电路的原理从电路结构、功能真值表、卡诺图、特征方程、状态转换图、驱动表、时序图等七个方面分析清楚,在分析的过程中可以借助Proteus仿真教学。通过仿真实践,能够理解电路的逻辑功能,找到电路的规律,再重新分析电路的原理,就容易找到各个变量的逻辑关系。Proteus仿真实践是《数字逻辑电路》教学的有益助手,是理论与实践的桥梁。

[参考文献]

[1] 朱正东,田靖轩,张小雨. MOOC混合教学模式及其在数字逻辑电路课程中的应用[J]. 计算机教育,2018(7):104-107.

[2] 王华本,朱良月,鹿建银.Proteus在《数字逻辑电路》课程教学中的应用[J].科技视界,2020(4):46-48.

[3] 刘钊,邓春健. 数字逻辑电路课程教学软件的设计[J]. 实验室研究与探索,2017,36(1):140-143.

[4] 沈姗姗,张晨,曹芳,等. 基于Multisim的数字逻辑电路双语实验教学改革探讨[J]. 当代教育实践与教学研究(电子刊),2017(2):215-216.

[5] 丁淑妍,李世宝,蔡丽萍,等. 基于CDIO理念的数字逻辑电路教学改革探索与实践[J]. 教育现代化,2018(48):103-104.

[6] 易艺. 高校数字逻辑电路实验教学探索[J]. 广西教育,2018(47):157-158.

[7] 潘学文,赵全友. Multisim在数字电路课程教学中的应用[J]. 实验技术与管理,2017,34(11):130-132.

[8] 肖杰,李强,龙胜春,等. 数字逻辑电路课程设计实验教学改革与实践[J]. 计算机教育,2018(5):75-79.