基于微调和斩波调制的多路低输出带隙基准源

2022-06-29赵婵君赵宏亮赵建中

赵婵君,赵宏亮,赵建中

(1.辽宁大学物理学院,辽宁沈阳 110031;2.中国科学院微电子研究所智能感知中心,北京 100029)

带隙基准是集成电路设计中很重要的一个部分,它为电路提供基准电压,对电路性能有显著的影响[1],并广泛应用于ADC、DAC、运放中,电路中的功耗、电源抑制比、开环增益和温度等特性都与它有直接关系,但随着晶体管越来越高的集成度,使电源电压在不断减小,工艺偏差及晶体管的不匹配带来的误差对带隙基准的精度影响很大[2]。为减小这一失调电压,一般采用大尺寸器件的运放并选择叉指结构的版图布局来减小失调或通过特殊的电路结构来抑制[3]。

该文设计了一款采用微调技术[4]和斩波技术[5-6]实现的高精度低输出带隙基准源。微调技术可以补偿电阻和三极管失配导致的PTAT 电压误差;斩波技术是利用调制和解调,将低频失调电压调制到斩波频率处,而有用信号经过调制后又解调到低频处,然后通过低通滤波器将高频处的频率成分滤除掉,达到降低失调电压的效果[7-8]。

1 误差及原理分析

带隙电压源的零温度系数的基准为:

但带隙基准中运算放大器的晶体管的不匹配性会影响输出电压,产生误差。这种影响被量化为VBE1-VOS≈VBE2+R3IC2(如果A1 很大)和VOUT=VBE2+(R3+R2)IC2。

VOS被放大了倍,在VOUT中引入了误差,且VOUT本身受温度影响,因此提高了输出电压的温度系数。所以,可通过减小运放的失调电压来提高带隙的精度[9]。

斩波稳压放大器是A/D 转换器的一部分,它不受调制器输入处低频噪声的影响。自70 年代以来,为了减少MOS 放大器的偏置电压的影响,采用斩波稳定放大器实现了比较器。一个典型的应用实例是测量加速度和压力的电容式传感器。利用斩波稳定器消除了偏移量、1/f噪声和开关电荷注入的影响,可以实现高分辨率和低漂移。

一般来说,斩波稳定放大器是低噪声连续时间放大器,用于放大直流和甚低频信号,主要用于仪器仪表的应用,如生物医学电子和光电子。通常设计目标是达到微电压水平的偏置和噪声,带宽限制在几百赫兹,同时保持功耗在100 W 以下。因此该设计主要采用斩波技术和微调技术来提高带隙基准源的精度。

斩波技术使用交流载波对输入信号进行幅度调制,原理如图1(a)所示[10]。斩波稳定放大器将输入信号乘以一个方波,使带限输入频谱在斩波频率及其倍数周围移动[11]。该操作将信号从偏移量和1/f噪声中分离,输入谱如图1(b)所示,截断和添加失调电压VOS和1/f噪声vf(t)的vn(t)等,得到了图1(c)的频谱。经过第二个调制器后,频谱变成图1(d)。低通滤波器可以降低偏移量的振幅和1/f贡献[12]。

图1 斩波电路原理图与调制频谱图

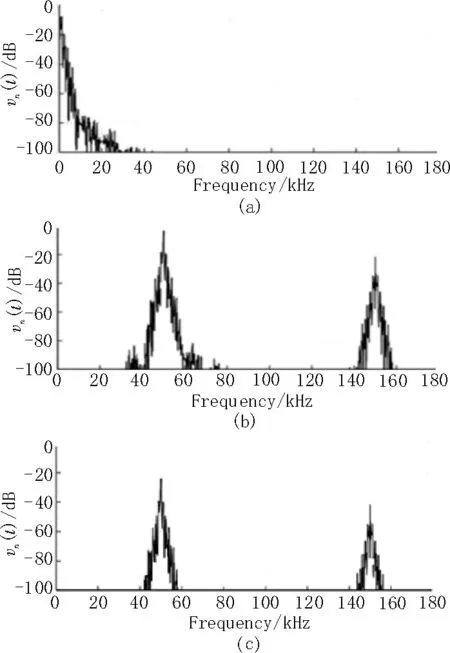

该方法已通过测试1/f噪声进行模拟,其频谱如图2(a)所示。经过spur 调制后的输出频谱如图2(b)所示,一阶低通滤波器经过fch/10 处的频谱如图2(c)所示。

图2 1/f噪声的频谱图

微调(trimming)也就是细调某个元件的值。因为带隙基准源的输出电压的绝对精度是电路中的一个重要指标,但是由于电路中工艺、温度等难以控制的因素,一般很难保证精确的电阻值,所以常常需要微调带隙基准源中的电阻值,以提高基准电压的精度。

2 带斩波调制及微调技术的多路低输出带隙基准源设计

该文设计的斩波电路由4 个传输门开关组成,它们在相位相差180°的两个时钟信号控制下,轮换打开与关闭,动态补偿失调引起的误差,提高了带隙的精度。设计的带隙基准如图3 所示,clkp 和clkn 是两个互为反相的方波时钟信号,开关管M1~M16 组成斩波电路,R1~R4和M1 组成一个RC低通滤波器。第一个斩波电路放在运算放大器输入对管的栅极,来调制输入信号[13]。在占空比为50%的时钟周期信号的控制下,前半个周期内,clkp 为低,clkn 为高,v1in 输入信号为inn,v2in 输入信号为inp;在后半个周期内,clkp 为低,clkn 为高,输入对将进行切换。第二个斩波电路放在运算放大器的负载电流镜CNA和CNB 的源 端。当clkp 为低、clkn 为 高 时,v1 接vp信号,v2 接vn 信号;当clkp 为高、clkn 为低时,v1 接vn 信号,v2 接vp 信号,实现了动态切换电流镜MOS管,消除了电流镜的噪声和失调,并对已经调制的信号进行了解调,随后输出端的滤波器将调制到的斩波频率的纹波滤掉,以提高输出电压的精度,同时由于MOS 管的沟道调制效应会导致带隙对电源明显的依赖性,带隙的核心电路还采用了Cascode 结构,利用了Cascode 对电源的屏蔽特性。

图3 运用微调和斩波技术的带隙基准

在数模混合电路中,除了基本的带隙基准电压外,还需要低于基本的带隙基准电压的其他电压值,因此高精度多输出带隙基准电路变得很重要,并被广泛应用。该设计通过串联电阻在输出端处实现了多路输出,这种多路输出电路结构比较容易实现,产生了8 种电压值依次降低的基准电压:400 mV、250 mV、200 mV、150 mV、115 mV、100 mV、75 mV、50 mV,满足了不同模块对各种基准电压的需求。同时还通过trim 对电阻值进行微调,进一步提高输出电压的精度,如图3 虚线椭圆框所示,其由R5~R7组成,电阻值比为4∶2∶1,通过3 个信号控制不同权重的电阻,形成8 个trim 档。

3 仿真结果分析与比较

基于SMIC 40 nm CMOS 工艺,通过Cadence 公司的Spectre 仿真工具对该设计进行了仿真分析。

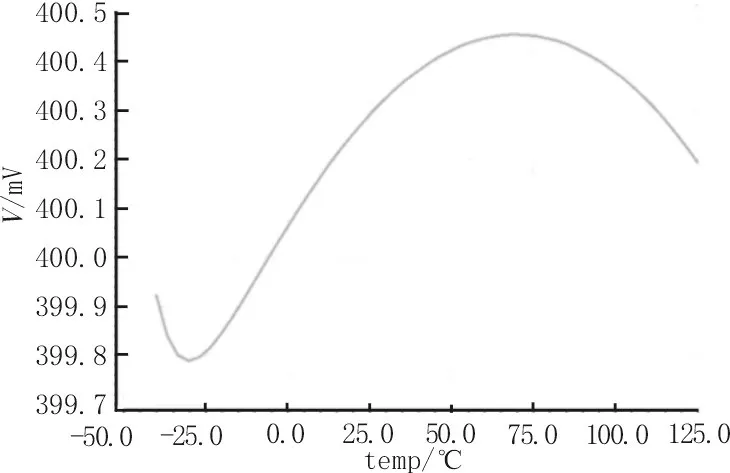

带斩波带隙基准源的输出电压的温度特性曲线如图4 所示,由图4 数据可计算得,当电源电压为2.5 V、温度范围为-40~125 °C 时,未加斩波的带隙基准的输出电压温度系数为50.12 ppm;而加了频率为2 MHz 的斩波后,带隙基准的输出电压温度系数为10.45 ppm。

图4 带斩波带隙基准源的输出电压的温度特性曲线

常温时,在TT corner 下,对基准电压随电源电压变化情况进行仿真,如图5所示,由图5数据可知,在电源电压为1.2~3.6 V 范围内,对整体电路进行了PSRR仿真,在低频段,PSRR 高达76.3 dB,性能比较稳定。

图5 输出电压随电源电压变化仿真图

当给输入对管和负载管分别加入±2%的误差时,对室温下的输出电压进行仿真,并与未加斩波的普通带隙的输出电压进行对比,如图6 所示,结果表明,普通带隙基准由于失调电压引起的最大误差达到25.23 mV,而加斩波调制的带隙基准由于失调电压引起的最大误差达到0.29 mV,相对精度提高了88 倍。

图6 加斩波的普通带隙与未加斩波的普通带隙的输出电压值对比

表1 为不 同corner 下,加trim 与未加trim 的基准电压值比较结果。仿真数据显示未加trim 的带隙基准源由于工艺等因素引起的最大误差达到8.56 mV,而加trim 的带隙基准源由于工艺等因素引起的最大误差达到1.53 mV,相对精度提高了5 倍。

表1 加trim与未加trim的基准电压值比较结果

该设计与其他设计的对比如表2 所示。该设计基于SMIC 40 nm CMOS 工艺在工作电压为2.5 V 的条件下,可以实现0.05~0.4 V 的多路低输出电压,加斩波的误差仅有±0.38%,温度系数为10.45 ppm,均优于其他设计。

表2 该设计与其他设计对比

4 结论

该文基于SMIC 40 nm CMOS 工艺设计了一款采用斩波调制和微调技术的多路低输出带隙基准源,有效地提高了输出电压的精度,大幅降低了其温度系数。在加入频率为2 MHz 的斩波后,带隙基准输出电压的温度系数达到10.45 ppm,与传统带隙基准相比,加入斩波后的输出电压精度提高了88 倍,且经过微调技术,精度又提高了5 倍。该电路实现的多路输出电压可应用于对各种基准电压的需求。